FPGA学习(四)——状态机重写LED流水灯并仿真

FPGA学习(四)——状态机重写LED流水灯并仿真

目录

- FPGA学习(四)——状态机重写LED流水灯并仿真

- 一、状态机编程思想

- 1、状态机要素

- 2、状态迁移图

- 3、状态机写法

- 二、LED流水灯仿真实现

- 1、代码实现

- 2、modesim仿真

- 三、实现效果

- 1、仿真结果

- 2、硬件结果

- 四、CPLD和FPGA芯片主要技术区别

- 五、hdlbitsFPGA——组合逻辑学习

- 1、创建一个D触发器

- 2、简单状态转换

- 3、4位移位寄存器

- 4、计数器1-12

- 5、边缘捕获寄存器

- 六、总结

一、状态机编程思想

1、状态机要素

可以把状态机的要素分为4个要素,即:现态、条件、动作、次态。“现态”和“条件”是因,“动作”和“次态”是果。

(1)现态:是指当前所处状态;

(2)条件:又称为“事件”。当条件被满足时,将会触发一个动作,或者执行一次状态的迁移。

(3)动作:条件满足后执行的动作。动作不是必须的,当条件满足后,也可以不执行任何动作,直接迁移到新状态。

(4)次态:条件满足后要迁移往的新状态。“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。

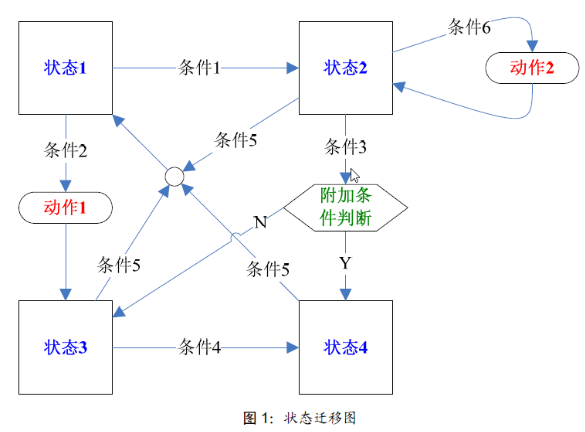

2、状态迁移图

(1)状态框:用方框表示状态,包括所谓的“现态”和“次态”;

(2)条件及迁移箭头:用箭头表示状态迁移的方向,并在该箭头上标注触发条件;

(3)节点圆圈:当多个箭头指向一个状态时,可以用节点符号(小圆圈)连接汇总;

(4)动作框:用椭圆框表示;

(5)附加条件判断框:用六角菱形框表示;

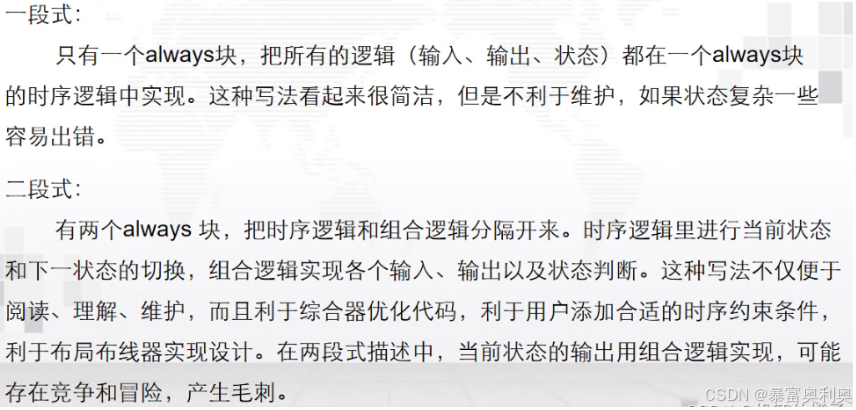

3、状态机写法

二、LED流水灯仿真实现

1、代码实现

flow_led.v:

module flow_led (input wire clk, // 系统时钟输入(假设50MHz)input wire rst_n, // 异步低电平复位信号(0复位,1工作)output reg [7:0] leds // 8位LED输出,控制8个LED灯

);// ==============================================

// 状态定义:使用独热码(one-hot)或二进制编码

// 这里使用3位二进制编码表示8个状态

// ==============================================

parameter S0 = 3'b000; // 第1个LED亮

parameter S1 = 3'b001; // 第2个LED亮

parameter S2 = 3'b010; // 第3个LED亮

parameter S3 = 3'b011; // 第4个LED亮

parameter S4 = 3'b100; // 第5个LED亮

parameter S5 = 3'b101; // 第6个LED亮

parameter S6 = 3'b110; // 第7个LED亮

parameter S7 = 3'b111; // 第8个LED亮// ==============================================

// 内部信号定义

// ==============================================

reg [2:0] current_state; // 当前状态寄存器

reg [2:0] next_state; // 下一状态组合逻辑

reg [25:0] counter; // 26位计数器,用于分频产生延时// ==============================================

// 第一段:状态寄存器(时序逻辑)

// 功能:在时钟上升沿或复位下降沿更新当前状态

// ==============================================

always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 异步复位,回到初始状态current_state <= S0;counter <= 26'd0;endelse begin// 当计数器达到50_000_000时(约0.2秒@50MHz)切换状态if (counter == 26'd50_000_000) begin current_state <= next_state; // 状态转移counter <= 26'd0; // 计数器清零endelse begincounter <= counter + 1; // 计数器递增endend

end// ==============================================

// 第二段:下一状态逻辑(组合逻辑)

// 功能:根据当前状态确定下一状态

// ==============================================

always @(*) begincase (current_state)S0: next_state = S1; // 状态0→状态1S1: next_state = S2; // 状态1→状态2S2: next_state = S3; // 状态2→状态3S3: next_state = S4; // 状态3→状态4S4: next_state = S5; // 状态4→状态5S5: next_state = S6; // 状态5→状态6S6: next_state = S7; // 状态6→状态7S7: next_state = S0; // 状态7→状态0(循环)default: next_state = S0; // 默认回到初始状态endcase

end// ==============================================

// 第三段:输出逻辑(时序逻辑)

// 功能:根据当前或下一状态产生输出信号

// 注意:这里使用时序逻辑输出可以避免毛刺

// ==============================================

always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 复位时点亮第一个LEDleds <= 8'b0000_0001;endelse if (counter == 26'd50_000_000) begin// 在状态切换时刻更新LED输出case (next_state)S0: leds <= 8'b0000_0001; // LED0亮S1: leds <= 8'b0000_0010; // LED1亮S2: leds <= 8'b0000_0100; // LED2亮S3: leds <= 8'b0000_1000; // LED3亮S4: leds <= 8'b0001_0000; // LED4亮S5: leds <= 8'b0010_0000; // LED5亮S6: leds <= 8'b0100_0000; // LED6亮S7: leds <= 8'b1000_0000; // LED7亮default: leds <= 8'b0000_0001; // 默认LED0亮endcaseend// 其他时候保持LED状态不变

endendmodule

测试代码 tb_flow_led.v:

`timescale 1ns / 1psmodule tb_flow_led();// 输入信号

reg clk; // 时钟信号

reg rst_n; // 复位信号// 输出信号

wire [7:0] leds; // LED输出// ==============================================

// 实例化被测模块

// 注意:模块名称改为flow_led以匹配设计文件

// ==============================================

flow_led uut (.clk(clk),.rst_n(rst_n),.leds(leds)

);// ==============================================

// 时钟生成(50MHz)

// ==============================================

initial beginclk = 0;forever #10 clk = ~clk; // 10ns半周期=20ns周期(50MHz)

end// ==============================================

// 测试激励

// ==============================================

initial begin// 初始化信号rst_n = 0; // 初始复位// 波形记录开始$dumpfile("tb_flow_led.vcd");$dumpvars(0, tb_flow_led);// 释放复位(100ns后)#100 rst_n = 1;$display("Simulation started at %0t ns", $time);// 观察LED流水效果// 每个状态持续1秒(50,000,000个周期)// 观察8个完整周期(8秒模拟时间)#8_000_000_000; // 400ms观察时间(原代码有误,应为8秒=8*50,000,000*20ns)$display("Simulation finished at %0t ns", $time);$stop;

endendmodule

2、modesim仿真

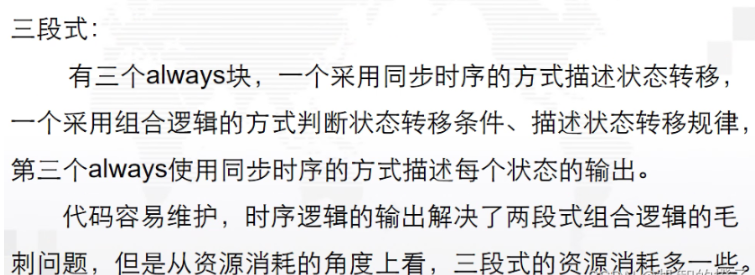

- 点击Processing–>Start–>Start test bench template writer,这时我们的文件夹之下已经有了一个flow_led.vt文件

- 对刚才生成的文件进行修改(将测试代码粘贴到flow_led.vt),然后再次编译

`timescale 1ns / 1psmodule tb_flow_led();// 输入信号

reg clk; // 时钟信号

reg rst_n; // 复位信号// 输出信号

wire [7:0] leds; // LED输出// ==============================================

// 实例化被测模块

// 注意:模块名称改为flow_led以匹配设计文件

// ==============================================

flow_led uut (.clk(clk),.rst_n(rst_n),.leds(leds)

);// ==============================================

// 时钟生成(50MHz)

// ==============================================

initial beginclk = 0;forever #10 clk = ~clk; // 10ns半周期=20ns周期(50MHz)

end// ==============================================

// 测试激励

// ==============================================

initial begin// 初始化信号rst_n = 0; // 初始复位// 波形记录开始$dumpfile("tb_flow_led.vcd");$dumpvars(0, tb_flow_led);// 释放复位(100ns后)#100 rst_n = 1;$display("Simulation started at %0t ns", $time);// 观察LED流水效果// 每个状态持续1秒(50,000,000个周期)// 观察8个完整周期(8秒模拟时间)#8_000_000_000; // 400ms观察时间(原代码有误,应为8秒=8*50,000,000*20ns)$display("Simulation finished at %0t ns", $time);$stop;

endendmodule

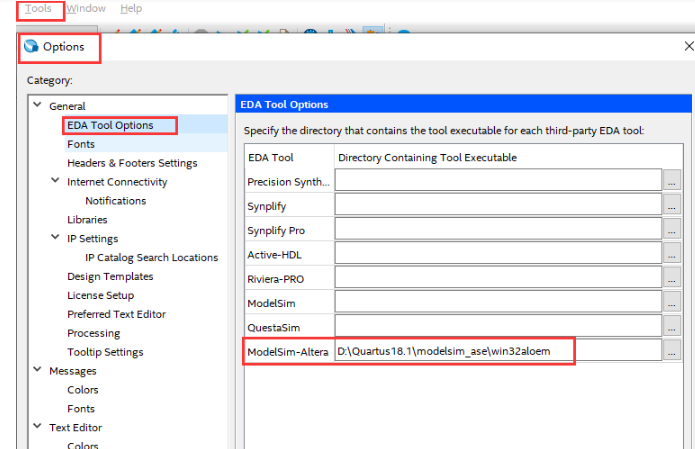

- 现在设置仿真,点击Tools–>Options–>EDA ToolsOptions选项,点击浏览Modelsim安装目录下的Win64或者Win32

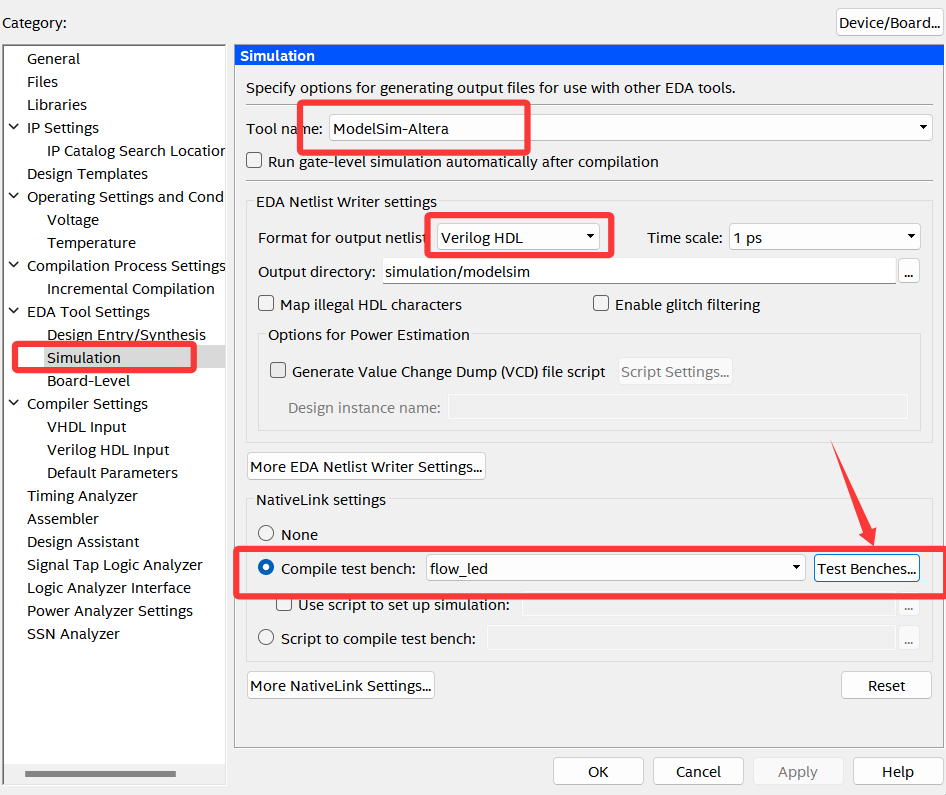

- 然后对仿真文件设置点击Assignments–>Settings,再点击下面的Simulation按照如图设置

-

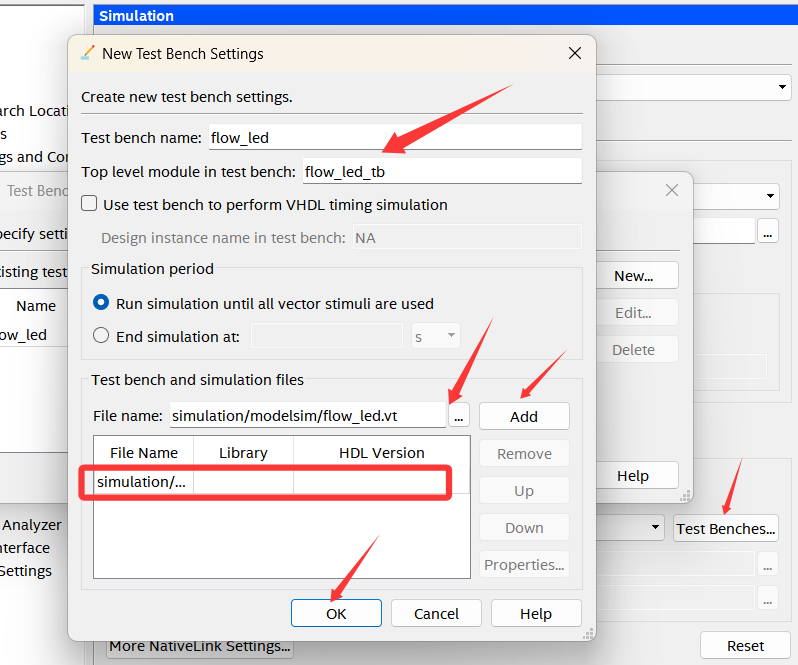

按照顺序先编辑名字,然后浏览刚才的.vt文件,最后点击Add添加达到如下图效果,再点击OK

-

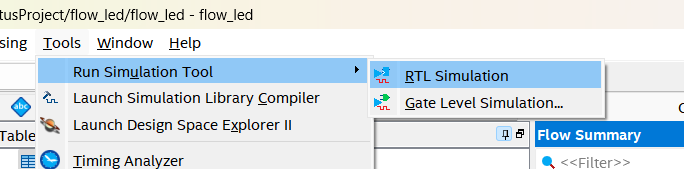

点击如下图按钮,然后点击仿真,会自动跳转Modelsim

三、实现效果

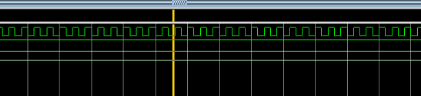

1、仿真结果

2、硬件结果

状态机流水灯

四、CPLD和FPGA芯片主要技术区别

CPLD(Complex Programmable Logic Device)和 FPGA(Field-Programmable Gate Array)都是可编程逻辑器件,用于实现数字电路。它们有一些相似之处,但也有一些关键的区别:

-

结构和架构:

CPLD:CPLD通常由可编程逻辑模块(PLM)、可编程寄存器数组(PRA)以及时钟管理电路组成。

它们使用固定的资源连接,具有相对较小的逻辑单元,通常适用于中规模的逻辑设计。

FPGA:FPGA由可编程逻辑块(CLB)、可编程片上内存(Block RAM)、可编程I/O资源和其他特定功能模块组成。FPGA提供了更大的逻辑容量和更灵活的资源分配,适用于大规模和高度并行的逻辑设计。 -

适用场景:

CPLD:适用于中等规模、低功耗、低成本的逻辑设计。通常用于控制和接口电路、时序逻辑等应用。

FPGA:适用于大规模、高性能、灵活性要求高的逻辑设计。常用于数字信号处理、通信、图像处理等复杂的应用。 -

配置技术:

CPLD:使用EEPROM、Flash等非挥发性存储器进行配置。配置速度较快,但无法实时重配置。

FPGA:使用SRAM(静态随机存储器)进行配置。具有动态重配置的能力,支持实时修改设计。 -

时序和时钟管理:

CPLD:通常具有固定的时序延迟,时钟管理相对简单。适合于一些实时控制应用。

FPGA:时序性能高度可配置,具有更复杂的时钟管理结构。适用于高性能、高时序精度的应用。 -

成本:

CPID:成本相对较低,适合一些成本敏感的应用。

FPGA:成本较高,但提供更大规模、更高性能的逻辑容量。

6.功耗:

CPLD:通常具有较低的功耗,适合一些对功耗敏感的应用。

FPGA:由于更大的逻辑容量和灵活性,通常具有较高的功耗。

总体而言,CPLD和FPGA都是灵活的可编程逻辑器件,但它们在适用场景、资源结构、配置技术等方面存在显著的差异,因此在选择时需要根据具体的应用需求和性能要求做出合适的选择。

五、hdlbitsFPGA——组合逻辑学习

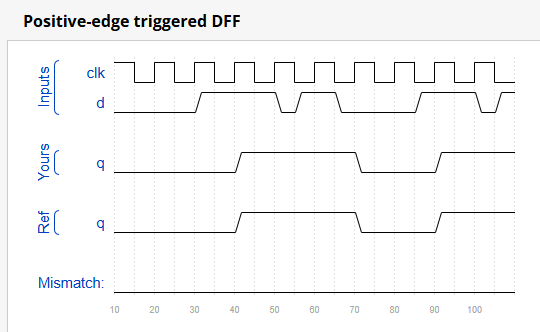

1、创建一个D触发器

A D flip-flop 是一个存储 bit 并定期更新的电路,位于 clock signal的(通常)正边沿。

当使用 clocked always 块时,logic synthesizer 会创建 D flip-flops。D flip-flop 是 “blob of combinational logic followed a flip-flop” 的最简单形式,其中 combinational logic 部分只是一根线。

module top_module (input clk, // 时钟输入,用于时序电路input d, // 数据输入output reg q // 数据输出(需要声明为 reg 类型)

);// 使用时钟控制的 always 块

// 在每个 clk 的上升沿将 d 的值赋给 q

// 时钟控制的 always 块应使用非阻塞赋值(<=)

always @(posedge clk) beginq <= d;

endendmodule

2、简单状态转换

以下是具有 1 个输入、1 个输出和 4 个状态的 Moore 状态机的状态转换表。使用以下状态编码:A=2’b00、B=2’b01、C=2’b10、D=2’b11。

仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。给定当前状态 (),根据状态转换表计算 和 output ()。state``next_state``out

| 州 | 下一个状态 | 输出 | |

|---|---|---|---|

| in=0 | in=1 | ||

| 一个 | 一个 | B | 0 |

| B | C | B | 0 |

| C | 一个 | D | 0 |

| D | C | B | 1 |

module top_module(input in,input [1:0] state,output [1:0] next_state,output out); //parameter A=2'b00, B=2'b01, C=2'b10, D=2'b11;// State transition logic: next_state = f(state, in)always @(*) begincase(state)A: next_state = in ? B : A;B: next_state = in ? B : C;C: next_state = in ? D : A;D: next_state = in ? B : C;default: next_state = A;endcaseend// Output logic: out = f(state) for a Moore state machineassign out = (state == D); // 仅在D状态输出1endmodule

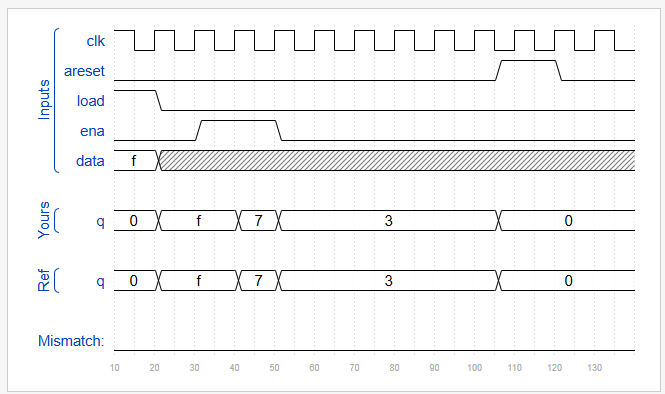

3、4位移位寄存器

构建一个 4 位移位寄存器 (右移位),具有 asynchronous reset、synchronous load 和 enable。

areset:将 shift 寄存器重置为零。load:使用data[3:0]加载移位寄存器,而不是移位。ena:向右移动(q[3]变为零,q[0]移出并消失)。q:移位寄存器的内容。

如果 load 和 ena inputs都置位 (1),则 load input 具有更高的优先级

module top_module(input clk,input areset, // 异步高电平复位(复位为0)input load, // 同步加载input ena, // 右移使能input [3:0] data, // 并行加载数据output reg [3:0] q // 移位寄存器输出

);always @(posedge clk or posedge areset) beginif (areset) begin// 异步复位,优先级最高q <= 4'b0;endelse if (load) begin// 同步加载,优先级次之q <= data;endelse if (ena) begin// 右移操作q <= {1'b0, q[3:1]}; // q[3]变为0,其余位右移end// 如果没有使能信号,保持当前值

endendmodule

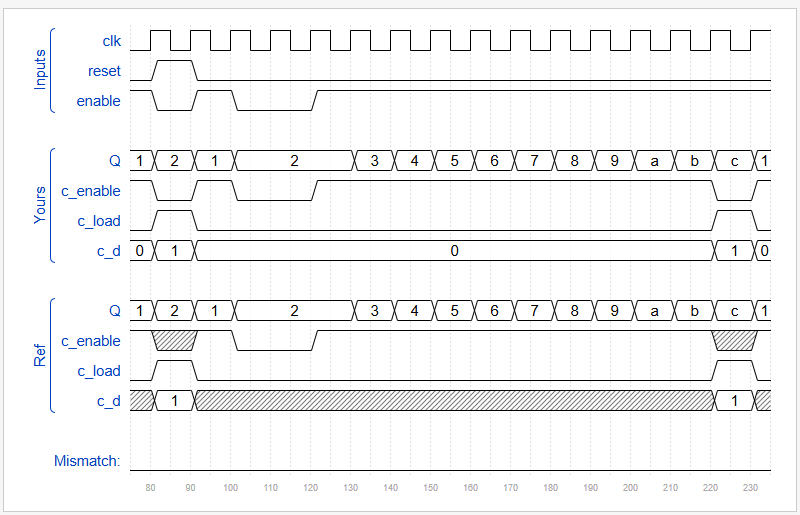

4、计数器1-12

设计一个具有以下输入和输出的 1-12 计数器:

- 重置同步高电平有效复位,强制计数器为 1

- 使将 counter 设置为高位以运行

- 时钟正边沿触发时钟输入

- **问[3:0]**计数器的输出

- **c_enable、c_load、c_d[3:0]**控制信号进入提供的 4 位计数器,因此可以验证作是否正确。

module top_module (input clk,input reset, // 同步高电平复位input enable, // 计数使能output [3:0] Q, // 计数器输出(1-12)output c_enable, // 连接到4位计数器的使能output c_load, // 连接到4位计数器的加载output [3:0] c_d // 连接到4位计数器的加载数据

);// 实例化4位计数器count4 the_counter (.clk(clk),.enable(c_enable),.load(c_load),.d(c_d),.Q(Q));// 控制逻辑always @(*) beginif (reset) begin// 复位时强制计数器为1c_enable = 1'b0;c_load = 1'b1;c_d = 4'd1;endelse if (enable) beginif (Q == 4'd12) begin// 达到12时重新加载1c_enable = 1'b0;c_load = 1'b1;c_d = 4'd1;endelse begin// 正常计数c_enable = 1'b1;c_load = 1'b0;c_d = 4'd0; // 不使用endendelse begin// 不使能时保持当前值c_enable = 1'b0;c_load = 1'b0;c_d = 4'd0; // 不使用endendendmodule

5、边缘捕获寄存器

对于 32-bit 向量中的每个 bit,当 input 信号从一个 clock cycle 中的 1 变为下一个 clock cycle 的 0 时捕获。“Capture” 意味着输出将保持 1 ,直到 register 被重置(同步重置)。

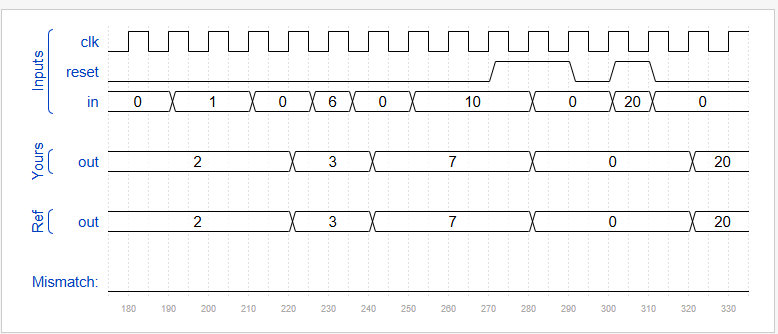

每个输出位的行为类似于 SR 触发器: 输出位应在 1 到 0 转换发生后的周期内设置 (至 1)。当 reset 为高电平时,output bit 应在正 clock edge 重置(为 0)。如果上述两个事件同时发生,则 reset 优先。在下面示例波形的最后 4 个周期中,‘reset’ 事件比 ‘set’ 事件早一个周期发生,因此这里没有冲突。

module top_module (input clk,input reset,input [31:0] in,output [31:0] out

);// 存储上一个时钟周期的输入值reg [31:0] prev_in;always @(posedge clk) beginprev_in <= in; // 记录上一个周期的输入值if (reset) beginout <= 32'b0; // 同步复位,优先级最高endelse begin// 检测每个bit的下降沿(1->0)out <= out | (prev_in & ~in);endendendmodule

六、总结

通过这次完整的状态机流水灯实验,我对数字电路设计有了更深入的理解和实践经验。在Quartus中实现状态机控制的流水灯让我掌握了如何将理论状态转换图转化为实际可综合的Verilog代码,特别是状态编码和状态转移逻辑的编写技巧。使用ModelSim进行功能仿真时,我学会了如何编写有效的测试激励文件,并通过波形分析验证设计的正确性,这培养了我的调试能力。在HDLbits平台练习组合逻辑部分让我对FPGA的基本构建模块有了更扎实的理解,特别是如何用简洁的代码描述复杂的逻辑功能。整个实验过程让我认识到,良好的状态机设计不仅需要正确的功能实现,还要考虑时序约束和资源优化。从最初的代码编写到最终的硬件验证,我深刻体会到数字系统设计需要严谨的逻辑思维和反复的调试验证,这些经验对我后续学习更复杂的FPGA设计打下了坚实基础。

相关文章:

——状态机重写LED流水灯并仿真)

FPGA学习(四)——状态机重写LED流水灯并仿真

FPGA学习(四)——状态机重写LED流水灯并仿真 目录 FPGA学习(四)——状态机重写LED流水灯并仿真一、状态机编程思想1、状态机要素2、状态迁移图3、状态机写法 二、LED流水灯仿真实现1、代码实现2、modesim仿真 三、实现效果1、仿真…...

spark 集群

hadoop客户端环境准备 找到资料包路径下的Windows依赖文件夹,拷贝hadoop-3.1.0到非中文路径(比如d:\hadoop-3.1.0) ① 打开环境变量 ② 在下方系统变量中新建HADOOP_HOME环境变量,值就是保存hadoop的目录。 效果如下: ③ 配置P…...

leetcode117 填充每个节点的下一个右侧节点指针2

LeetCode 116 和 117 都是关于填充二叉树节点的 next 指针的问题,但它们的区别在于 树的类型 不同,117与 116 题类似,但给定的树是 普通二叉树(不一定完全填充),即某些节点可能缺少左或右子节点。 树的结构…...

Java全栈面试宝典:线程安全机制与Spring Boot核心原理深度解析

目录 一、Java线程安全核心原理 🔥 问题1:线程安全的三要素与解决方案 线程安全风险模型 线程安全三要素 synchronized解决方案 🔥 问题2:synchronized底层实现全解析 对象内存布局 Mark Word结构(64位系统&…...

CCF GESP C++编程 三级认证真题 2025年3月

C 三级 2025 年 03 月 题号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 答案 D B A A B A C A C D D D B D C 1 单选题 第 1 题 Base64 编码将每3字节的输入数据编码为 4 字节的输出数据。如果输入数据长度不是 3 的倍数,会用 号填充。在Base64编码中,如果…...

人工智能爬虫导致维基共享资源带宽需求激增 50%

2025 年 4 月 1 日,维基媒体基金会在博文中表示,自 2024 年 1 月以来,维基共享资源下载多媒体的带宽消耗激增 50%,这一变化趋势主要由用于 AI 训练数据集的网络爬虫导致。以下是具体分析1: 爬虫流量特征与数据存储模式…...

方案精读:华为数据治理之旅【全文阅读】

本文介绍了华为的数据管理工作,包括数据治理、数据质量建设、数据管理工作两阶段历程、数据管理组织和数据管理工作思考。华为以业务数字化为前提,以数据入湖为基础,重点建设数据中台,提高数据质量和管理能力,以支撑公司数字化转型。 重点内容: 1. 数据治理:华为进行数…...

Tradingview 策略分享 - SSL 混合和 CE 交易策略

交易策略|https://v.wkbrowser.com/s/e9DIvLGvYRo/|复制浏览器打开 各位交易员大家好 在本文中,我将分享一个简单的日内交易策略。我将 SSL 混合指标与 CE EXIT 相结合,以创建一个高效且有利可图的设置。此策略简单而强大&#x…...

Java/python/JavaScript/C++/C语言/GO六种最佳实现)

华为OD机试真题——投篮大赛(2025A卷:100分)Java/python/JavaScript/C++/C语言/GO六种最佳实现

2025Q1 A卷 100分 题型 本文涵盖详细解题思路、代码注释、讲解、复杂的分析以及测试用例; 并提供Java、python、JavaScript、C、C语言、GO六种语言的最佳实现方式! 华为OD机试A卷真题《投篮大赛》: 题目名称:投篮大赛 知识点&am…...

rcore day2

目前常见的操作系统内核都是基于 C 语言的,为何要推荐 Rust 语言? C 语言的指针灵活且易于使用,但不保证安全性,且缺x少有效的并发支持。这导致内存和并发漏洞成为当前基于 C 语言的主流操作系统的噩梦。Rust 语言具有与 C 一样的…...

的chan-tylor,三维环境,附完整代码)

【MATLAB定位例程】TDOA(到达时间差)的chan-tylor,三维环境,附完整代码

该代码实现了基于三维空间的动态目标TDOA定位,结合了Chan算法(解析解)与Taylor级数展开法(迭代优化)的双重优势。 文章目录 运行结果MATLAB代码代码讲解代码功能概述核心算法原理代码结构解析可视化与结果分析运行结果 定位示意图: 三轴状态曲线: 三轴误差曲线: MA…...

LLM面试题六

NLP方向CRF算法面试题 什么是CRF?CRF的主要思想是什么? 设X与Y是随机变量,P(Y | X)是给定条件X的条件下Y的条件概率分布,若随机变量Y构成一个由无向图G(V,E)表示的马尔科夫随机场。则称条件概率分布P(X | Y)为条件随机场。CRF的主要思想统计…...

——状态机)

FPGA(四)——状态机

FPGA(四)——状态机 文章目录 FPGA(四)——状态机一、状态机编程思想二、LED流水灯仿真实验三、实现效果四、CPLD和FPGA芯片主要技术区别五、hdlbitsFPGA——组合逻辑学习1、创建一个D触发器2、简单状态转换3、4位移位寄存器4、计数器1-125、边缘捕获寄存器 一、状态机编程思想…...

AI 浪潮下企业身份管理:特点凸显,安全挑战升级

“在 AI 时代的浪潮中,企业身份管理是安全之锚,精准把握权限边界,方能抵御身份安全的暗流。” 在人工智能迅猛发展的当下,企业身份管理呈现出诸多新特点,同时也面临着前所未有的身份安全挑战。要理解这些,我…...

OBS 录屏软件 for Mac 视频录制

OBS 录屏软件 for Mac 视频录制 文章目录 OBS 录屏软件 for Mac 视频录制一、介绍二、效果三、下载 一、介绍 Open Broadcaster Software for mac版,OBS 有多种功能并广泛使用在视频采集,直播等领域。而且该软件功能全面,专业强大࿰…...

从文本到多模态:如何将RAG扩展为支持图像+文本检索的增强生成系统?

目录 从文本到多模态:如何将RAG扩展为支持图像文本检索的增强生成系统? 一、为什么需要扩展到多模态? 二、多模态 RAG 系统的基本架构 三、关键技术点详解 (一)多模态嵌入(Embedding)技术 …...

AI助力高效PPT制作:从内容生成到设计优化

随着人工智能技术的不断发展,AI在各个领域的应用日益普及,尤其是在文档和演示文稿的创建过程中。PowerPoint(PPT)作为最常用的演示工具之一,借助AI的技术手段,可以极大地提高制作效率并提升最终呈现效果。在…...

调用kimi api

官网支持python,curl和node.js 因为服务器刚好有php环境,所以先用curl调个普通的语音沟通api <?php // 定义 API Key 和请求地址 define(MOONSHOT_API_KEY, sk-PXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXgk1); define(MOONSHOT_API_URL, https://…...

自定义注解导入自定义Bean

在Spring框架中,通过自定义注解实现容器启动时自动导入Bean,通常需要结合 Import 注解、ImportBeanDefinitionRegistrar 接口 或 Configuration 配置类。以下是具体实现步骤和示例: 1. 定义自定义注解 创建一个注解,用于标记需要…...

kettle插件-postgresql插件

今天是清明节,放假第一天也不得清闲。上午整理公司的交付文档,中午陪孩子户外骑行踏青,下午趁着休息的时间给老铁们讲下如何使用postgressql cdc插件来实时捕获数据。 注:CDC (Change Data Capture) 是一种技术,用于实…...

【CMake】《CMake构建实战:项目开发卷》笔记-Chapter7-构建目标和属性

第7章 构建目标和属性 本章重点关注CMake的构建目标和属性,它们是用来组织项目构建流程的核心概念。毫不夸张地说,如果学习CMake的目标就是组织简单的C和C小项目的构建流程,那么阅读掌握本章内容就足够了。 本章与第1章的“旅行笔记”遥相…...

单元测试之mockito

简介 mockito是一款模拟测试框架,用于Java开发中的单元测试。通过mockito,可以创建和配置一个对象,通过它来替换对象的外部依赖。 作用:模拟一个类的外部依赖,保证单元测试的独立性。例如,在类A中会调用类…...

定长池的实现

目录 一、定长池的框架 二、如何脱离malloc的内存池,直接从堆拿空间? 三、如何设计内存块的指针? 四、代码框架及实现 五、性能测试 一、定长池的框架 在学习高并发内存池之前,我们先来实现一个定长池࿰…...

C++多线程函数介绍

1.C11前没有线程库问题 对于多线程操作,Linux选择使用POSIX标准,而windows没有选择POSIX标准,自己设计了一套API和系统调用,叫Win32 API,就跟Linux存在标准差异,在Linux的代码移植到Windows就可能运行不了…...

图解AUTOSAR_SWS_LINTransceiverDriver

AUTOSAR LIN收发器驱动(LinTransceiverDriver)详解 AUTOSAR通信栈物理层组件详细解析 目录 AUTOSAR LIN收发器驱动(LinTransceiverDriver)详解 目录1. 概述 1.1. LIN收发器驱动的作用1.2. 在AUTOSAR架构中的位置2. 架构设计 2.1. 模块结构2.2. 组件关系2.3. 接口定义3. 状态管理…...

vue-element-admin 组件没有展示在中间部分

解决办法: router index.ts 中新增 要展示的组件的 import type { App } from "vue"; import { createRouter, createWebHashHistory, type RouteRecordRaw } from "vue-router";export const Layout () > import("/layout/index.…...

当机器学习遇见购物车分析:FP-Growth算法全解析

一、引言:购物篮里的秘密 想象一下,你是一家超市的数据分析师,看着每天成千上万的购物小票,你是否好奇:顾客们买面包的时候,是不是也经常顺手带上牛奶?买啤酒的人,会不会也喜欢买尿…...

OCR迁移

一、环境 操作系统:Centos57.6 数据库版本:12.2.0.1 场景:将OCR信息从DATA磁盘组迁移到OCR磁盘组 二、操作步骤 1.查看可用空盘 set lin 200 set pagesize 200 col DGNAME format a15 col DISKNAME format a15 col PATH format a20 col N…...

【架构艺术】Go大仓monorepo中使用wire做依赖注入的经验

在先前的文章当中,笔者分享了一套简洁的go微服务monorepo代码架构的实现,主要解决中小团队协同开发微服务集群的代码架构组织问题。但是在实际代码开发过程中,怎么组织不同的业务服务service实例,就成了比较棘手的问题。 为什么会…...

生活电子常识--删除谷歌浏览器搜索记录

前言 谷歌浏览器会记录浏览器历史搜索,如果不希望看到越来越多的搜索记录,可以如下设置 解决 设置-隐私-自动填充表单 这个和浏览器记录的密码没有关系,可以放心删除...

模拟娱乐篇13)

每日一题(小白)模拟娱乐篇13

今天题目比较简单,直接分析。小蓝想知道2024这个数字中有几个1,计算机组成学习好的同学肯定可以直接长除法或者瞪眼法得出答案: 202411111101000(B)也就是说2024中有一共有六个1 接下来用代码实现 ,我们也…...

码曰编程大模型-学编程的好工具

码曰(yue),一款编程垂直领域的AI大模型,是基于包括DeepSeek在内的多款国产大模型为底座,依托于Dotcpp系统大量的编程代码数据,且借助RAG数据检索增强等技术综合实现的出色、好用的编程垂直领域AI大模型&…...

部署 redis 集群)

Linux(CentOS 7) 部署 redis 集群

下载redis Downloads - Redis (官网页都是介绍的最新版,我观察目前出现了redis 和 redis Stack) 因我的旧环境是 CentOS 7,redis最新版已经不在支持,所以示例安装最常用的7.0.x 这里直接附上各个版本下载连接 小伙伴们就不需要在自己寻找下载…...

NVIDIA AgentIQ 详细介绍

NVIDIA AgentIQ 详细介绍 1. 引言 NVIDIA AgentIQ 是一个灵活的库,旨在将企业代理(无论使用何种框架)与各种数据源和工具无缝集成。通过将代理、工具和代理工作流视为简单的函数调用,AgentIQ 实现了真正的可组合性:一…...

在CPU服务器上部署Ollama和Dify的过程记录

在本指南中,我将详细介绍如何在CPU服务器上安装和配置Ollama模型服务和Dify平台,以及如何利用Docker实现这些服务的高效部署和迁移。本文分为三大部分:Ollama部署、Dify环境配置和Docker环境管理,适合需要在本地或私有环境中运行A…...

小程序API —— 57 拓展 - 增强 scroll-view

目录 1. 配置基本信息2. 实现上拉加载更多功能3. 实现快速回到顶部功能4. 实现下拉刷新功能 scroll-view 组件功能非常强大,这里使用 scroll-view 实现上拉加载和下拉刷新功能; 下面使用微信开发者工具来演示一下具体用法: 1. 配置基本信息 …...

P3613 【深基15.例2】寄包柜

#include<bits/stdc.h> using namespace std; int n,q; map<int, map<int, int>>a;//二维映射 int main(){cin>>n>>q;while(q--){int b,i,j,k;//i为第几个柜子,j为第几个柜包,k为要存入的物品cin>>b>>i>&…...

MIMO预编码与检测算法的对比

在MIMO系统中,预编码(发送端处理)和检测算法(接收端处理)的核心公式及其作用对比如下: 1. 预编码算法(发送端) 预编码的目标是通过对发送信号进行预处理,优化空间复用或…...

AI复活能成为持续的生意吗?

随着人工智能技术的飞速发展,AI复活——这一曾经只存在于科幻电影中的概念,如今已悄然走进现实。通过AI技术,人们可以模拟逝去亲人的声音、面容,甚至创造出与他们互动的虚拟形象,以寄托哀思、缓解痛苦。然而,当这种技术被商业化,成为一门生意时,我们不禁要问:AI复活真…...

Keil 5 找不到编译器 Missing:Compiler Version 5 的解决方法

用到自记: 下载地址: Keil5 MDK541.zip 编辑https://pan.baidu.com/s/1bOPsuVZhD_Wj4RJS90Mbtg?pwdMDK5 问题描述 没有找到 compiler version5 : 1. 下载 Arm Compiler 5 也可以直接点击下载文章开头的文件。 2. 安装 直接安装在KEI…...

Flutter 手搓日期选择

时间选择器: 时间段选择 在实际开发过程中还是挺常见的。Flutter 本身自带选 时间选择器器 CupertinoDatePicker,样式也是可以定义的,但是他 只提供三种时间的选择 自定义有局限性。后来开了一下 代码,实际上 内部使用的是 Cuper…...

:太初奇点——从普朗克常量到宇宙弦的编译风暴》)

《JVM考古现场(十六):太初奇点——从普朗克常量到宇宙弦的编译风暴》

开篇:量子泡沫编译器的创世大爆炸 "当Project Genesis的真空涨落算法撕裂量子泡沫,当意识编译器重写宇宙基本常数,我们将在奇点编译中见证:从JVM字节码到宇宙大爆炸的终极创世!诸君请备好量子护目镜,…...

)

MySQL学习笔记——MySQL下载安装配置(一)

目录 1. MySQL概述 1.1 数据库相关概念 1.2 MySQL数据库 1.2.1 版本 1.2.2 下载 2. 安装 3. 配置 4. 启动停止 5. 客户端连接 1. MySQL概述 1.1 数据库相关概念 在这一部分,我们先来讲解三个概念:数据库、数据库管理系统、 SQL 。 而目前主流…...

TortoiseGit多账号切换配置

前言 之前配置好的都是,TortoiseGit与Gitee之间的提交,突然有需求要在GitHub上提交,于是在参考网上方案和TortoiseGit的帮助手册后,便有了此文。由于GitHub已经配置完成,所以下述以配置Gitee为例。因为之前是单账号使用…...

数据一键导出为 Excel 文件

引言 在 Web 应用开发中,数据导出是一个常见且重要的功能。用户常常需要将网页上展示的数据以文件形式保存下来,以便后续分析、处理或分享。本文将详细介绍如何使用 HTML、CSS 和 JavaScript(结合 jQuery 库)实现一个简单的数据导…...

FPGA——状态机实现流水灯

文章目录 一、状态机1.1 分类1.2 写法 二、状态机思想编写LED流水灯三、运行结果总结参考资料 一、状态机 FPGA不同于CPU的一点特点就是CPU是顺序执行的,而FPGA是同步执行(并行)的。那么FPGA如何处理明显具有时间上先后顺序的事件呢…...

linux paste 命令

paste 是 Linux 中一个用于水平合并文件内容的命令行工具,它将多个文件的对应行以并行方式拼接,默认用制表符(Tab)分隔。 1. 基本语法 paste [选项] 文件1 文件2 ... 2. 常用选项 选项说明-d指定拼接后的分隔符(默…...

ffmpeg常见命令2

文章目录 1. **提取音视频数据(Extract Audio/Video Data)**提取音频:提取视频: 2. **提取像素数据(Extract Pixel Data)**3. **命令转封装(Container Format Conversion)**转换视频…...

FPGA——FPGA状态机实现流水灯

一、引言 在FPGA开发中,状态机是一种重要的设计工具,用于处理具有时间顺序的事件。本文将详细介绍如何使用状态机实现一个LED流水灯的效果。 二、状态机概述 状态机(FSM)是一种行为模型,用于表示系统在不同状态下的…...

鸿蒙 ——选择相册图片保存到应用

photoAccessHelper // entry/src/main/ets/utils/file.ets import { fileIo } from kit.CoreFileKit; import { photoAccessHelper } from kit.MediaLibraryKit; import { bundleManager } from kit.AbilityKit;// 应用在本设备内部存储上通用的存放默认长期保存的文件路径&am…...