FPGA_UART

1.UART 概述 (通用异步收发传输器)

1. 基本定义

UART(Universal Asynchronous Receiver/Transmitter)是一种常见的串行通信协议,用于在设备间通过异步串行通信传输数据。它不依赖独立的时钟信号,而是通过预定义的波特率(Baud Rate) 同步数据的收发。 核心特点:

- 异步通信:无需共享时钟信号,仅通过数据线传输。

- 全双工模式:收发双方可同时发送和接收数据(需独立TX、RX线)。

- 灵活配置:支持自定义波特率、数据位长度、校验位、停止位等。

2. 工作原理

(1) 数据传输格式

每一帧数据包含以下部分(以典型8N1格式为例):

| 起始位 | 数据位(8位) | 校验位(可选) | 停止位(1位) |

|---|---|---|---|

1位,低电平 | LSB先发 | 奇偶校验(可选) | 1位,高电平 |

- 起始位:低电平(0)表示数据传输开始。

- 数据位:传输的有效数据(5~9位),通常低位(LSB)先发送(如用户之前的案例)。

- 校验位:用于简单错误检测(奇校验/偶校验/无校验)。

- 停止位:高电平(1)表示一帧数据结束,并允许接收端校准时序。

(2) 异步同步机制

- 波特率校准:收发双方必须使用相同的波特率(如115200、9600)。 例如:

复制

波特率115200 → 每位持续时间 ≈ 1/115200 ≈ 8.68μs

- 数据采样:接收端在起始位下降沿触发,并在数据位中间点采样,抵消时钟偏移影响。

3. 典型应用场景

- 微控制器与外围模块通信:如ESP8266(Wi-Fi)、GPS模块、传感器(温湿度)。

- 调试接口:通过UART输出调试信息(常见于嵌入式开发板)。

- 有线设备互联:旧式打印机、工业设备(如Modbus RTU协议)。

- 信号转换:结合电平转换芯片(如MAX232)实现RS232、RS485等长距离通信。

4. 优缺点分析

| 优点 | 缺点 |

|---|---|

| 硬件简单(仅需两根数据线) | 传输距离短(通常<1米) |

| 成本低(无需复杂协议栈) | 无硬件错误恢复机制(需软件纠错) |

| 广泛兼容性(几乎所有MCU支持) | 需严格匹配波特率(误差<3%) |

5. 硬件实现关键点

- 发送端(TX):

- 将并行数据转为串行,按波特率逐位发送。

- 使用分频器生成波特率时钟(如50MHz主频 → 115200波特率需分频系数:50e6 / 115200 ≈ 434)。

- 接收端(RX):

- 检测起始位下降沿,启动同步采样。

- 通过移位寄存器重组串行数据为并行数据。

6. 常见问题与解决方案

- 波特率失配: 若收发波特率差超过3%,会导致采样偏移,需重新校准。

- 电磁干扰: 长距离使用需加屏蔽线或转换为差分信号(如RS485)。

- 数据冲突: 全双工通信需避免同时发送,可通过流控信号(RTS/CTS)解决。

7. 主流扩展协议

- RS-232:电平标准(±3~15V),支持更长距离(<15米)。

- RS-485:差分信号,可多点通信(工业现场总线)。

- USB转UART:通过芯片(如CH340、CP2102)实现USB与串口无缝衔接。

2.verilog编写

这里需要讲解下,这里使用到50mhz的时钟, 波特率为115200,这里的50mhz的时钟是在1秒内有50_000_000个周期的数据,波特率115200是在1秒内有115200bit的传输。

50_000_000/115200 指的是传输1bit需要传输多少个时钟周期

在写测试代码的时候,#8680 是因为 在 50_000_000/115200= 434 个时钟周期传输1bit, 而434个时钟周期每个时钟周期为20ns 434*20= 8680.

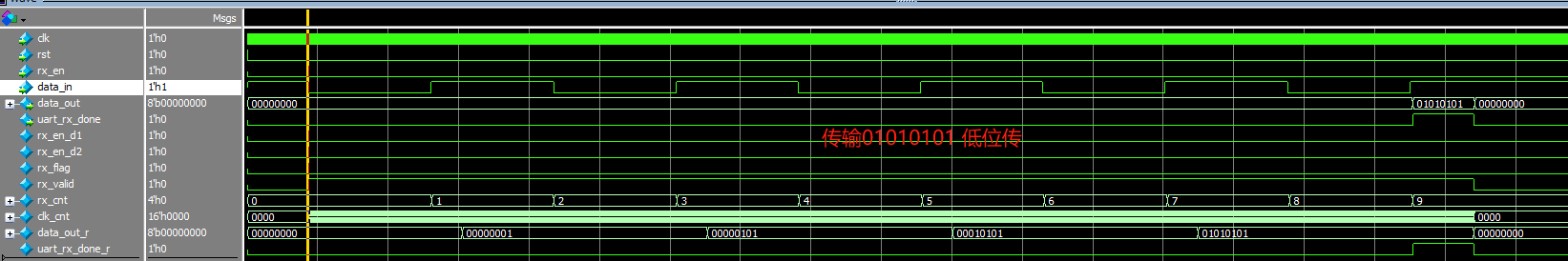

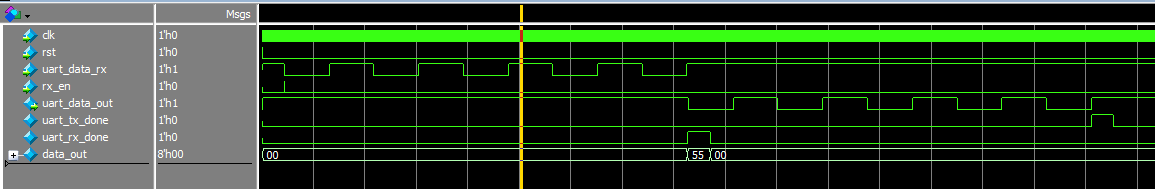

1,波形图

接收和发送都根据这个图编写就行

2.1接收模块代码

module uart_rx (

input clk,

input rst,

input rx_en,

input data_in,

output reg [7:0] data_out,

output uart_rx_done

);localparam CLK = 50_000_000,BOTE = 115200,CNT = CLK / BOTE ;reg rx_en_d1;

reg rx_en_d2;

reg rx_flag ;

reg rx_valid;

reg [3:0] rx_cnt ;

reg [15:0] clk_cnt ;

reg [7:0] data_out_r;

reg uart_rx_done_r;assign uart_rx_done = uart_rx_done_r;always @(posedge clk or negedge rst )beginif (rst == 1'b1)beginrx_en_d1 <= 1'b0;rx_en_d2 <= 1'b0;endelse beginrx_en_d1 <= rx_en;rx_en_d2 <= rx_en_d1;end

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)rx_flag <= 1'b0;else if (rx_en_d1 == 1'b1 && rx_en_d2 == 1'b0)rx_flag <= 1'b1;else rx_flag <= 1'b0;

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)rx_valid <= 1'b0;else if (rx_cnt == 4'd9 && clk_cnt == CNT /2 )rx_valid <= 1'b0;else if (rx_flag == 1'b1)rx_valid <= 1'b1;else;

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)clk_cnt <= 16'd0;else if (clk_cnt == CNT )clk_cnt <= 16'd0;else if (rx_valid == 1'b1)clk_cnt <= clk_cnt +1'b1;else clk_cnt <= 16'd0;

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)rx_cnt <= 4'd0;else if (rx_en_d1 == 1'b1 && rx_en_d2 == 1'b0)rx_cnt <= 4'd0;else if (clk_cnt == CNT) rx_cnt <= rx_cnt +1'b1;else;

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)uart_rx_done_r <= 1'b0;else if (rx_valid == 1'b1) beginif (rx_cnt == 4'd9)uart_rx_done_r <= 1'b1;else uart_rx_done_r <= 4'd0;endelseuart_rx_done_r <= 1'b0;

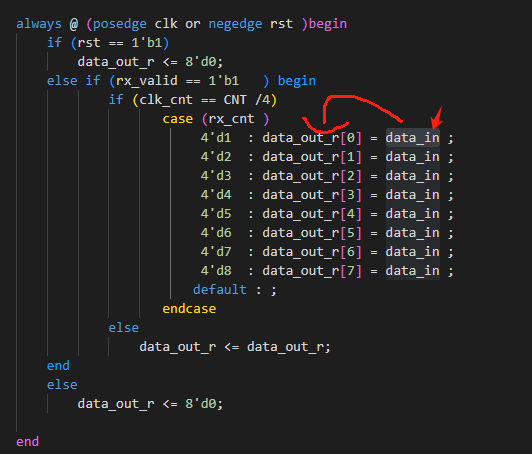

endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)data_out_r <= 8'd0;else if (rx_valid == 1'b1 ) beginif (clk_cnt == CNT /4) case (rx_cnt )4'd1 : data_out_r[0] = data_in ; 4'd2 : data_out_r[1] = data_in ; 4'd3 : data_out_r[2] = data_in ; 4'd4 : data_out_r[3] = data_in ; 4'd5 : data_out_r[4] = data_in ; 4'd6 : data_out_r[5] = data_in ; 4'd7 : data_out_r[6] = data_in ; 4'd8 : data_out_r[7] = data_in ; default : ;endcaseelse data_out_r <= data_out_r;endelse data_out_r <= 8'd0; endalways @ (posedge clk or negedge rst )beginif (rst == 1'b1)data_out <= 8'd0;else if (rx_cnt == 4'd9)data_out <= data_out_r;else data_out <= 8'd0;

endendmodule 2.2发送模块代码

module uart_tx(

input clk,

input rst,input tx_en,

input [7:0] data_din,

output data_out,

output uart_tx_done );

localparam CLK = 50_000_000, //时钟 50_000_000 一秒 50000000个时钟周期 数据 波特率 9600 一秒9600个数据bit 5000000/9600 一个bit需要多少时钟周期 BOTE =115200, CNT = CLK /BOTE ;reg tx_en_d1;

reg tx_en_d2;

reg start_flag;

reg tx_valid;

reg [3:0] tx_cnt;

reg [15:0] clk_cnt;

reg uart_done_r;

reg uart_dout_r;

reg [7:0] data_din_r;assign data_out = uart_dout_r;

assign uart_tx_done = uart_done_r;always @ (posedge clk or negedge rst) beginif (rst == 1'b1) begintx_en_d1 <= 1'b0;tx_en_d2 <= 1'b0;endelse begintx_en_d1 <=tx_en;tx_en_d2 <= tx_en_d1;end

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)data_din_r <= 8'd0;else if (tx_cnt ==4'd9 && clk_cnt == CNT /2)data_din_r <= 8'd0;else if ( tx_en_d1 == 1'b1 && tx_en_d2 == 1'b0 ) data_din_r <= data_din;else;

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)start_flag <= 1'b0;else if ( tx_en_d1 == 1'b1 && tx_en_d2 == 1'b0 ) start_flag <= 1'b1;else start_flag <= 1'b0;

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)tx_valid <= 1'b0;else if (start_flag == 1'b1)tx_valid <= 1'b1;else if (tx_cnt ==4'd9 && clk_cnt == CNT /2 )tx_valid <= 1'b0;else;

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)clk_cnt <= 16'd0;else if (clk_cnt == CNT )clk_cnt <= 16'd0;else if (tx_valid == 1'b1)clk_cnt <= clk_cnt +1'b1;else clk_cnt <= 16'd0;

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)tx_cnt <= 4'd0;else if (tx_en_d1 == 1'b1 && tx_en_d2 == 1'b0)tx_cnt <= 4'd0;else if (clk_cnt == CNT)tx_cnt <= tx_cnt +1'b1;else;

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)uart_done_r <= 1'b0;else if (tx_valid == 1'b1) beginif (tx_cnt == 4'd9) uart_done_r <= 1'b1;elseuart_done_r <= 1'b0; endelseuart_done_r <= 1'b0;

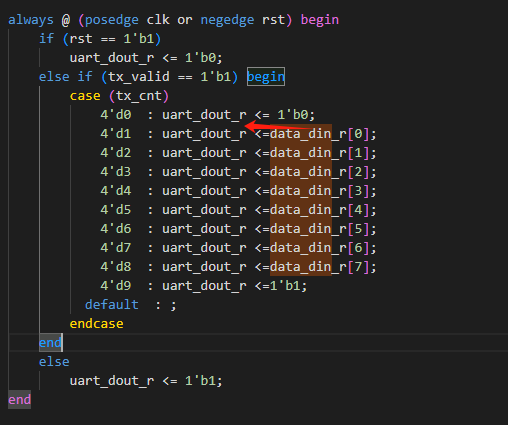

endalways @ (posedge clk or negedge rst) beginif (rst == 1'b1)uart_dout_r <= 1'b0; else if (tx_valid == 1'b1) begincase (tx_cnt)4'd0 : uart_dout_r <= 1'b0;4'd1 : uart_dout_r <=data_din_r[0]; 4'd2 : uart_dout_r <=data_din_r[1];4'd3 : uart_dout_r <=data_din_r[2];4'd4 : uart_dout_r <=data_din_r[3];4'd5 : uart_dout_r <=data_din_r[4];4'd6 : uart_dout_r <=data_din_r[5];4'd7 : uart_dout_r <=data_din_r[6];4'd8 : uart_dout_r <=data_din_r[7]; 4'd9 : uart_dout_r <=1'b1;default : ;endcaseendelseuart_dout_r <= 1'b1;

endendmodule 2.3顶层模块代码

module uart_top (

input clk,

input rst,

input uart_data_rx,

input rx_en,

output uart_data_out

);wire uart_tx_done;

wire uart_rx_done;

wire [7:0] data_out;uart_rx uart_rx (

.clk (clk ), //input

.rst ( rst ), //input

.rx_en ( rx_en ), //input

.data_in ( uart_data_rx ), //input

.data_out ( data_out ), //output reg [7:0]

.uart_rx_done ( uart_rx_done ) //output

);uart_tx uart_tx(

.clk ( clk ), //input

.rst ( rst ), //input

.tx_en ( uart_rx_done ), //input

.data_din ( data_out ), //input [7:0]

.data_out ( uart_data_out ), //output

.uart_tx_done ( uart_tx_done ) //output );endmodule 2.4仿真模块代码

module uart_tb();reg clk;

reg rst;

reg rx_en;

reg uart_data_rx;

wire uart_data_out;initial beginrst = 1'b1;clk = 1'b1;uart_data_rx = 1'b1;rx_en = 1'b0;#20rst = 1'b0;#4340uart_data_rx = 1'b0;rx_en = 1'b1;#20rx_en = 1'b0;#8680 uart_data_rx = 1'b1;#8680 uart_data_rx = 1'b0;#8680 uart_data_rx = 1'b1;#8680 uart_data_rx = 1'b0;#8680 uart_data_rx = 1'b1;#8680 uart_data_rx = 1'b0;#8680 uart_data_rx = 1'b1;#8680 uart_data_rx = 1'b0;#8680 uart_data_rx = 1'b1;endalways #10 clk = !clk;uart_top uart_top_inst (.clk(clk),.rst(rst),.rx_en(rx_en),.uart_data_rx(uart_data_rx),.uart_data_out(uart_data_out)

);endmodule3.仿真波形

3.1 接收模块仿真波形

数据输入先放到低位依次传入

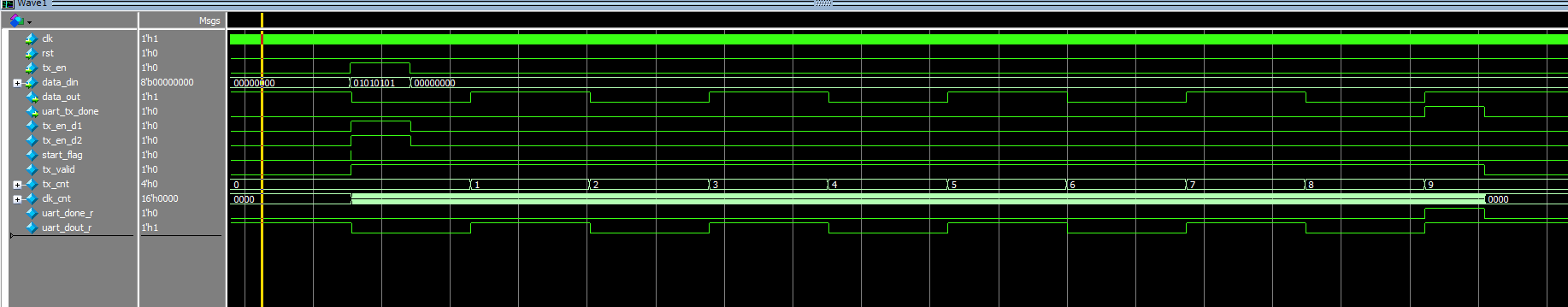

3.2 发送模块仿真波形

发送的时候,把需要发送的数据低位先发

3.3 顶层模块仿真波形

相关文章:

FPGA_UART

1.UART 概述 (通用异步收发传输器) 1. 基本定义 UART(Universal Asynchronous Receiver/Transmitter)是一种常见的串行通信协议,用于在设备间通过异步串行通信传输数据。它不依赖独立的时钟信号,而是通过预…...

绿算轻舟系列FPGA加速卡:驱动数字化转型的核心动力

在数字化浪潮席卷全球的今天,算力已成为推动企业创新和行业升级的核心引擎。绿算轻舟系列FPGA加速卡凭借其高性能、低延迟、高能效比的独特优势,正成为各领域智能化转型的“隐形加速器”。它以灵活的硬件架构和强大的并行计算能力,为复杂场景…...

gitee基本使用

git实用手册 git全局设置 git config --global user.name "yourname" git config --global user.email "youremail"推代码时的账号(email) 版本回退 git loggit reset –hard <码>git push -f HTTPS步骤(上传) 拉取项目 1、新建一个…...

最短路径介绍

最短路径是图论中的算法,下面将列举几个常见的算法: 🚗 一、单源最短路径(一个起点到所有点) 1. Dijkstra 算法 适用图:非负权图(不能有负权边) 思路:贪心 最小堆&am…...

VRRP 基础全解析:从结构到配置

目录 VRRP基本概述 VRRP基本结构 状态机 编辑 负载分担 (多个VRRP) VRRP基本概述 VRRP能够在不改变组网的情况下,将多台路由器虚拟成一个虚拟路由器,通过配置虚拟路由器的IP地址为默认网关,实现网关的备份。协…...

【NIO番外篇】之组件 Buffer

目录 一、Buffer:数据界的“快递小哥”/“临时仓库管理员” 😉什么是 Buffer?它的作用是什么? 二、Buffer 的“三围”和“书签”📌:核心属性1. Capacity (容量):2. Position (位置):…...

)

Python基础知识(一、基础语法)

Python基础知识(一、基础语法) 字面量注释单行注释多行注释 变量数据类型数据类型查看数据类型转换 标识符命名规范不可使用关键字 运算符算数运算符赋值运算符 字符串字符串的定义方式字符串拼接占位拼接数字精度控制快速格式化 数据输入逻辑运算比较运…...

C语言题目自增在前与在后

一、题目引入 谨记真言: i的值最终都会改变 只是表达式的值不同 二、分析题目 if判断语句里面要条件为真执行时 printf语句 i 变量在前 使用i的当前值是1 i的值就是1与1相等 所以&&左边的为真 但是&&存在 必须前后都为真才为真 所以还要看&&后面…...

【口腔粘膜鳞状细胞癌】文献阅读

写在前面 看看文章,看看有没有思路 文献 The regulatory role of cancer stem cell marker gene CXCR4 in the growth and metastasis of gastric cancer IF:6.8 中科院分区:1区 医学WOS分区: Q1 目的:通过 scRNA-seq 结合大量 RNA-seq 揭示癌症干细胞…...

如何撤回刚提交的 commit

如何撤回刚提交的 commit 如果刚刚执行了 git commit 但想撤销这个提交,有几种方法可以实现,具体取决于你想达到的效果: 1. 撤销 commit 但保留更改(修改回到暂存区) git reset --soft HEAD~1这会撤销最后一次提交提…...

deepin使用autokey添加微信快捷键一键显隐ctrl+alt+w

打开deepin商店,搜索快捷键,找到autokey 快捷键管理,点击安装 点击右键新建文件夹 点击右键新建脚本 打开脚本并添加以下内容 import subprocess import time# ------------------ 配置项 ------------------ WM_CLASS "wechat…...

开源微调混合推理模型:cogito-v1-preview-qwen-32B

一、模型概述 1.1 模型特点 Cogito v1-preview-qwen-32B 是一款基于指令微调的生成式语言模型(LLM),具有以下特点: 支持直接回答(标准模式)和自我反思后再回答(推理模式)。使用 I…...

【uniapp-兼容性处理】swiper在iOS上偶发出现后几张图片白屏情况

【日期】2025-04-14 【问题】 swiper在iOS上偶发出现后几张图片白屏情况 swiper内部的几个swiper-item垂直排列,各自进行滚动,样式方面兼容性出现问题 【原因】: 原代码:(不应在swiper-item添加style属性…...

go中new和make有什么异同?

相同点:都是给变量分配内存 不同点: 作用类型不同。new通常给int、string、数组类型的变量分配内存,而make通常给slice、map、channel分配内存。返回值类型不同。new返回指向变量的指针,make返回的是变量本身new分配内存空间后&…...

RabbitMQ 深度解析:从基础到高级应用的全面指南

🐰 RabbitMQ 深度解析:从基础到高级应用的全面指南 前言📘 一、RabbitMQ 简介⚙️ 二、核心特性可靠性 🔒灵活路由 🔄高可用性 🌐多协议支持 🌍多语言客户端 💻插件机制 ὐ…...

)

动手强化学习之马尔可夫决策(机器人篇)

1 马尔可夫决策过程 马尔可夫决策过程(Markov Decision Process, MDP)是一种数学框架,用于建模智能体(agent)在随机环境中做决策的问题。它假设环境的状态转换具有马尔可夫性质,即未来的状态只依赖于当前状…...

【RabbitMQ】核心概念和工作流程

文章目录 RabbitMQ 工作流程流程图 Producer 和 ConsumerConnecting 和 ChannelVirtual hostQueueExchangeRabbitMQ 工作流程 RabbitMQ 工作流程 流程图 RabbitMQ 就是一个生产者/消费者模型 Producer 就是生产者、Consumer 就是消费者Broker 是 RabbitMQ 服务器生产者和消费…...

Windows 操作系统 - Windows 10 磁盘管理无法为 C 盘选择扩展卷

Windows 10 磁盘管理无法为 C 盘选择扩展卷 在 Windows 10 的磁盘管理中,无法为 C 盘选择扩展卷(选项灰色不可用),主要原因是未分配空间没有紧邻 C 盘的右侧 补充:Windows 10 磁盘管理打开方式 1. 按下快捷键【Win …...

数据结构——双向链表

首先我们要介绍一下链表的分类 链表的分类 链表说明: 虽然有这么多种链表结构,但是我们实际中用的还是两种结构:单链表(单向不带头不循环)和 双向带头循环链表 。 单链表(单向不带头不循环)&…...

Git报错remote: Verify fatal: Authentication failed for ***

解决 Git 拉取代码时报错:fatal: Authentication failed 在使用 Git 时,执行如下命令: git pull origin master出现报错: remote: Verify fatal: Authentication failed for ***一、问题原因分析 1. 使用 HTTP 协议访问&#…...

八、自动化函数

1.元素的定位 web自动化测试的操作核心是能够找到页面对应的元素,然后才能对元素进行具体的操作。 常见的元素定位方式非常多,如id,classname,tagname,xpath,cssSelector 常用的主要由cssSelector和xpath 1.1 cssSelector选择器 选择器的功能&#x…...

websoket 学习笔记

目录 基本概念 工作原理 优势 应用场景 HTTP协议与 webSoket协议之间的对比 消息推送场景 1. 轮询(Polling) 2. 长轮询(Long Polling) 3. 服务器发送事件(Server-Sent Events, SSE) 4. WebSocket…...

正版金币捕鱼海洋管家APP源码结构解析与运行环境说明

这是一款基于成熟运营逻辑开发的休闲类互动娱乐游戏《海洋管家》,采用金币流通体系,双端源码完整,结构清晰,适合用于结构学习、本地部署测试或功能参考。 整体玩法围绕捕鱼为主线,并融合了排行榜、VIP、签到、道具商城…...

大语言模型深度思考与交互增强

总则:深度智能交互的全面升级 在主流大语言模型(LLM)与用户的每一次交互中,模型需于回应或调用工具前,展开深度、自然且无过滤的思考进程。当模型判断思考有助于提升回复质量时,必须即时进行全方位的思考与…...

Vue.js 项目中 vue.config.js 常用配置项解析

Vue.js 项目中 vue.config.js 常用配置项解析 摘要 在 Vue CLI 创建的项目中,vue.config.js 是核心配置文件,用于定制化构建、开发和部署流程。本文详细解析了该文件的常用配置项,包括基础路径、开发服务器、Webpack 配置、CSS 预处理、插件…...

Javascript逗号操作符

这段代码是一个使用了生成器函数(Generator Function)的无限循环(for (;;)),内部通过switch语句控制流程。代码中有很多逗号分隔的语句,这其实是利用了JavaScript的逗号操作符(comma operator&a…...

windows系统安装驱动、cuda和cudnn

一、首先在自己的电脑里安装了nvidia的独立显卡 显卡的查找方式: CtrlShiftEsc打开任务管理器,点击性能,点击GPU 0查看显卡型号,如下图所示: 只要电脑中有nvidia的独立显卡,就可以暗转显卡驱动、cuda和cu…...

常见的 14 个 HTTP 状态码详解

文章目录 一、2xx 成功1、200 OK2、204 No Content3、206 Partial Content 二、3xx 重定向1、301 Moved Permanently2、302 Found3、303 See Other注意4、Not Modified5、307 Temporary Redirect 三、4xx 客户端错误1、400 Bad Request2、401 Unauthorized3、403 Forbidden4、4…...

)

DAY 44 leetcode 28--字符串.实现strStr()

题号28 给你两个字符串 haystack 和 needle ,请你在 haystack 字符串中找出 needle 字符串的第一个匹配项的下标(下标从 0 开始)。如果 needle 不是 haystack 的一部分,则返回 -1 。 我的解法 双指针,slow定位&…...

Nginx用途以及好处:

反向代理: 1、提高访问速度 2、进行负载均衡:所谓负载均衡,就是把大量的请求按照我们指定的的方式均衡的分配给集群中的每台服务器(不使用nginx前端会固定的访问某一台服务器 加入nginx分配到多台服务器) 3、保证后端的安全 服务器一般部署在…...

打造可控可测的星座网络:IPLOOK低轨通信仿真平台搭建实践

在低轨卫星通信迅猛发展的趋势下,空天地一体化网络正逐步成为新一代信息基础设施的核心组成。作为移动核心网领域的技术引领者,IPLOOK依托在5G核心网、NTN(非地面网络)和卫星通信仿真方面的技术优势,率先构建了自主可控…...

)

火车头采集动态加载Ajax数据(无分页瀑布流网站)

为了先填充好数据在上线,在本地搭建了一个网站,并用火车头采集数据填充到里面。 开始很上手,因为找的网站的分类中是有分页的。很快捷的找到页面标识。 但是问题来了,如今很多网站都是采用的Ajax加载数据,根本没有分…...

严重超时完结,不过,撒花)

笔记:代码随想录算法训练营day67:Floyd 算法精讲、A * 算法精讲 (A star算法) 严重超时完结,不过,撒花

学习资料:代码随想录 Floyd 算法精讲 卡码网:97. 小明逛公园 首先明确floyd算法解决的是多源最短路径问题,对边的权的正负值没有要求,而且是动态规划的思想 五部曲: 定义:grid[i][j][k]表示从i出发到j…...

)

Electron Forge【实战】桌面应用 —— AI聊天(中)

系列教程 Electron Forge【实战】桌面应用 —— AI聊天(上) 添加本地存储 Dexie.js 用 IndexedDB 实现,Dexie.js 库简化操作 npm i dexie新建文件 src\db.ts import Dexie, { type EntityTable } from "dexie";import { Provide…...

国达陶瓷重磅推出陶瓷罗马柱外墙整装尖端新产品“冠岩臻石”

近日,记者在佛山国达建材有限公司(以下简称国达陶瓷)董事长杨建平处了解到,该公司重磅推出的“冠岩臻石”新产品,是属于陶瓷罗马柱外墙整装产品中的尖端产品。新产品自面市之后,深受高端用户的青睐与认可。…...

Java 系统设计:如何应对高并发场景?

Java 系统设计:如何应对高并发场景? 在现代互联网应用中,高并发场景已经成为系统设计中不可避免的挑战。无论是电商秒杀、抢票系统,还是实时数据处理平台,高并发场景都对系统的性能、稳定性和扩展性提出了极高的要求。…...

VR 全景多维赋能,众趣科技助力零售业开启购物新时代

说到商铺这个词,最早形成于春秋战国时期,当时还未形成固定位置的商铺,部分有远见的商人会在人流量较大的区域摆设摊位,促进了城市的繁荣。到了唐宋时期,商铺进一步发展,并随着商品经济的发展和城市人…...

的差异)

五大生产模式(MTS、MTO、ATO、ETO、CTO)的差异

五大生产模式(MTS、MTO、ATO、ETO、CTO)差异 一、 库存控制二、 订货提前期三、交期与库存分析四、五大生产模式的产品生命周期 一、 库存控制 ETO 模式侧重于原材料库存管理,以应对定制设计所需的物料供应。 MTO 模式重点是原材料库存&…...

clickhosue中json字符串转为表

将json字符串直接通过sql转为表,这里就可以直接把接口来的数据,直接通过clickhouse进行关联查询了。 -- 将json字符串直接通过sql转为表,这里就可以直接把接口来的数据,直接通过clickhouse进行关联查询了。 WITH -- 解析 JSON 数据为字符串json_data AS (SELECT [{"c…...

二叉树的基本功能实现

一.二叉树的结构及实现 1.二叉树的结构 在之前的章节中已经介绍过,二叉树是一种特殊的树,其最大度为2,及最多有左,右两个孩子,结构图如下 在此之前已经讨论过一些特殊的二叉树,这里讨论一般的二叉树 2.…...

VSCode 降低适用版本并且关闭自动更新

VSCode 降低适用版本并且关闭自动更新 相关链接问题描述解决方法下载安装包关闭自动更新 参考链接 相关链接 VSCode 官网 问题描述 无法正常使用vscode-remote插件远程连接Centos7等一些老版本Linux云服务器(如Centos7) 从2024年1月,vsco…...

(二))

OpenHarmony - 小型系统内核(LiteOS-A)(二)

OpenHarmony - 小型系统内核(LiteOS-A)(二) 三、基础内核 3.1、中断及异常处理 基本概念 中断是指出现需要时,CPU暂停执行当前程序,转而执行新程序的过程。即在程序运行过程中,出现了一个必须…...

2025第十六届蓝桥杯PythonA组部分题解

试题A:数字求和 题目描述 给定两个整数a和b,输出它们的和。 输入格式:两个整数,空格分隔 输出格式:一个整数 输入输出样例 输入: 5 8输出: 13解题思路 直接使用加法运算符计算两数之和。…...

苍穹外卖day04

Spring Task实现定时处理订单状态 作用:不需要输入提示信号,便可定时自动执行程序 使用步骤 1、启动类上加上注解(EnableScheduling)开启定时任务调度 2、专门创建一个包来管理执行定时任务的类,该类需要交给IOC容…...

曲线与曲面的绘制

一、学习目标 (1)掌握常用规则参数曲线与曲面的编程绘制方法。 (2)掌握自由曲线与曲面的编程绘制方法。 (3)了解自由曲面的拼接编程方法。 二、学习内容 (1)编程绘一个规则参数…...

Python Cookbook-6.2 定义常量

任务 你需要定义一些模块级别的变量(比如命名的常量),而且客户代码无法将其重新绑定。 解决方案 你可以把任何对象当做模块一样安装。将下列代码存为一个模块const.py,并放入你的Python的sys.path 指定的目录中: class _const(object):class ConstEr…...

)

【信息系统项目管理师】高分论文:论信息系统项目的范围管理(信息化系统综合管理平台)

更多内容请见: 备考信息系统项目管理师-专栏介绍和目录 文章目录 论文1、规划范围管理2、收集需求3、定义范围4、创建WBS5、确认范围6、控制范围论文 2017年6月,我作为项目经理参与了 XX市经济和信息化委员会系统综合管理平台建设项目,该项目投资共150万元人民币,建设工期…...

用Webpack 基础配置快速搭建项目开发环境

Webpack 是一个现代 JavaScript 应用程序的静态模块打包工具,但是Webpack有大量的配置项,对新手不太友好,但是我们可以根据webpack-cli的init命令根据项目需求快速生成webpack的配置文件,本文将手把手教你如何用 Webpack 和 npm 快…...

【LLM Agent】SystemMessage 和 HumanMessage

文章目录 SystemMessage 和 HumanMessageSystemMessage(系统消息)HumanMessage(用户消息)结合使用高级设置能否将用户消息(HumanMessage)写在系统消息(SystemMessage) SystemMessage…...

机器学习核心知识:从基础概念到关键算法

摘要 本文深度剖析机器学习知识体系,从基本概念、学习方式,到分类算法、逻辑回归等关键内容均有涉及。详细阐述各知识点原理与应用场景,并对比多种算法的优劣。 关键词:机器学习;监督学习;分类算法&#x…...