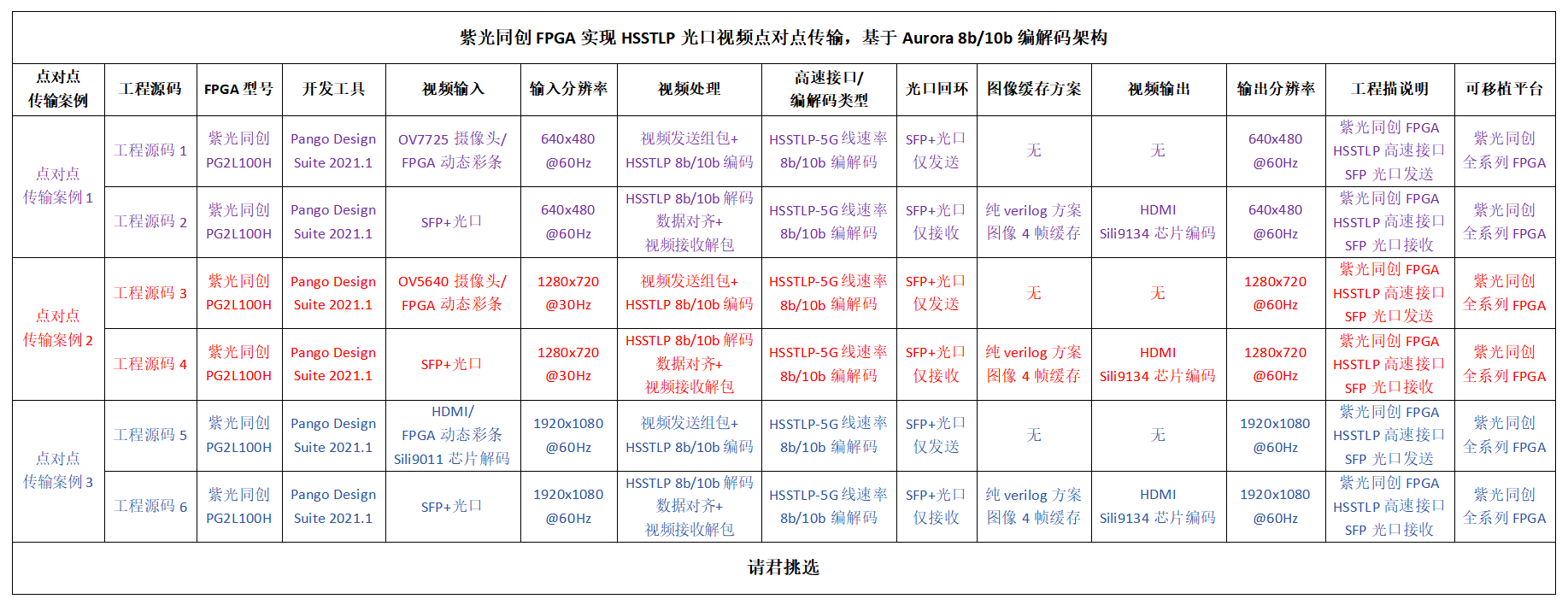

紫光同创FPGA实现HSSTLP光口视频点对点传输,基于Aurora 8b/10b编解码架构,提供6套PDS工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 紫光同创FPGA相关方案推荐

- 我这里已有的 GT 高速接口解决方案

- Xilinx系列FPGA实现GTP光口视频传输方案推荐

- Xilinx系列FPGA实现GTX光口视频传输方案推荐

- Xilinx系列FPGA实现GTH光口视频传输方案推荐

- Xilinx系列FPGA实现UltraScale-GTH光口视频传输方案推荐

- Xilinx系列FPGA实现UltraScale-GTY光口视频传输方案推荐

- 3、设计思路框架

- 工程设计原理框图

- 输入Sensor之-->OV7725摄像头

- 输入Sensor之-->OV5640摄像头

- 输入Sensor之-->芯片解码的HDMI

- 视频数据组包

- 基于HSSTLP高速接口的视频传输架构

- HSSTLP IP 简介

- HSSTLP基本结构

- HSSTLP发送和接收处理流程

- HSSTLP的参考时钟

- HSSTLP发送接口

- HSSTLP接收接口

- HSSTLP IP核调用和使用

- 数据对齐

- 视频数据解包

- 图像缓存架构

- HDMI输出架构

- 点对点视频发送端工程源码架构

- 点对点视频接收端工程源码架构

- 4、PDS工程源码1详解:点对点OV7725视频转SFP光口发送

- 5、PDS工程源码2详解:点对点SFP光口接收OV7725视频转HDMI

- 6、PDS工程源码3详解:点对点OV5640视频转SFP光口发送

- 7、PDS工程源码4详解:点对点SFP光口接收OV5640视频转HDMI

- 8、PDS工程源码5详解:点对点HDMI视频转SFP光口发送

- 9、PDS工程源码6详解:点对点SFP光口接收HDMI视频转HDMI

- 7、上板调试验证并演示

- 准备工作

- HSSTLP光口视频点对点传输效果演示

- 8、福利:工程源码获取

紫光同创FPGA实现HSSTLP光口视频点对点传输,基于Aurora 8b/10b编解码架构,提供6套PDS工程源码和技术支持

1、前言

国产FPGA现状:

“苟利国家生死以,岂因祸福避趋之!”大洋彼岸的我优秀地下档员,敏锐地洞察到祖国的短板在于先进制程半导体的制造领域,于是本着为中华民族伟大复兴的中国梦贡献绵薄之力的初心,懂先生站在高略高度和长远角度谋划,宁愿背当代一世之骂名也要为祖国千秋万世谋,2018年7月,懂先生正式打响毛衣战,随后又使出恰勃纸战术,旨在为祖国先进制程半导体领域做出自主可控的战略推动;2019年初我刚出道时,还是Xilinx遥遥领先的时代(现在貌似也是),那时的国产FPGA还处于黑铁段位;然而才短短7年,如今的国产FPGA属于百家争鸣、百花齐放、八仙过海、神仙打架、方兴未艾、得陇望蜀、友商都是XX的喜极而泣之局面,此情此景,不得不吟唱老人家的诗句:魏武挥鞭,东临碣石有遗篇,萧瑟秋风今又是,换了人间。。。

目前对于国产FPGA优势有以下几点:

1:性价比高,与同级别国外大厂芯片相比,价格相差几倍甚至十几倍;

2:自主可控,国产FPGA拥有完整自主知识产权的产业链,从芯片到相关EDA工具;

3:响应迅速,FAE技术支持比较到位,及时解决开发过程中遇到的问题,毕竟中文数据手册;

4:采购方便,产业链自主可控,采购便捷;

FPGA实现SFP光口视频编解码现状;

目前FPGA实现SFP光口传输方案很丰富,主流还是Xilinx的GT系列,此外国产FPGA厂商也纷纷抄袭Xilinx推出了自己的高速接口方案;基于Xilinx系列FPGA的SFP光口视频编解码主要有以下几种,Artix7系列的GTP、Kintex7系列的GTX、更高端FPGA器件的GTH、GTY、GTV、GTM等,线速率越来越高,应用场景也越来越高端;编码方式也是多种多样,有8b/10b编解码、64b/66b编解码、HDMI编解码、SDI编解码等等;国产的紫光同创也推出了HSSTLP方案,官方宣称其性能可对标Xilinx的GTP,但本博实际测试发现,HSSTLP无论是功能还是性能都无法与Xilinx的GTP相媲美,但将个烂就也行,毕竟聊胜于无嘛;本设计采用紫光同创系列FPGA的HSSTLP作为高速接口、8b/10b编解码的方式实现SFP光口视频编解码;

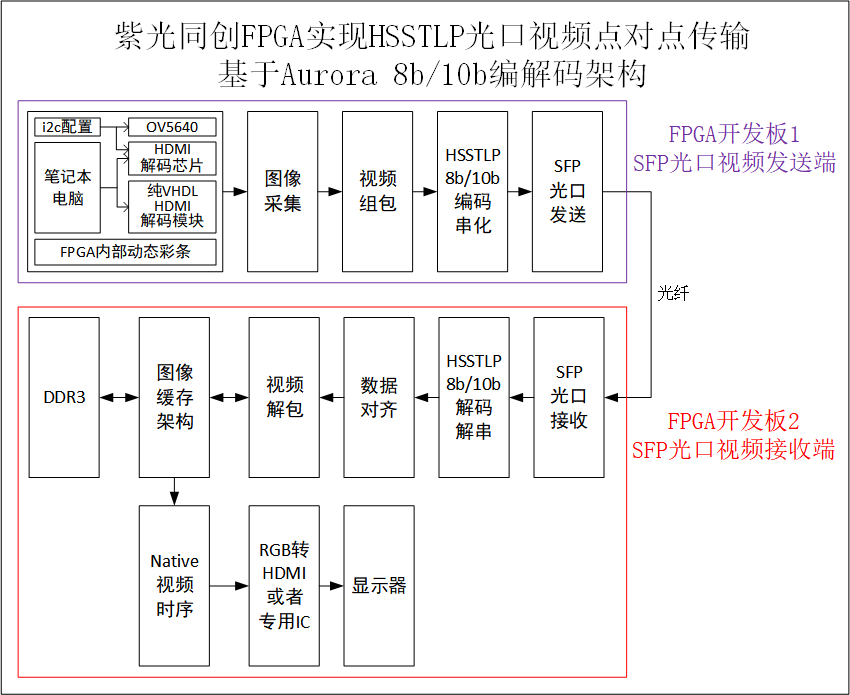

工程概述

本设计使用紫光同创系列FPGA为平台,实现HSSTLP光口视频点对点传输,所谓点对点传输,也就是两块FPGA开发板之间的相互传输;比如FPGA开发板1采集视频并通过SFP光口输出,FPGA开发板2通过SFP光口接收视频然后转HDMI输出给显示器;

视频发送端处理流程如下:

FPGA开发板1的视频输入源有多种,一种是板载的HDMI输入接口,另一种是传统摄像头,包括OV7725、OV5640和AR0135;如果你的FPGA开发板没有视频输入接口,或者你的手里没有摄像头时,可以使用FPGA逻辑实现的动态彩条模拟输入视频,代码里通过parametr参数选择视频源,默认不使用动态彩条;FPGA首先对摄像头进行i2c初始化配置,然后采集摄像头视频;然后采集的输入视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTLP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;

视频接收端处理流程如下:

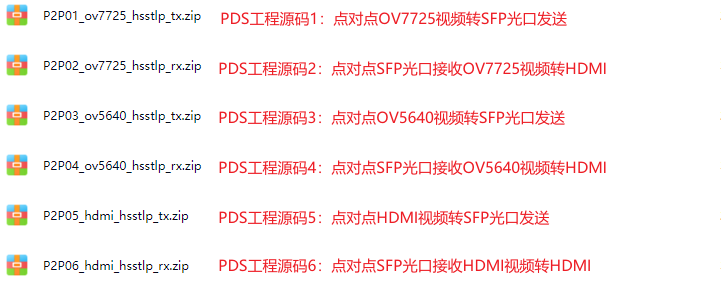

FPGA开发板2用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTLP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR3作为缓存介质;然后Native视频时序控制图像缓存架构从DDR3中读取视频,并做Native视频时序同步,输出RGB888视频;然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;针对市场主流需求,本设计提供6套PDS工程源码,具体如下:

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1:点对点传输案例1的视频发送端工程

此工程为点对点传输案例1的视频发送端工程,即视频HSSTLP 8b/10b编码转SFP光口输出;开发板FPGA型号为PG2L100H-6EBG676;输入视频为OV7725摄像头或者动态彩条,默认使用OV7725;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为640x480@60Hz;然后采集的输入视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTLP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出,输出分辨率为640x480@60Hz;由此形成Sensor+8b/10b编码+SFP光口的高端架构;该工程适用于视频转SFP光口光端机应用;

工程源码2:点对点传输案例1的视频接收端工程

此工程为点对点传输案例1的视频接收端工程,即SFP光口视频接收HSSTLP 8b/10b解码转HDMI输出;FPGA开发板2用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTLP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR3作为缓存介质;然后Native视频时序控制图像缓存架构从DDR3中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为640x480@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;由此形成Sensor+高速接口+光编码+HDMI的高端架构;该工程适用于SFP光口的视频采集卡(光端机)应用;

工程源码3:点对点传输案例2的视频发送端工程

此工程为点对点传输案例2的视频发送端工程,即视频HSSTLP 8b/10b编码转SFP光口输出;FPGA型号为PG2L100H-6EBG676;输入视频为OV5640摄像头或者动态彩条,默认使用OV5640;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为1280x720@30Hz;然后采集的输入视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTLP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;输出分辨率为1280x720@60Hz;由此形成Sensor+8b/10b编码+SFP光口的高端架构;该工程适用于视频转SFP光口光端机应用;

工程源码4:点对点传输案例2的视频接收端工程

此工程为点对点传输案例2的视频接收端工程,即SFP光口视频接收HSSTLP 8b/10b解码转HDMI输出;FPGA开发板2用板载的SFP光口的光纤接收视频;然后送入紫光同创官方的HSSTLP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR3作为缓存介质;然后Native视频时序控制图像缓存架构从DDR3中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1280x720@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;由此形成Sensor+高速接口+光编码+HDMI的高端架构;该工程适用于SFP光口的视频采集卡(光端机)应用;

工程源码5:点对点传输案例3的视频发送端工程

此工程为点对点传输案例3的视频发送端工程,即视频HSSTLP 8b/10b编码转SFP光口输出;开发板FPGA型号为PG2L100H-6EBG676;输入视频为HDMI视频,用笔记本电脑模拟,笔记本电脑通过HDMI线连接FPGA开发板的HDMI输入接口,板载的silicom9011芯片实现HDMI视频解码,FPGA使用纯Verilog实现的i2c总线对silicom9011进行初始化配置,分辨率配置为1920x1080@60Hz,输出RGB888视频给FPGA;然后采集的输入视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTLP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;输出分辨率为1920x1080@60Hz;由此形成Sensor+8b/10b编码+SFP光口的高端架构;该工程适用于视频转SFP光口光端机应用;

工程源码6:点对点传输案例3的视频接收端工程

此工程为点对点传输案例3的视频接收端工程,即SFP光口视频接收HSSTLP 8b/10b解码转HDMI输出;FPGA开发板2用板载的SFP光口的光纤接收视频;然后送入紫光同创官方的HSSTLP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR3作为缓存介质;然后Native视频时序控制图像缓存架构从DDR3中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1920x1080@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;由此形成Sensor+高速接口+光编码+HDMI的高端架构;该工程适用于SFP光口的视频采集卡(光端机)应用;

紫光同创紫光同创FPGA实现HSSTLP光口视频点对点传输的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

紫光同创FPGA相关方案推荐

鉴于国产FPGA的优异表现和市场需求,我专门开设了一个人紫光同创FPGA专栏,里面收录了基于紫光同创FPGA的图像处理、UDP网络通信、GT高速接口、PCIE等博客,感兴趣的可以去看看,博客地址:点击直接前往

我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

Xilinx系列FPGA实现GTP光口视频传输方案推荐

Xilinx 7系列FPGA基于GTP实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现GTX光口视频传输方案推荐

Xilinx 7系列FPGA基于GTX实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现GTH光口视频传输方案推荐

Xilinx 7系列FPGA基于GTH实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现UltraScale-GTH光口视频传输方案推荐

Xilinx UltraScale系列FPGA基于UltraScale-GTH实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现UltraScale-GTY光口视频传输方案推荐

Xilinx UltraScale+系列FPGA基于UltraScale-GTY实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

3、设计思路框架

工程设计原理框图

工程设计原理框图如下:

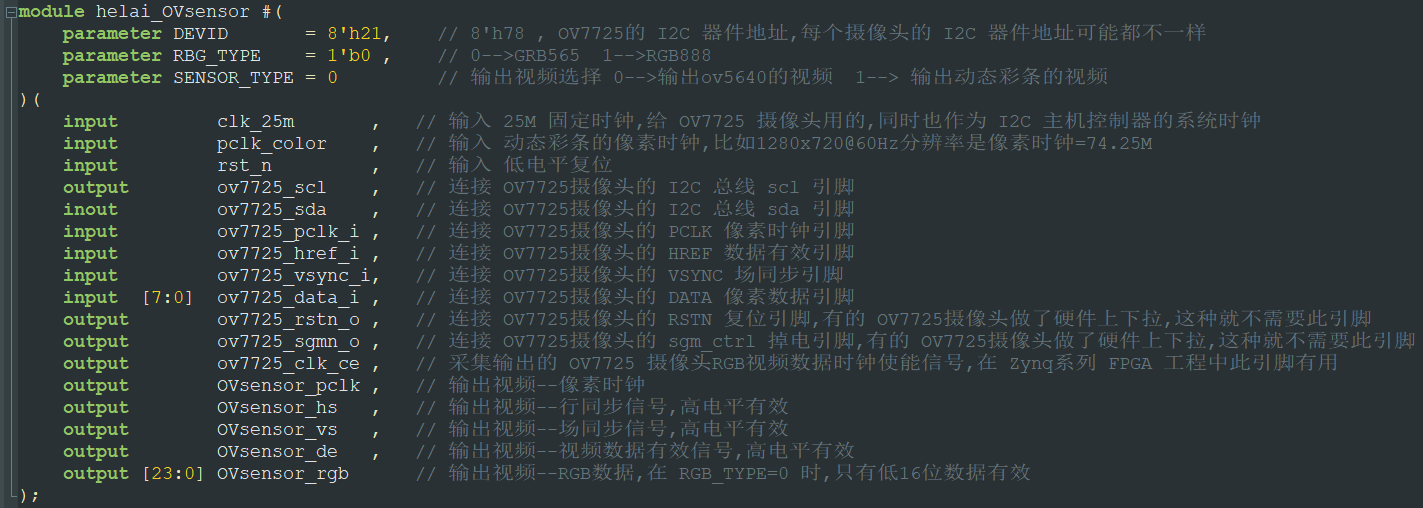

输入Sensor之–>OV7725摄像头

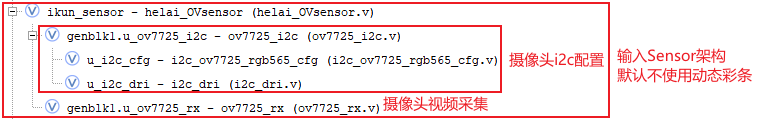

此模块为点对点视频发送端工程所独有;输入Sensor是本工程的输入设备,其一为OV7725摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV7725摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

OV7725摄像头需要i2c初始化配置,本设计配置为640x480@60Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV7725摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV7725摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

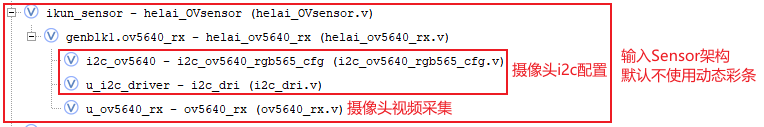

输入Sensor之–>OV5640摄像头

此模块为点对点视频发送端工程所独有;输入Sensor是本工程的输入设备,其一为OV5640摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV5640摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

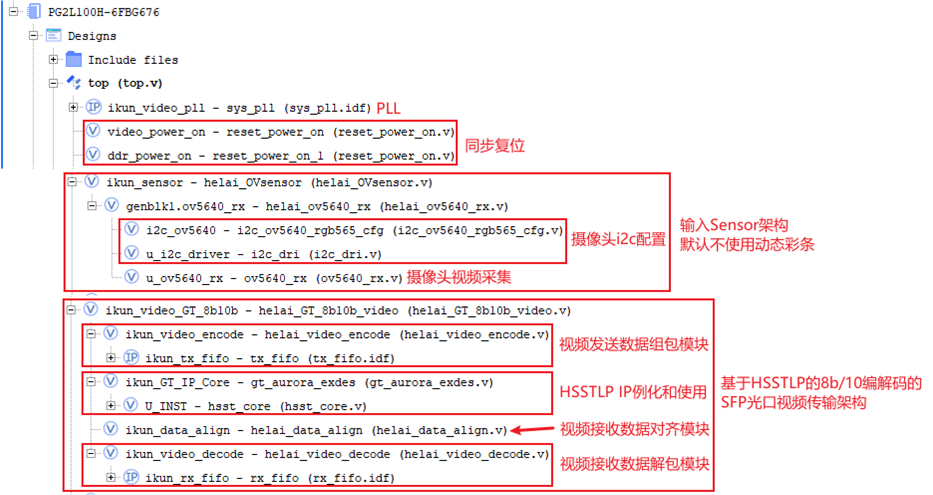

OV5640摄像头需要i2c初始化配置,本设计配置为1280x720@30Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV5640摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV5640摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

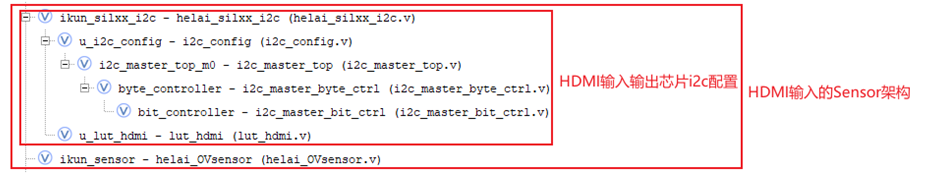

输入Sensor之–>芯片解码的HDMI

此模块为点对点视频发送端工程所独有;输入Sensor是本工程的输入设备,其二为板载的HDMI输入接口;输入源为板载的HDMI输入接口或动态彩条,分辨率为1920x1080@60Hz,使用笔记本电脑接入HDMI输入接口,以模拟输入Sensor;HDMI解码方案为芯片解码,使用Silcom9011,可将输入的HDMI视频解码为RGB888视频;FPGA纯verilog实现的i2c配置模块完成对Silcom9011芯片的配置,分辨率配置为1920x1080@60Hz;可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出HDMI接口采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

整个模块代码架构如下:

视频数据组包

此模块为点对点视频发送端工程所独有;由于视频需要在HSSTLP中通过aurora 8b/10b协议收发,所以数据必须进行组包,以适应aurora 8b/10b协议标准;视频数据组包模块代码位置如下:

首先,我们将16bit的视频存入FIFO中,存满一行时就从FIFO读出送入HSSTLP发送;在此之前,需要对一帧视频进行编号,也叫作指令,HSSTLP组包时根据固定的指令进行数据发送,HSSTLP解包时根据固定的指令恢复视频的场同步信号和视频有效信号;当一帧视频的场同步信号上升沿到来时,发送一帧视频开始指令 0,当一帧视频的场同步信号下降沿到来时,发送一帧视频开始指令 1,视频消隐期间发送无效数据 0 和无效数据 1,当视频有效信号到来时将每一行视频进行编号,先发送一行视频开始指令,在发送当前的视频行号,当一行视频发送完成后再发送一行视频结束指令,一帧视频发送完成后,先发送一帧视频结束指令 0,再发送一帧视频结束指令 1;至此,一帧视频则发送完成,这个模块不太好理解,所以我在代码里进行了详细的中文注释,需要注意的是,为了防止中文注释的乱序显示,请用notepad++编辑器打开代码;指令定义如下:

注意!!!指令可以任意更改,但最低字节必须为bc;

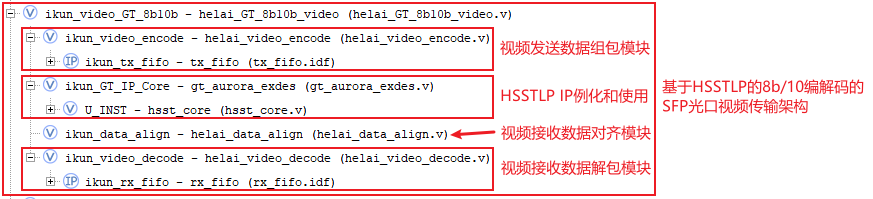

基于HSSTLP高速接口的视频传输架构

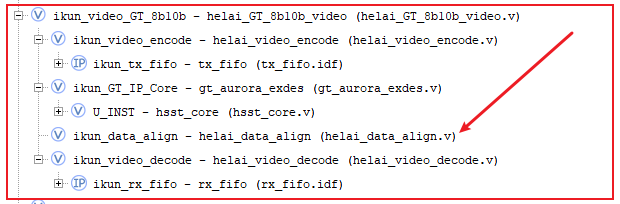

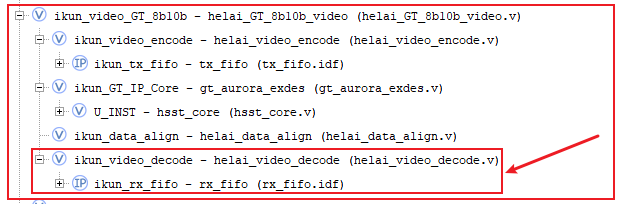

HSSTLP aurora 8b/10b编解码整体模块在视频点对点传输发送端和接收端都用到了;本设计使用HSSTLP高速接口传输视频,使用8b/10b编解码协议,搭建基于HSSTLP高速接口的视频传输架构,包括视频数据组包模块、HSSTLP IP核配置调用、接收数据对齐模块、视频数据解包模块等部分,总体代码架构如下:

基于HSSTLP高速接口的视频传输架构顶层接口核参数配置如下:

本设计共例化了2路HSSTLP,所以2路HSSTLP的收发回环方式也做了灵活的参数化配置,如果你只需要1路HSSTLP,则可删除另一路,如果你想例化更多路HSSTLP,则可根据上述设计方法扩展,十分方便;

HSSTLP IP 简介

关于HSSTLP介绍最详细的肯定是紫光同创官方的《Logos2 系列产品 HSSTLP IP 用户指南》,我们以此来解读:

Logos2 系列产品内置了高速串行接口模块,即 HSSTLP。除了 PMA,HSSTLP 还集成了丰富的 PCS功能,可灵活应用于各种串行协议标准,每通道的收发速度高达6.6 Gb/s,收发器支持不同的串行传输接口或协议,支持 PCI1.0,PCI2.0,XAUI,千兆以太网,CPRI,SRIO 等协议,官方宣称可对标Xilinx的GTP;

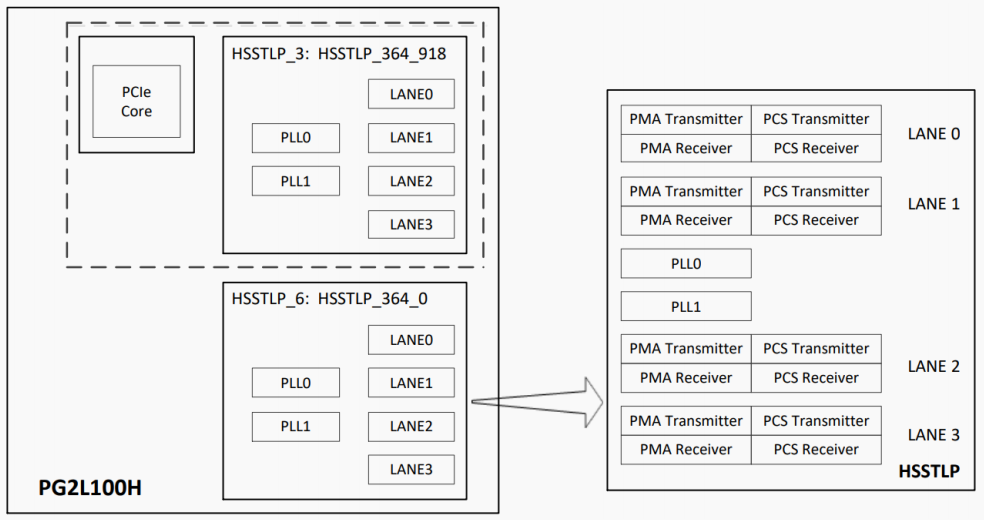

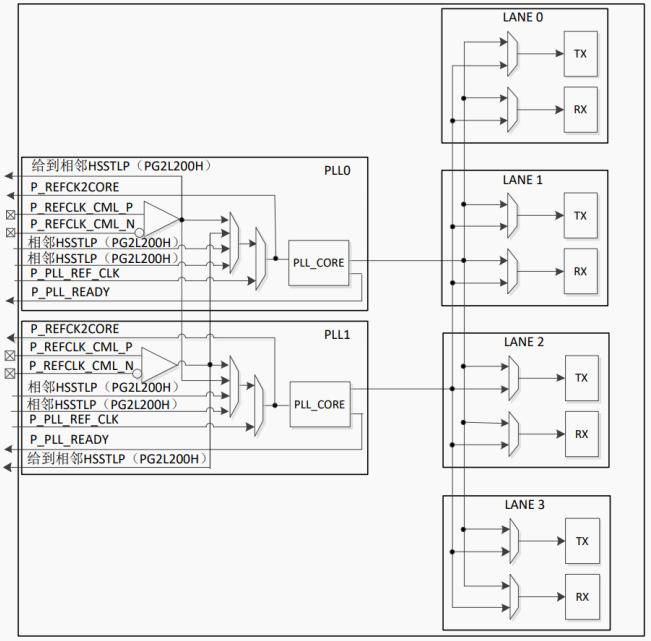

HSSTLP基本结构

紫光同创FPGA的HSSTLP模仿了Xilinx的GTP,HSSTLP基本结构如下:

每个 HSSTLP 由两个 PLL 和四个收发 LANE 组成,其中每个 LANE 有两个子层:PCS(物理编码子层)和 PMA(物理媒体连接子层),PCS 子层包含 8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路;PMA 层主要进行串并、并串转换、预加重、去加重、串行数据的发送和数据时钟的提取,包括四个组件:PCS Transmitter,PMATransmitter,PCS Receiver,PMA Receiver。PCS Transmitter 和 PMA Transmitter组成发送通路,PCS Receiver 和 PMA Receiver 组成接收通路;HSSTLP 中的四个收发 LANE 共享 PLL0 和 PLL1,每个发送或者接收 LANE 都可以独立选择 PLL0 或者 PLL1,PLL 工作频率范围参见《DS04001_Logos2 系列 FPGA 器件数据手册》。PLL0 和 PLL1 都各自对应有一对外部差分参考时钟输入,每个 PLL 还可以选择来自另一个 PLL 的参考时钟或者来自 Fabric 的时钟作为参考时钟输入(Fabric 逻辑时钟做参考时钟,仅用于内部测试);PLL 输出频率支持动态再分频,以适应 Data Rate 范围。

HSSTLP发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

HSSTLP的参考时钟

HSSTLP参考时钟源选择的结构示意图如下:

HSSTLP 支持PLL0、PLL1和LANE TX/RX 参考时钟的灵活选择:每个HSSTLP都有两对专用的差分参考时钟输入管脚 P_REFCK0P/P_REFCK0N和P_REFCK1P/P_REFCK1N,PLL 也可以选择来自 Fabric 的时钟P_PLL0_REF_CLK,P_PLL1_REF_CLK(Fabric 逻辑时钟做参考时钟,仅用于内部测试),仅PG2L200H器件支持选择来自相邻HSSTLP的参考时钟,通过PMA_PLL_REG_REFCLK_SEL和PMA_PLL_REG_CML_CLK_OUT_EN配置,PG2L 系列 25H、50H、100H 不支持这种用法,LANE TX,RX可以各自独立选择来自PLL0或者PLL1输出的时钟;专用时钟输入管脚P_REFCK0P/P_REFCK0N 和

P_REFCK1P/P_REFCK1N也可以通过端口P_PLL0_REFCK2CORE和P_PLL1_REFCK2CORE 输出到Fabric;

HSSTLP发送接口

紫光同创官方的《Logos2 系列产品 HSSTLP IP 用户指南》详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲HSSTLP例化时留给用户的发送部分需要用到的接口;用户只需要关心发送接口的时钟和数据即可,以例化2路HSSTLP为例,经本博主优化,用户只需要关心如下HSSTLP发送接口即可快速使用HSSTLP;

HSSTLP接收接口

紫光同创官方的《Logos2 系列产品 HSSTLP IP 用户指南》详细介绍了接收处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲HSSTLP例化时留给用户的发送部分需要用到的接口;用户只需要关心接收接口的时钟和数据即可,以例化2路HSSTLP为例,经本博主优化,用户只需要关心如下HSSTLP接收接口即可快速使用HSSTLP;

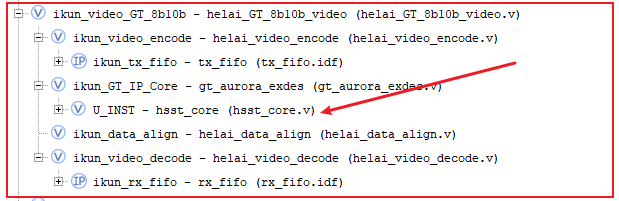

HSSTLP IP核调用和使用

HSSTLP的使用比较特殊,需要先调用配置IP,然后再打开官方生成的Example工程,然后修改Example工程,删除数据生成和数据比对模块,再添加用户需要的信号逻辑,用起来比较麻烦;因为HSSTLP IP配置后并不能直接使用,需要修改其内部代码才能使用,这也是国产FPGA的不成熟之处;HSSTLP IP核配置调用在工程种位置如下:

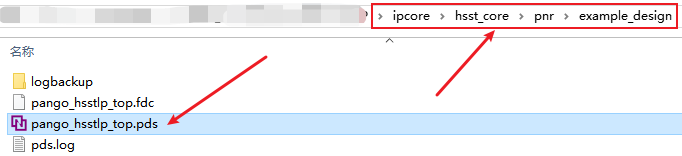

IP配置好后,打开打开官方生成的Example工程,位置如下:

!!!注意

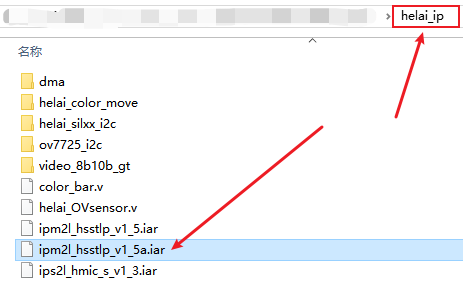

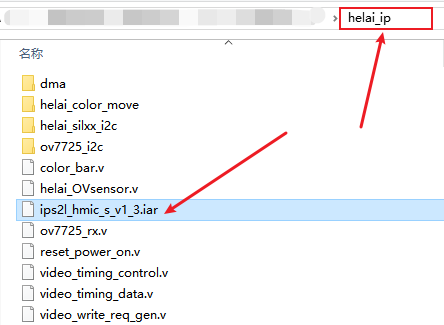

本设计使用的HSSTLP IP版本为ipm2l_hsstlp_v1_5a,安装包以放在资料中,请用户自行安装,安装包目录如下:

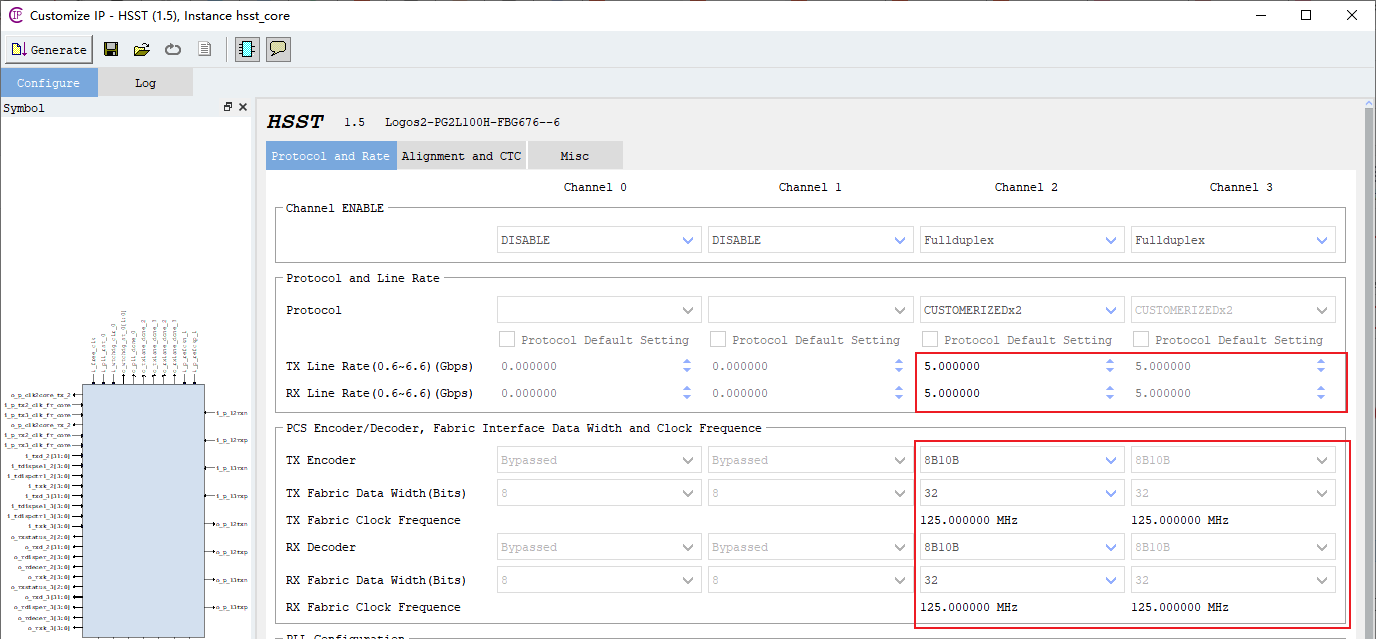

HSSTLP IP核调用和使用很简单,通过PDS的UI界面即可完成,如下:

这里对上图的标号做解释:

1:线速率,根据自己的项目需求来,HSSTLP线速率最高6.6G,由于我的项目是视频传输,所以在HSSTLP的速率范围内均可,为了通用性,我在工程中配置为5G;

2:参考时钟,这个得根据你的原理图来,可以是80M、125M、148.5M、156.25M等等,我的开发板是125M;

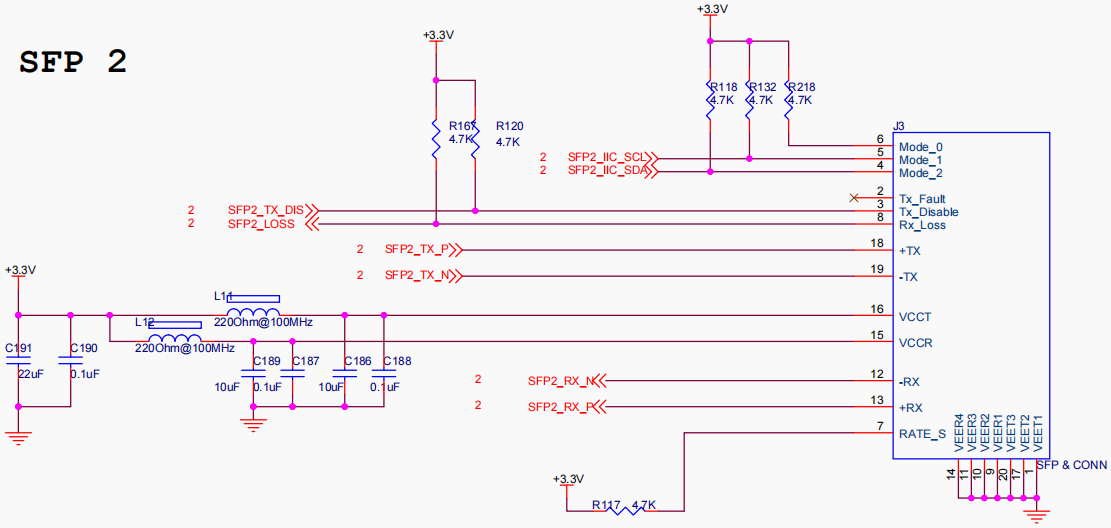

4:HSSTLP通道(Channel)的绑定,这个很重要,他的绑定参考依据有两个,一是你的开发板原理图,二是官方的参考资料《Logos2 系列产品 HSSTLP IP 用户指南》;我的板子原理图如下:

数据对齐

此模块为点对点视频接收端工程所独有;由于HSSTLP资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;数据对齐模块顶层接口如下:

视频数据解包

此模块为点对点视频接收端工程所独有;数据解包是数据组包的逆过程,代码位置如下:

HSSTLP解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;由于数据解包是数据组包的逆过程,所以这里不再过多赘述,视频数据解包模块顶层接口如下:

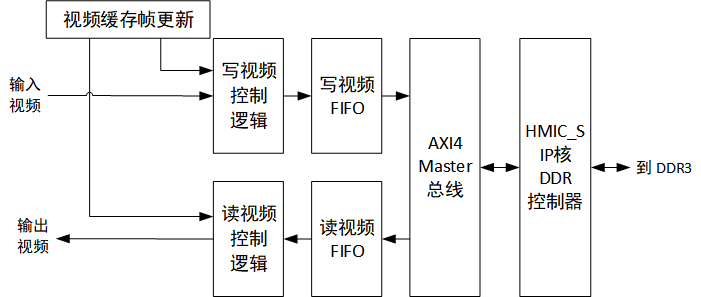

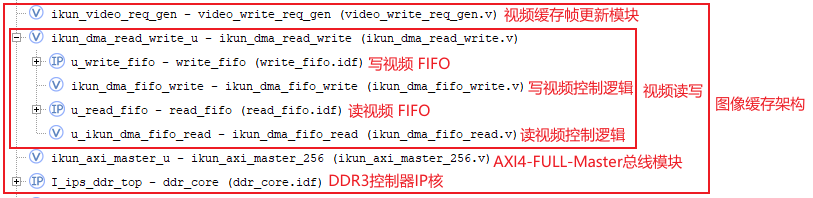

图像缓存架构

此模块为点对点视频接收端工程所独有;图像缓存架构实现的功能是将输入视频缓存到板载DDR3中再读出送后续模块,目的是实现视频同步输出,实现输入视频到输出视频的跨时钟域问题,更好的呈现显示效果;由于调用了紫光官方的HMIC_S IP核作为DDR控制器,所以图像缓存架构就是实现用户数据到HMIC_S的桥接作用;架构如下:

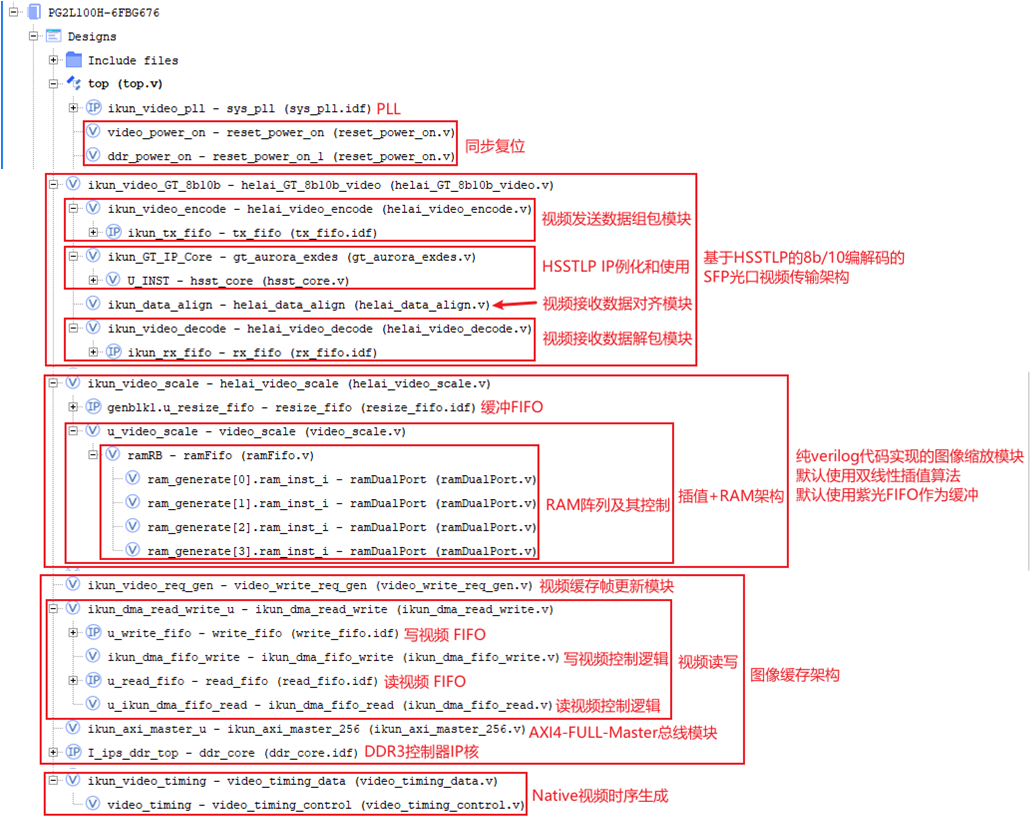

图像缓存架构由视频缓存帧更新模块+写视频控制逻辑+读视频控制逻辑+AXI4-FULL-Master总线模块组成;AXI4-FULL-Master总线模块实际上就是一个AXI4-FULL总线主设备,与HMIC_S IP核对接,HMIC_S IP核配置为AXI4-FULL接口;写视频控制逻辑、读视频控制逻辑实际上就是一个视频读写状态机,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;写视频控制逻辑每次写入一次突发传输的视频数据,记作Y,即每次向DDR3中写入Y个像素,写M×N÷Y次即可完成1帧图像的缓存,读视频与之一样;同时调用两个FIFO实现输入输出视频的跨时钟域处理,使得用户可以忽略AXI4内部代码,以简单地像使用FIFO那样操作AXI4总线,从而达到读写DDR的目的,进而实现视频缓存;本设计图像缓存方式为4帧缓存;图像缓存模块代码架构如下:

!!!注意

本设计使用的DDR3控制器IP版本为ips2l_hmic_s_v1_3,安装包以放在资料中,请用户自行安装,安装包目录如下:

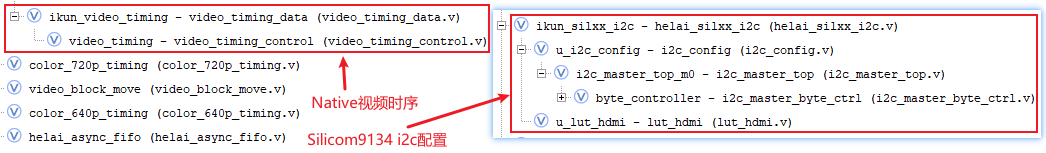

HDMI输出架构

此模块为点对点视频接收端工程所独有;HDMI输出包括Native视频时序和HDMI编码,Native视频时序的作用是产生传统VGA的、RGB的视频流;HDMI编码采用Silicom9134芯片编码方式,FPGA仅需输出RGB视频流即可;HDMI输出代码架构如下:

点对点视频发送端工程源码架构

以工程源码3为例,点对点视频发送端工程源码架构如下:

点对点视频接收端工程源码架构

以工程源码4为例,点对点视频接收端工程源码架构如下:

4、PDS工程源码1详解:点对点OV7725视频转SFP光口发送

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:OV7725摄像头或FPGA内部动态彩条,分辨率640x480@60Hz;

输出:SFP光口,分辨率640x480@60Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b编码;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

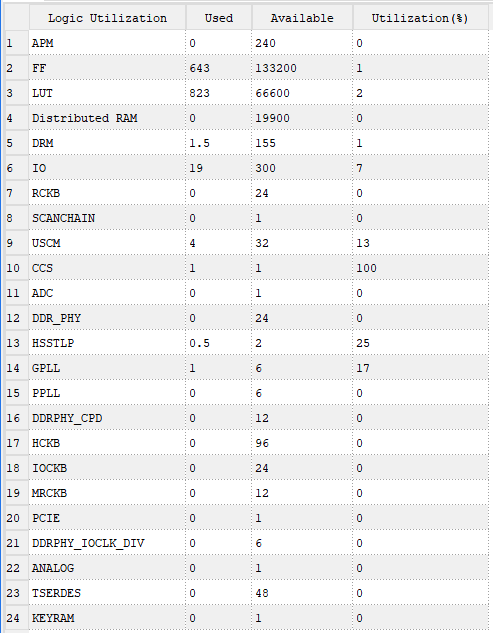

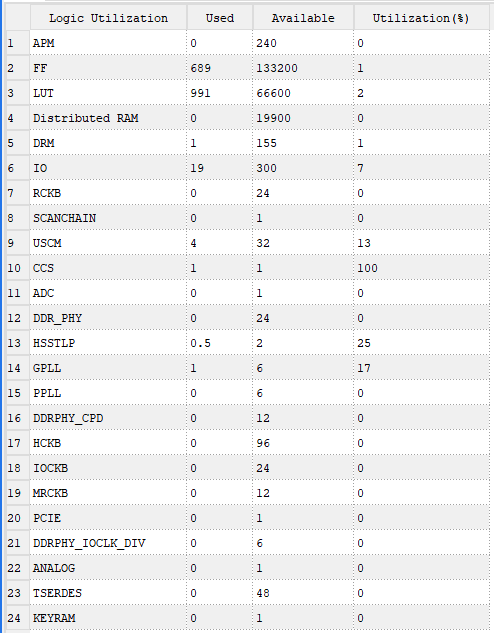

工程的资源消耗和功耗如下:

5、PDS工程源码2详解:点对点SFP光口接收OV7725视频转HDMI

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:SFP光口,分辨率640x480@60Hz;

输出:HDMI,Silicom9134芯片编码,分辨率640x480@60Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b解码;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

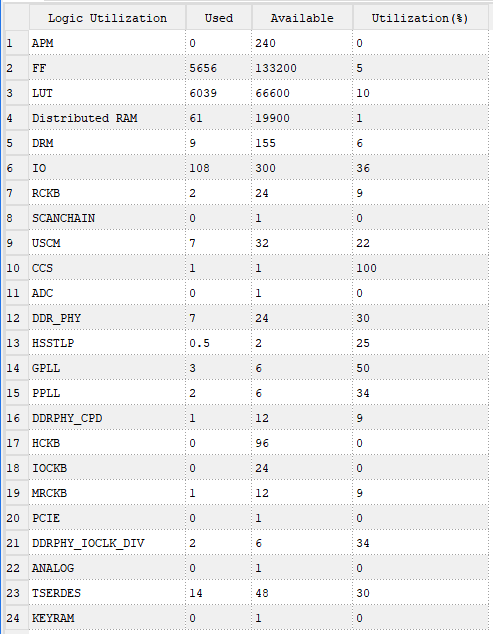

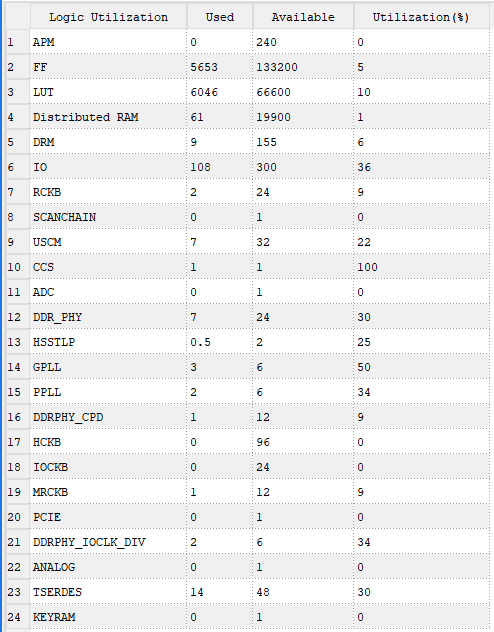

工程的资源消耗和功耗如下:

6、PDS工程源码3详解:点对点OV5640视频转SFP光口发送

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:OV5640摄像头或FPGA内部动态彩条,分辨率1280x720@30Hz;

输出:SFP光口,分辨率1280x720@30Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b编码;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

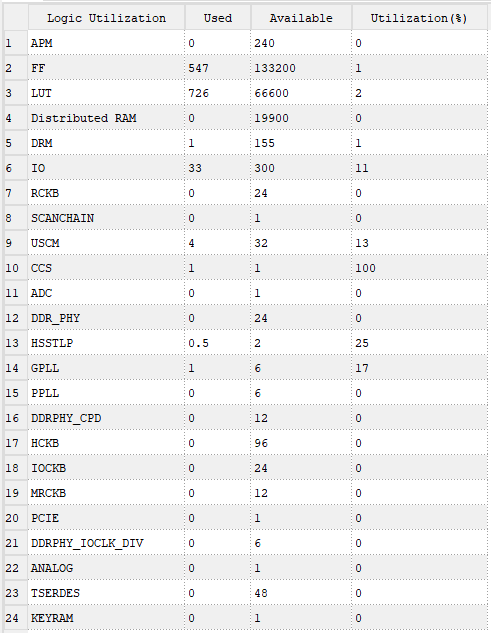

工程的资源消耗和功耗如下:

7、PDS工程源码4详解:点对点SFP光口接收OV5640视频转HDMI

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:SFP光口,分辨率1280x720@30Hz;

输出:HDMI,Silicom9134芯片编码,分辨率1280x720@60Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b解码;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

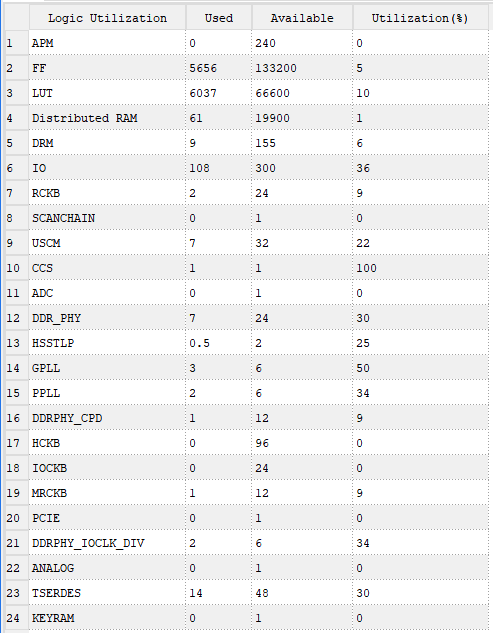

工程的资源消耗和功耗如下:

8、PDS工程源码5详解:点对点HDMI视频转SFP光口发送

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:HDMI或者FPGA内部动态彩条,silicom9011芯片解码方案,分辨率1920x1080@60Hz,笔记本电脑模拟输入源;

输出:SFP光口,分辨率1920x1080@30Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b编码;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

9、PDS工程源码6详解:点对点SFP光口接收HDMI视频转HDMI

开发板FPGA型号:紫光同创–PG2L100H-6EBG676;

开发环境:Pango Design Suite 2021.1

输入:SFP光口,分辨率1920x1080@60Hz;

输出:HDMI,Silicom9134芯片编码,分辨率1920x1080@60Hz;

高速接口类型:HSSTLP,线速率5Gbps;

高速接口编解码协议:8b/10b解码;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTLP光口视频点对点传输的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

7、上板调试验证并演示

准备工作

你需要有以下装备才能移植并测试该工程代码:

1:FPGA开发板;

2:OV7725或OV5640摄像头或笔记本电脑,没有则请使用FPGA内部生成的彩条;

3:HDMI传输线;

4:HDMI显示,要求分辨率支持1920x1080;

SFP光模块和光纤;

我的开发板了连接如下:

HSSTLP光口视频点对点传输效果演示

HSSTLP光口视频点对点传输效果演示如下:

紫光-SFP光口图传

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

紫光同创FPGA实现HSSTLP光口视频点对点传输,基于Aurora 8b/10b编解码架构,提供6套PDS工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目紫光同创FPGA相关方案推荐我这里已有的 GT 高速接口解决方案Xilinx系列FPGA实现GTP光口视频传输方案推荐Xilinx系列FPGA实现GTX光口视频传输方案推荐Xilinx系列FPGA实…...

)

正则表达式使用知识(日常翻阅)

正则表达式使用 一、字符匹配 1. 普通字符 描述:直接匹配字符本身。示例: abc 匹配字符串中的 “abc”。Hello 匹配字符串中的 “Hello”。 2. 特殊字符 .(点号): 描述:匹配任意单个字符(…...

学习笔记)

CSS padding(填充)学习笔记

CSS 中的 padding(填充)是一个非常重要的属性,它用于定义元素边框与元素内容之间的空间,即上下左右的内边距。合理使用 padding 可以让页面布局更加美观、清晰。以下是对 CSS padding 的详细学习笔记。 一、padding 的作用 padd…...

Python中的字符串、列表、字典和集合详解

Python是一门强大的编程语言,其内置的数据结构丰富多样。其中,字符串、列表、字典和集合是最常用的数据类型。本文将对它们的区别、用法和使用场景进行详细介绍,帮助大家更好地理解和应用这些数据结构。 1. 字符串(String…...

【CUDA编程】CUDA Warp 与 Warp-Python 对比文档

相关文档: Nvidia-Warp GitHub:nvidia/warp CUDA Warp 和 Warp-Python 库 的对比与统一文档,涵盖两者的核心概念、区别、使用场景及示例: 1. CUDA Warp(硬件/编程模型概念) 1.1 定义与核心概念 定义: C…...

中厂算法岗面试总结

时间:2025.4.10 地点:上市的电子有限公司 面试流程: 1.由负责人讲解公司文化 2,由技术人员讲解公司的技术岗位,还有成果 3.带领参观各个工作位置,还有场所 4.中午吃饭 5.面试题,闭卷考试…...

))

Losson 4 NFS(network file system(网络文件系统))

网络文件系统:在互联网中共享服务器中文件资源。 使用nfs服务需要安装:nfs-utils 以及 rpcbind nfs-utils : 提供nfs服务的程序 rpcbind :管理nfs所有进程端口号的程序 nfs的部署 1.客户端和服务端都安装nfs-utils和rpcbind #安装nfs的软件rpcbind和…...

自动化运行后BeautifulReport内容为空

一、问题描述 自动化程序运行后发现运行目录下生成的html报告文件内容为空,没有运行结果。 二、测试环境 操作系统:Windows 11 家庭版BeautifulReport:0.1.3Python:3.11.9Appium-Python-Client:5.0.0Appium Server:2.…...

CTF-WEB排行榜制作

CTF-WEB排行榜制作 项目需求: 现在14道题对应有14个flag,我需要使用dockerfile搭建一个简单的,能够实现验证这些题目对应的flag来计分的简单网站(要求页面比较精美) 前十题设置为10分 11-14题设置为20分 1. flag{5a3…...

)

架构生命周期(高软57)

系列文章目录 架构生命周期 文章目录 系列文章目录前言一、软件架构是什么?二、软件架构的内容三、软件设计阶段四、构件总结 前言 本节讲明架构设计的架构生命周期概念。 一、软件架构是什么? 二、软件架构的内容 三、软件设计阶段 四、构件 总结 就…...

STM32单片机定时器的输入捕获和输出比较

目录 一、定时器的输入捕获 1、工作原理 2、示例代码 二、定时器的输出比较 1、工作原理 2、示例代码 三、总结 在STM32单片机中,定时器是一个非常重要的外设,广泛应用于时间管理、事件计时、波形生成等多种场景。其中输入捕获和输出比较是两个基…...

计算机组成原理-系统总线

1. 系统总线的定义 系统总线是计算机系统中各功能部件(CPU、存储器、I/O设备等)之间传递信息的公共通路,遵循统一的电气规范和时序协议,是计算机硬件互联的基础。 核心作用:实现数据、地址和控制信号的传输ÿ…...

【android bluetooth 框架分析 02】【Module详解 3】【HciHal 模块介绍】

1. 背景 我们在 gd_shim_module 介绍章节中,看到 我们将 HciHal 模块加入到了 modules 中。 modules.add<hal::HciHal>();在 ModuleRegistry::Start 函数中我们对 加入的所有 module 挨个初始化。 而在该函数中启动一个 module 都要执行那下面几步ÿ…...

Git 远程仓库

Git 入门笔记 远程仓库 Git 远程仓库 Git 远程仓库是一个托管在网络服务器上的代码仓库,它是团队协作开发的核心。 通过远程仓库,开发者可以共享代码、同步更新,实现分布式协作。 SSH 密钥 SSH 密钥可以让你在使用 Git 时安全地连接远程…...

)

209.长度最小的子数组- 力扣(LeetCode)

题目: 给定一个含有 n 个正整数的数组和一个正整数 target 。 找出该数组中满足其总和大于等于 target 的长度最小的 子数组 [numsl, numsl1, ..., numsr-1, numsr] ,并返回其长度。如果不存在符合条件的子数组,返回 0 。 示例 1:…...

符号右移“ >>= “ 与 无符号右移“ >>>= “ 的区别

符号右移" >> " 与 无符号右移" >>> " 的区别 一、符号右移" >> " 与 无符号右移" >>> " 的区别1. 符号右移(>>)与无符号右移(>>>)的区别…...

山东大学软件学院项目实训-基于大模型的模拟面试系统-专栏管理部分

本周我的主要任务是关于专栏管理部分的完善。 专栏图片的显示问题 问题分析 根据代码可知:图片URL来自于portfolio.headImgUrl,而且如果URL不存在的话,应该显示的是无图片,而网页中显示加载失败说明portfolio.headImgUrl应该是存…...

从 SYN Flood 到 XSS:常见网络攻击类型、区别及防御要点

常见的网络攻击类型 SYN Flood、DoS(Denial of Service) 和 DDoS(Distributed Denial of Service) 是常见的网络攻击类型,它们的目标都是使目标系统无法正常提供服务。以下是它们的详细说明: 1. SYN Flood…...

ros2-rviz2控制unity仿真的6关节机械臂,探索从仿真到实际应用的过程

文章目录 前言(Introduction)搭建开发环境(Setup Development Environment)在window中安装Unity(Install Unity in window)创建Docker容器,并安装相关软件(Create Docker containers…...

01_通过调过api文字生成音频示例

第1 第2 第3,测试音色 第4 第5 第6 第7生成api_key 第8代码 import requestsurl "https://api.siliconflow.cn/v1/audio/speech"payload {"input": "在中国传统文化中,谦让被视为一种美德,但过度的让步…...

使用PyTorch实现目标检测边界框转换与可视化

一、引言 在目标检测任务中,边界框(Bounding Box)的坐标表示与转换是核心基础操作。本文将演示如何: 实现边界框的两种表示形式(角点坐标 vs 中心坐标)之间的转换 使用Matplotlib在图像上可视化边界框 验…...

— ARM32通过u-boot 启动Linux)

QEMU学习之路(8)— ARM32通过u-boot 启动Linux

QEMU学习之路(8)— ARM32通过u-boot 启动Linux 一、前言 参考文章: Linux内核学习——内核的编译和启动 Linux 内核的编译和模拟执行 Linux内核运行——根文件系统 Linux 内核学习——使用 uboot 加载内核 二、构建Linux内核 1、获取Linu…...

flutter 桌面应用之右键菜单

在 Flutter 桌面应用开发中,context_menu 和 contextual_menu 是两款常用的右键菜单插件,各有特色。以下是对它们的对比分析: 🧩 context_menu 集成方式:通过 ContextMenuArea 组件包裹目标组件,定义…...

、什么是静态资源、负载均衡(Nginx)、canal、主从复制)

系统设计面试总结:高性能相关:CDN(内容分发网络)、什么是静态资源、负载均衡(Nginx)、canal、主从复制

以下为本人自学回顾使用,请支持javaGuide原版。 1.CDN概述 CDN 就是将静态资源分发到多个不同的地方以实现就近访问,进而加快静态资源的访问速度,减轻服务器以及带宽的负担。 你可以将 CDN 看作是服务上一层的特殊缓存服务,分布…...

)

从红黑树到哈希表:原理对比与典型场景应用解析(分布式以及布隆过滤器)

在数据结构的世界里,红黑树一直以「自平衡二叉查找树」的身份备受赞誉。凭借红黑节点的精妙设计,它能将插入、删除、查找的时间复杂度稳定控制在 ( log n ) (\log n) (logn),成为处理有序数据的经典方案。然而,当业务场景对「…...

动手学深度学习:手语视频在VGG模型中的测试

前言 其他所有部分同上一篇AlexNet一样,所以就不再赘诉,直接看VGG搭建部分。 模型 VGG是第一个采取块进行模块化搭建的模型。 def vgg_block(num_convs,in_channels,out_channels):layers[]for _ in range(num_convs):layers.append(nn.Conv2d(in_ch…...

微信小程序实战案例 - 餐馆点餐系统 阶段 4 - 订单列表 状态

✅ 阶段 4 – 订单列表 & 状态 目标 展示用户「我的订单」列表支持状态筛选(全部 / 待处理 / 已完成)支持分页加载和实时刷新使用原生组件编写 ✅ 1. 页面结构:文件结构 pages/orders/├─ index.json├─ index.wxml├─ index.js└─…...

深度学习理论-直观理解 Attention

本文首先介绍 Attention 的原始公式,然后以 Self-Attention 为例,简化后逐步分析 Attention 计算结果表达的含义 Attention Attention 公式如下: A t t e n t i o n s o f t m a x ( Q ⋅ K T d k ) ⋅ V Attention softmax(\frac{Q \cd…...

python中 “with” 关键字的取舍问题

自动管理资源(自动关闭文件) 当你使用 with 打开文件时,文件会在 with 代码块结束后自动关闭,无论是否发生异常。这意味着你不需要显式地调用 f.close() 来关闭文件 示例: with open("words.txt", "r…...

)

ISIS协议(动态路由协议)

ISIS基础 基本概念 IS-IS(Intermediate System to Intermediate System,中间系统到中间系统)是ISO (International Organization for Standardization,国际标准化组织)为它的CLNP(ConnectionL…...

llm开发框架新秀

原文链接:https://i68.ltd/notes/posts/20250404-llm-framework3/ google开源ADK-Agent Development Kit 开源的、代码优先的 Python 工具包,用于构建、评估和部署具有灵活性和控制力的复杂智能体项目仓库:https://github.com/google/adk-python 2.6k项目文档:Age…...

Zookeeper的典型应用场景?

大家好,我是锋哥。今天分享关于【Zookeeper的典型应用场景?】面试题。希望对大家有帮助; Zookeeper的典型应用场景? 1000道 互联网大厂Java工程师 精选面试题-Java资源分享网 ZooKeeper 是一个开源的分布式协调服务,主要用于管理和协调大…...

【C数据结构】 TAILQ双向有尾链表的详解

TAILQ双向有尾链表的详解 常见的链表结构1.SLIST2.STAILQ3.LIST4.TAILQ5.CIRCLEQ 一、TAILQ链表简介二、TAILQ的定义和声明三、TAILQ队列的函数1.链表头的初始化2.获取第一个节点地址3.获取最后一个节点地址4.链表是否为空5.下一个节点地址6.上一个节点地址7.插入头节点8.插入尾…...

redisson的unlock方法

//分布式方式,分布式锁,采用redisson锁 RLock lock redissonClient.getLock(userId.toString());//lock方法会无限重试。getLock底层是hash,大key是userid,小key是线程,value是重入次数 try {//boolean b lock.tryLo…...

ffmpeg 切割视频失败 ffmpeg 命令参数 -vbsf 在新版本中已经被弃用,需要使用 -bsf:v 替代

ffmpeg 切割视频失败 ffmpeg 命令参数 -vbsf 在新版本中已经被弃用,需要使用 -bsf:v 替代 从日志中可以看到问题出在第一个 ffmpeg 命令执行时: Unrecognized option vbsf.Error splitting the argument list: Option not found这是因为 ffmpeg 命令参…...

设计模式——抽象工厂模式总结

理解了前面的工厂模式后,再理解抽象工厂模式就很容易了。 工厂模式:https://blog.csdn.net/inside802/article/details/147170118?spm1011.2415.3001.10575&sharefrommp_manage_link 抽象工厂模式就是工厂模式的更加抽象化,父类不仅不承…...

JavaScript 定时器

在 JavaScript 中,定时器是实现代码在特定时间间隔执行或延迟执行的重要工具。下面我们将深入探讨定时器的相关知识。 定时器基础 setTimeout() setTimeout() 函数用于在指定的延迟时间后执行一次回调函数。它接受两个参数,第一个参数是要执行的回调函…...

企业经营决策风险

在企业的经营过程中,领导者每天都在面对大量的决策——该扩大生产还是收缩业务?该增设销售渠道还是提升产品质量?但你知道吗,企业最大的成本,不是生产成本,也不是人工成本,而是决策错误的成本&a…...

【云安全】云原生-centos7搭建/安装/部署k8s1.23.6单节点

一、节点基本配置 1、准备操作系统 2、 修改主机名 hostnamectl set-hostname master-1 hostnamectl set-hostname node1 hostnamectl set-hostname node2#验证hostnamectl status 3、修改/etc/hosts cat <<EOF >>/etc/hosts 192.168.255.137 master-1 192.168…...

【已更新完毕】2025泰迪杯数据挖掘竞赛B题数学建模思路代码文章教学:基于穿戴装备的身体活动监测

基于穿戴装备的身体活动监测 摘要 本研究基于加速度计采集的活动数据,旨在分析和统计100名志愿者在不同身体活动类别下的时长分布。通过对加速度数据的处理,活动被划分为睡眠、静态活动、低强度、中等强度和高强度五类,进而计算每个志愿者在…...

)

力扣每日打卡 1922. 统计好数字的数目 (中等)

力扣 1922. 统计好数字的数目 中等 前言一、题目内容二、解题方法1. 暴力解法(会超时,此法不通)2. 快速幂运算3. 组合计数的思维逻辑分析组合计数的推导例子分析思维小结论 4.官方题解4.1 方法一:快速幂 三、快速幂运算快速幂运算…...

)

宝塔Linux面板 - 添加站点建站时没有域名实现 IP 地址访问测试(宝塔面板建站 IP 访问)

前言 使用面板添加站点时,必须要填写一个域名用来指向程序,没有域名怎么办? 答案:域名直接写 【服务器 IP 地址】 操作步骤 如果还没有添加站点,则直接在创建站点的时候,域名那填写服务器地址即可&#…...

【GitHub探索】mcp-go,MCP协议的Golang-SDK

近期大模型Agent应用开发方面,MCP的概念比较流行,基于MCP的ToolServer能力开发也逐渐成为主流趋势。由于笔者工作原因,主力是Go语言,为了调研大模型应用开发,也接触到了mcp-go这套MCP的SDK实现。 对于企业内部而言&am…...

手撕TCP内网穿透及配置树莓派

注意: 本文内容于 2025-04-13 15:09:48 创建,可能不会在此平台上进行更新。如果您希望查看最新版本或更多相关内容,请访问原文地址:手撕TCP内网穿透及配置树莓派。感谢您的关注与支持! 之前入手了树莓派5,…...

人形机器人运动与操作: 控制、规划和学习方面的当前进展与挑战

前言 图 1:执行运动和操作任务的人形机器人:(a)HRP-4 在适应地形的同时擦拭木板[1];(b-g)Digit、Hector[2]、Atlas、H1、Justin[3]和 Apollo 取放物体;(h)iCu…...

C++ 重构muduo网络库

本项目参考的陈硕老师的思想 1. 基础概念 进程里有 Reactor、Acceptor、Handler 这三个对象 Reactor 对象的作用是监听和分发事件;Acceptor 对象的作用是获取连接;Handler 对象的作用是处理业务; 先说说 阻塞I/O,非阻塞I/O&…...

大学校园网综合项目设计)

【计算机网络实践】(十二)大学校园网综合项目设计

本系列包含: (一)以太网帧分析与网际互联协议报文结构分析 (二)地址解析协议分析与传输控制协议特性分析 (三)交换机的基本操作、配置、 虚拟局域网配置和应用 (四)交…...

通过api程序的方式编辑ps的三种方式

目前只使用了第一种 ps-python-api去操作 还没有尝试其他两种方式对于第一种方式必须要开启ps程序,程序调用修改新增图层和文档时会同步到ps页面,可以直观看到修改结果...

论文阅读笔记——Reactive Diffusion Policy

RDP 论文 通过 AR 提供实时触觉/力反馈;慢速扩散策略,用于预测低频潜在空间中的高层动作分块;快速非对称分词器实现闭环反馈控制。 ACT、 π 0 \pi_0 π0 采取了动作分块,在动作分块执行期间处于开环状态,无法及时响…...

MySQL表的增删改查进阶版

Mysql 1、数据库的约束1.1约束类型1.2 NULL约束1.3 UNIQUE:唯一约束1.4 DEFAULT:默认值约束1.5 PRIMARY KEY:主键约束(重点)1.6 FOREIGN KEY:外键约束(重点) 2.表的设计2.1一对一2.2…...