Quartus II的IP核调用及仿真测试

目录

- 第一章 什么是IP核?

- 第二章 什么是LPM?

- 第一节 设置LPM_COUNTER模块参数

- 第二节 仿真

- 第三章 什么是PLL?

- 第一节 设置ALTPLL(嵌入式锁相环)模块参数

- 第二节 仿真

- 第四章 什么是RAM?

- 第一节 RAM_1PORT的调用

- 第二节 配置RAM_1PORT

- 第三节 RAM_2PORT的调用

- 第四节 配置RAM_2PORT

- 第五章 什么是FIFO?

- 第一节 FIFO模块参数配置

- 第二节 配置FIFO

- 参考文献

第一章 什么是IP核?

IP核就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品——掩膜。[1]

第二章 什么是LPM?

LPM即参数化模块库(Library of Parameterized Modules),是Altera 公司FPGA/CPLD设计软件Quartus II自带的一些宏功能模块,如:锁相环(PLLs), LVDS,数字信号处理(DSP) 模块等。这些功能是对Altera器件的优化,设计者在用这些模块时,不耗用器件的逻辑资源(Logic Cell)。[2]

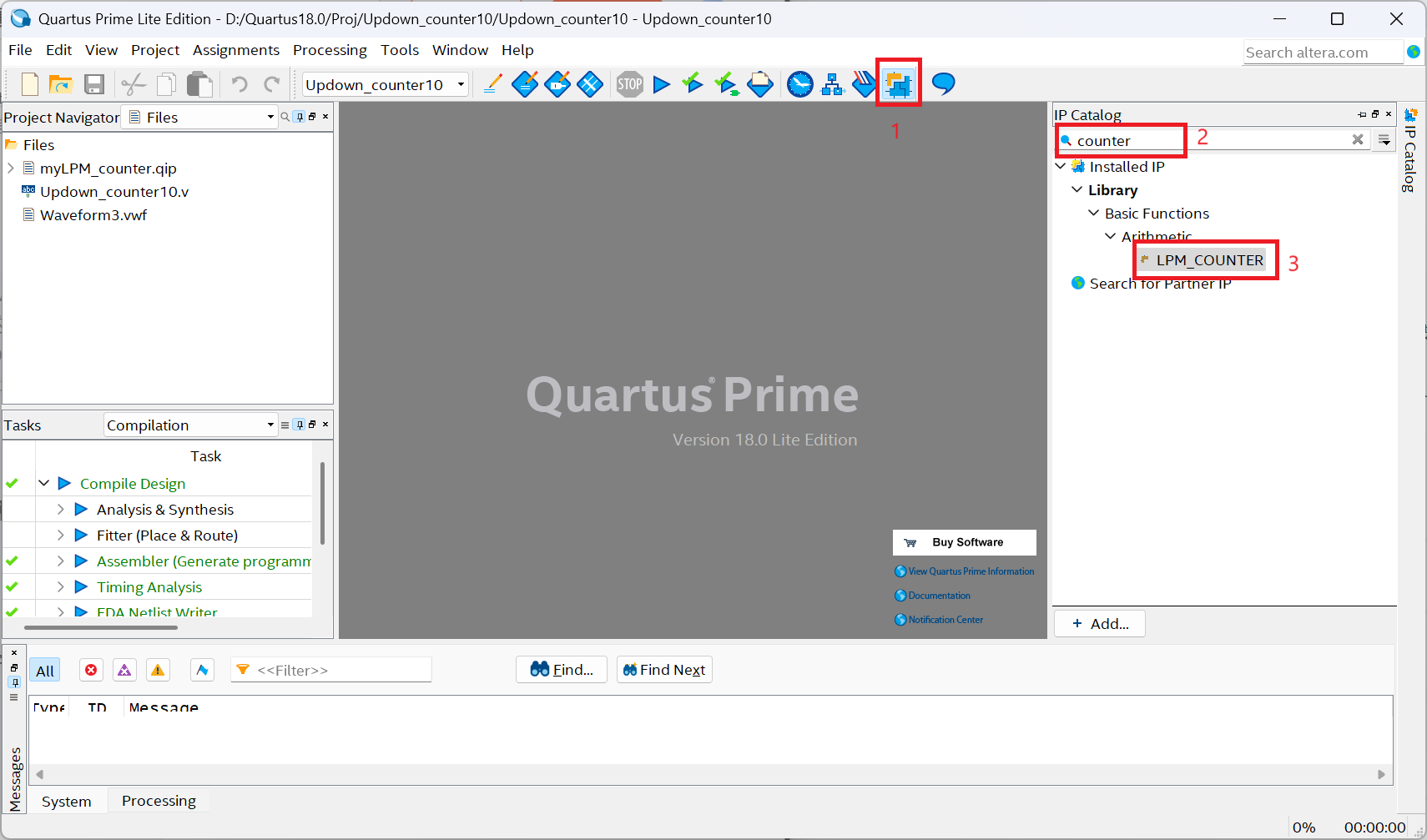

第一节 设置LPM_COUNTER模块参数

-

新建项目,点击

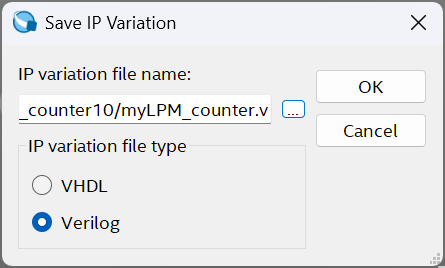

IP Catalog,在搜索框内输入counter,点击LPM_COUNTER,然后将其保存为myLPM_counter.v,点击Ok开始配置

-

基础设置

-

设置输入并点击NEXT。

-

多次点击NEXT,出现如下界面后选择需要文件,点击Finish完成配置,在弹出界面点击Yes

第二节 仿真

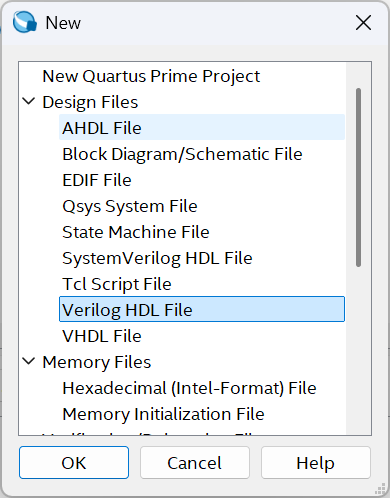

- 新建Verilog HDL File,然后写入代码,生成需要的模型,将其保存为

Updown_counter10.v

module Updown_counter10 (aclr,cp_en,cp,updown,co,q);input aclr;input cp_en;input cp;input updown;output co;output [3:0] q;myLPM_counter myLPM_counter_inst(.aclr(aclr),.clk_en(cp_en),.clock(cp),.updown(updown),.cout(co),.q (q));

endmodule

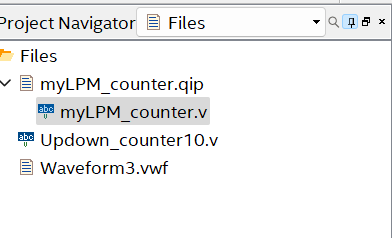

文件目录如下

- 设置LPM_COUNTER,修改

myLPM_counter.qip文件下的myLPM_counter.v,使其符合期望

`timescale 1 ps / 1 ps

module myLPM_counter (aclr,clk_en,clock,sclr,updown,cout,q);input aclr;input clk_en;input clock;input sclr;input updown;output cout;output [3:0] q;wire sub_wire0;wire [3:0] sub_wire1;wire cout = sub_wire0;wire [3:0] q = sub_wire1[3:0];lpm_counter LPM_COUNTER_component (.clk_en (clk_en),.clock (clock),

// .sclr (sclr),.updown (updown),.cout (sub_wire0),.q (sub_wire1),.aclr (1'b0),.aload (1'b0),.aset (1'b0),.cin (1'b1),.cnt_en (1'b1),.data ({4{1'b0}}),.eq (),.sclr(1'b0),.sload (1'b0),.sset (1'b0));defparamLPM_COUNTER_component.lpm_direction = "UNUSED",LPM_COUNTER_component.lpm_modulus = 10,LPM_COUNTER_component.lpm_port_updown = "PORT_USED",LPM_COUNTER_component.lpm_type = "LPM_COUNTER",LPM_COUNTER_component.lpm_width = 4;

endmodule

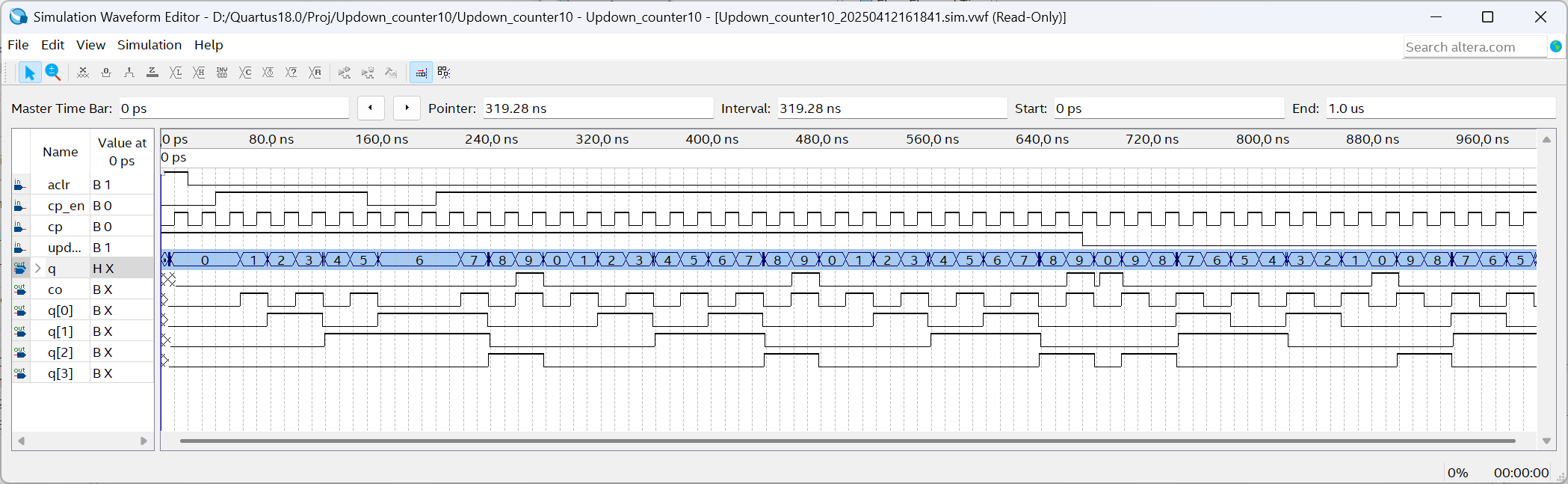

- 开始完整编译,编译通过后,新建

University Program VWF进行仿真

- 仿真

观察仿真结果发现,结果与预期相同

第三章 什么是PLL?

PLL即锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。根据自动控制原理,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。[3]

第一节 设置ALTPLL(嵌入式锁相环)模块参数

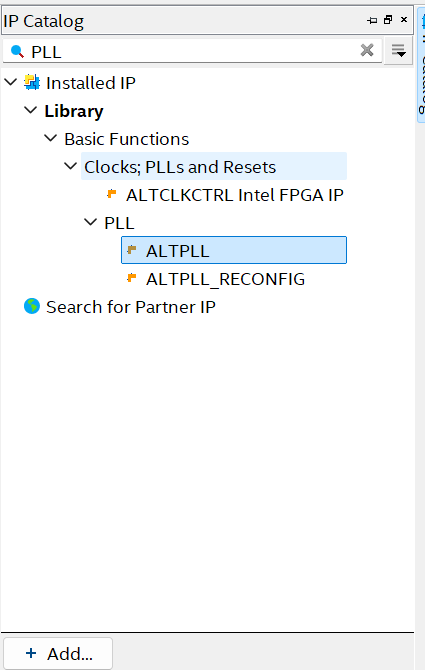

-

选择ALTPLL,与第二章第一节相同的处理方法,在IP Catalog中搜索

PLL,选择ALTPLL在点击左下角的Add按钮将其保存为mypll.v文件并开始配置

-

根据选择的芯片设置合适的晶振,ep4ce115f29c7的晶振为50MHZ,使用时钟频率选择50MHZ,模式为正常

-

以下配置默认即可

-

设置时钟

c0:设置100MHZ,将时钟倍频,占空比设置50%

c1:25MHZ,选择分频,且相位偏移90°,占空比50%

c2:5MHZ,占空比为25%

c3:先分频再倍频,75MHZ,占空比50%

目前只选择4个时钟,第5个时钟不启用 -

多次点击next,直到出现此界面,勾选

mypll_inst.v文件和mypll_bb.v文件

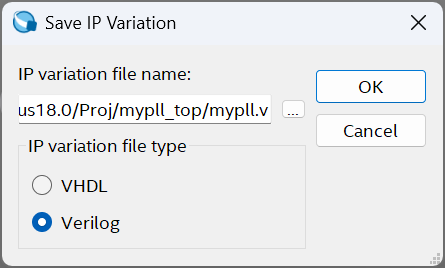

第二节 仿真

- 新建

Verilog HDL File,写入下面的模型代码,保存为test_IP.v

module test_IP(input clk , // 时钟信号input rst_n , // 上电复位低有效output c0 ,output c1 ,output c2 ,output c3 ,output locked

);// PLL

mypll mypll_inst (.areset ( ~rst_n ), // IP复位高有效.inclk0 ( clk ), // 输入时钟.c0 ( c0 ), // 输出时钟.c1 ( c1 ), // 输出时钟.c2 ( c2 ), // 输出时钟.c3 ( c3 ), // 输出时钟.locked ( locked ) // 时钟输出锁--锁定不稳定时钟输出

);endmodule以及测试代码test_tb.v

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;wire c0 ;wire c1 ;wire c2 ;wire c3 ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.c0 (c0 ),.c1 (c1 ),.c2 (c2 ),.c3 (c3 ),.locked (locked )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位#200;rst_n = 1'b1;#20000;$stop;

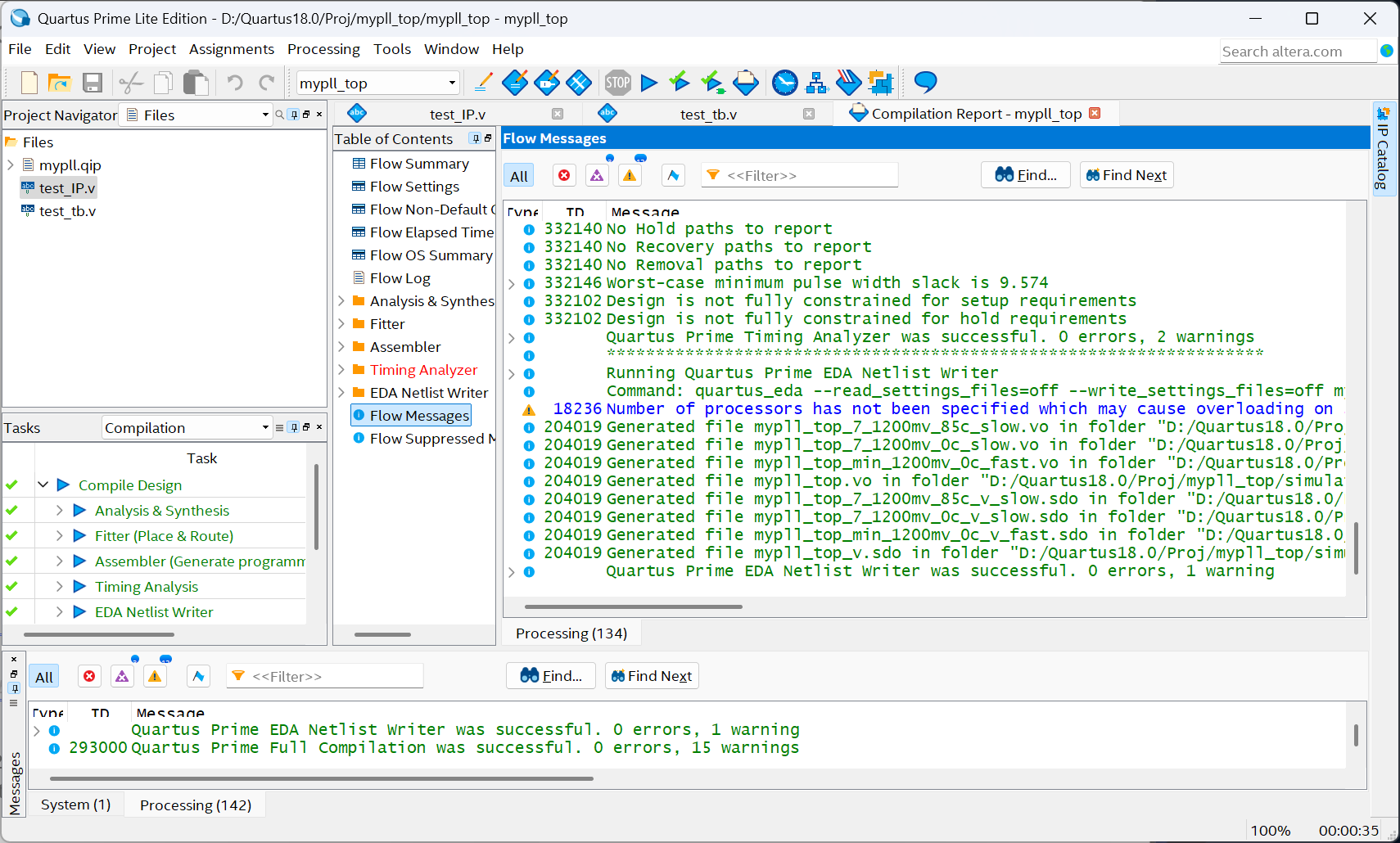

endendmodule- 进行完整编译,编译通过后开始仿真

- 仿真

观察仿真结果发现与预期相同

第四章 什么是RAM?

RAM即随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。[4]

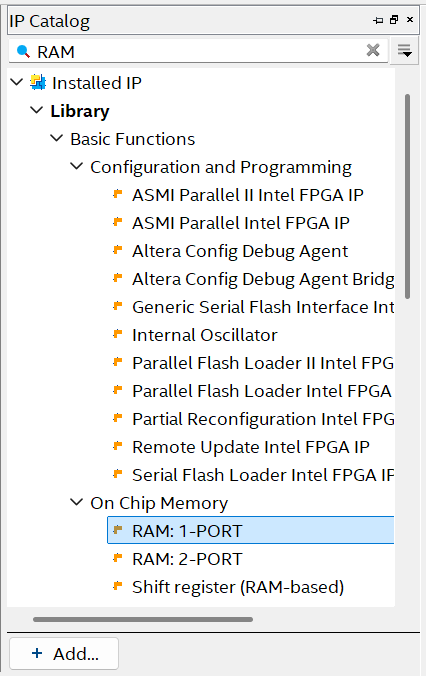

第一节 RAM_1PORT的调用

-

搜索

RAM选择RAM_1PORT并添加保存为RAM_1PORT.v

-

设置位宽和数据深度

-

多次点击NEXT直到出现此界面,并勾选

RAM_1PORT_inst.v和RAM_1PORT_bb.v

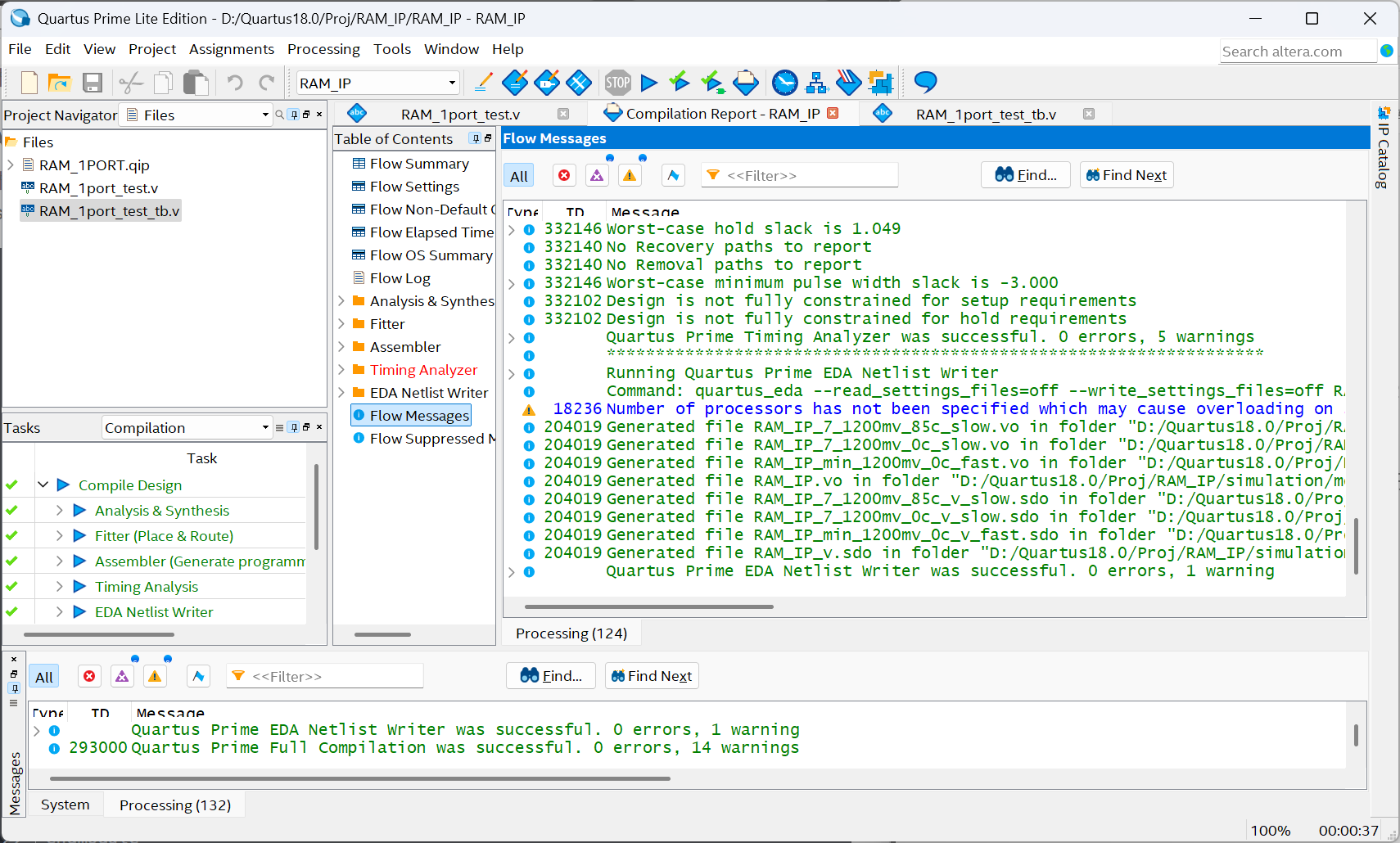

第二节 配置RAM_1PORT

- 新建Verilog HDL File,写入模型的代码

module RAM_1port_test(input clk ,//时钟信号input rst_n ,//上电复位低有效input rden ,input wren ,input [7:0] address ,input [7:0] data ,output [7:0] q

);//RAM_1portRAM_1PORT RAM_1PORT_inst (.aclr ( ~rst_n ),.address ( address ),.clock ( clk ),.data ( data ),.rden ( rden ),.wren ( wren ),.q ( q ));

endmodule以及测试的代码

`timescale 1ns/1ps

module RAM_1port_test_tb();reg clk ;reg rst_n ;reg rden ;reg wren ;reg [7:0] address ;reg [7:0] data ;wire [7:0] q ;//例化要仿真的文件

RAM_1port_test u_RAM_1port_test(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.rden (rden ),.wren (wren ),.address (address ),.data (data ),.q (q )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位

//RAM_1PORTwren = 1'b0;//复位有效,赋初值rden = 1'b0;data = 0;address = 0;#200;rst_n = 1'b1;#200;//wren 50Mfor(i=0;i<256;i=i+1)beginwren = 1'b1;//高电平有效address = i;data = i+1;#20;endwren = 1'b0;//写完拉低#100;//rden 100Mfor(j=0;j<256;j=j+1)beginrden = 1'b1;address = j;#20;endrden = 1'b0;//读完拉低#200;$stop;

endendmodule- 完全编译

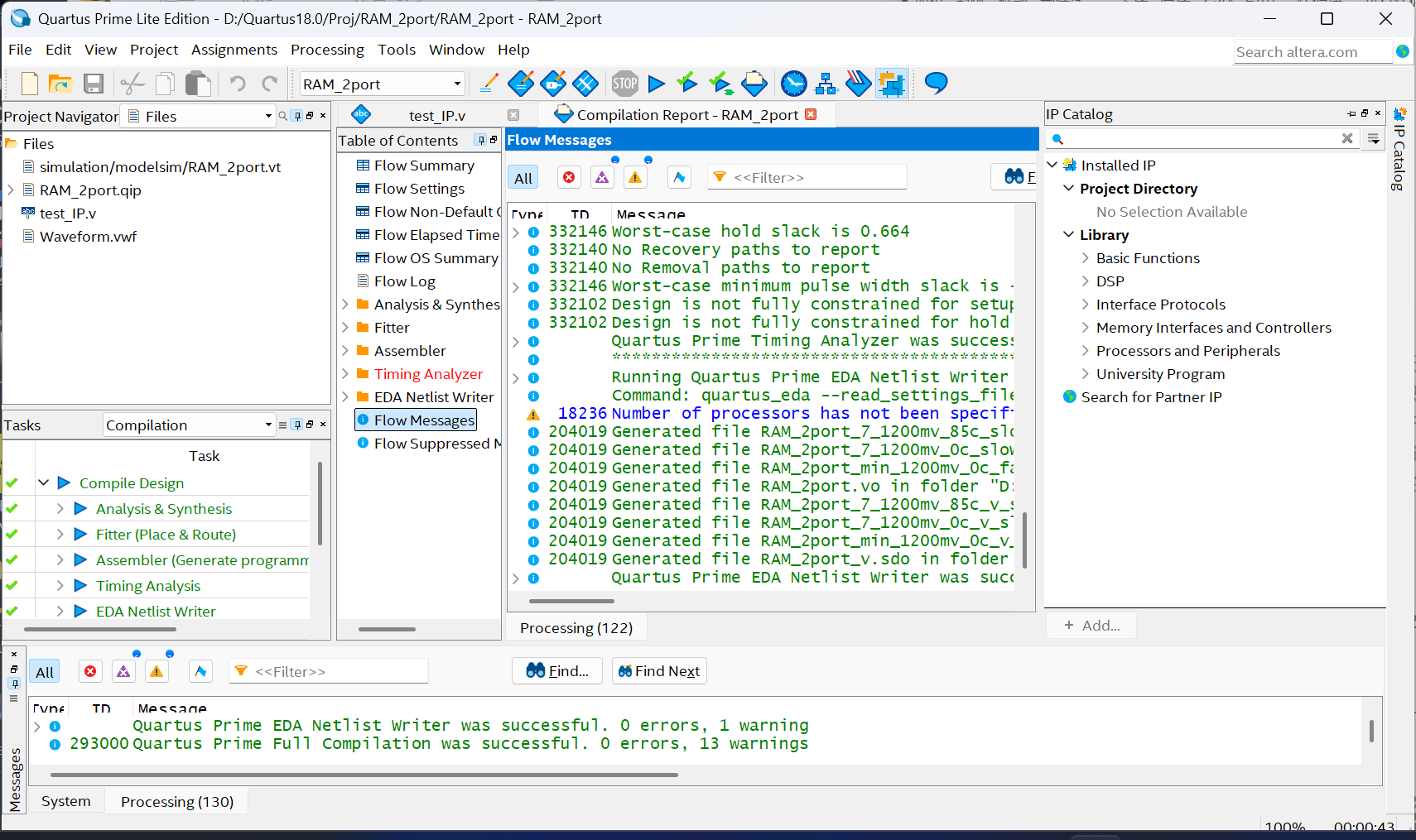

第三节 RAM_2PORT的调用

- 同样,找到RAM_2PORT并添加,保存为

RAM_2port.v

- 配置读写模块

- 配置数据深度为1024

- 选择读写时钟分开

- 读出数据设置为q,同样选择复位清零

- 多次点击next直到出现此界面,选择

RAM_2port_inst.v及RAM_2port_bb.v

第四节 配置RAM_2PORT

- 同样编译模型代码和测试代码

test_IP.v

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input [7:0] data ,input [7:0] rdaddress ,input rden ,input [7:0] wraddress ,input wrclock ,input wren ,output [7:0] q);// //RAM_2portRAM_2port RAM_2port_inst (.data ( data ),.rd_aclr ( ~rst_n ),.rdaddress ( rdaddress ),.rdclock ( clk ),.rden ( rden ),.wraddress ( wraddress ),.wrclock ( wrclock ),.wren ( wren ),.q ( q ));endmodule测试代码test_tb.v

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;reg [7:0] data ;reg [7:0] rdaddress ;reg rden ;reg [7:0] wraddress ;reg wrclock ;reg wren ;wire [7:0] q ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.data (data ),.rdaddress (rdaddress ),.rden (rden ),.wraddress (wraddress ),.wrclock (clk ),.wren (wren ),.q (q )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位wren = 1'b0;//复位有效,赋初值rden = 1'b0;rdaddress = 0;wraddress = 0;data = 0;#200;rst_n = 1'b1;#200;//wren 50Mfor(i=0;i<256;i=i+1)beginwren = 1'b1;//高电平有效wraddress = i;data = i+1;#20;endwren = 1'b0;//写完拉低#100;//rden 100Mfor(j=0;j<256;j=j+1)beginrden = 1'b1;rdaddress = j;#20;endrden = 1'b0;//读完拉低#200;$stop;

endendmodule- 完整编译通过

第五章 什么是FIFO?

FIFO( First Input First Output)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采集、高速数据处理、高速数据传输以及多机处理系统中得到越来越广泛的应用。[5]

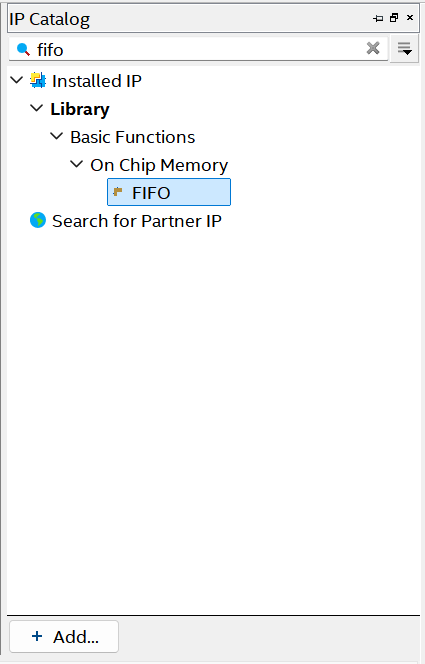

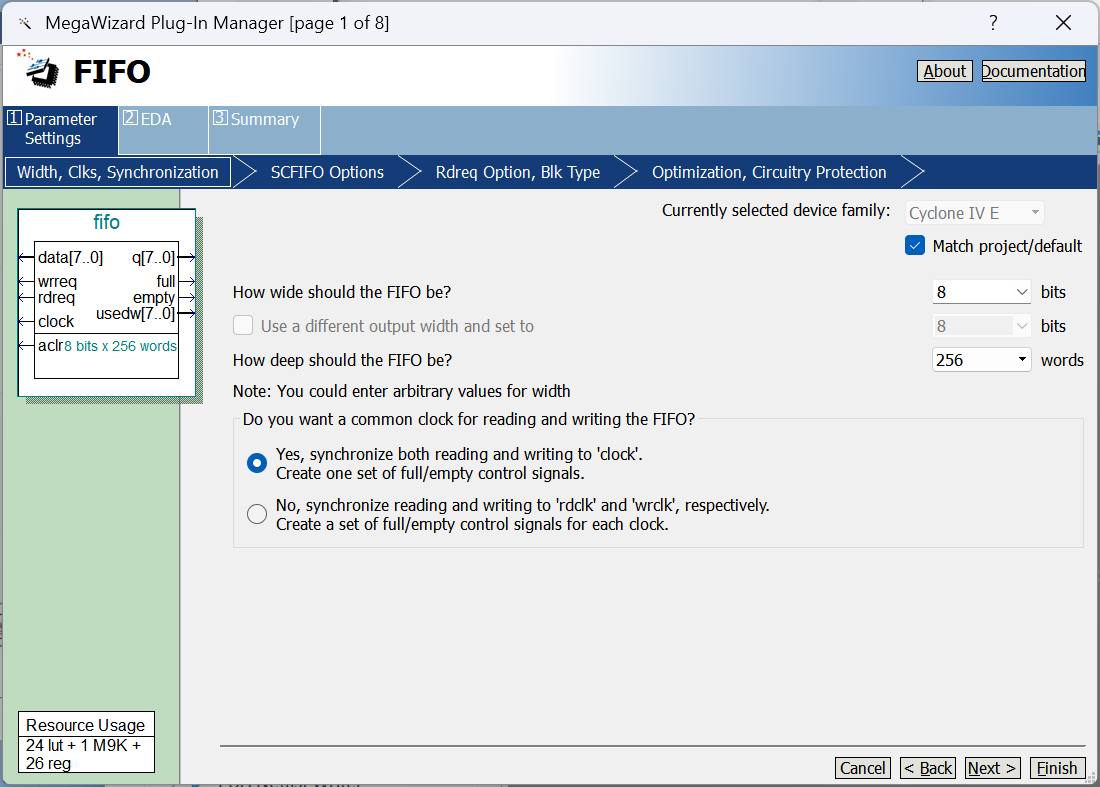

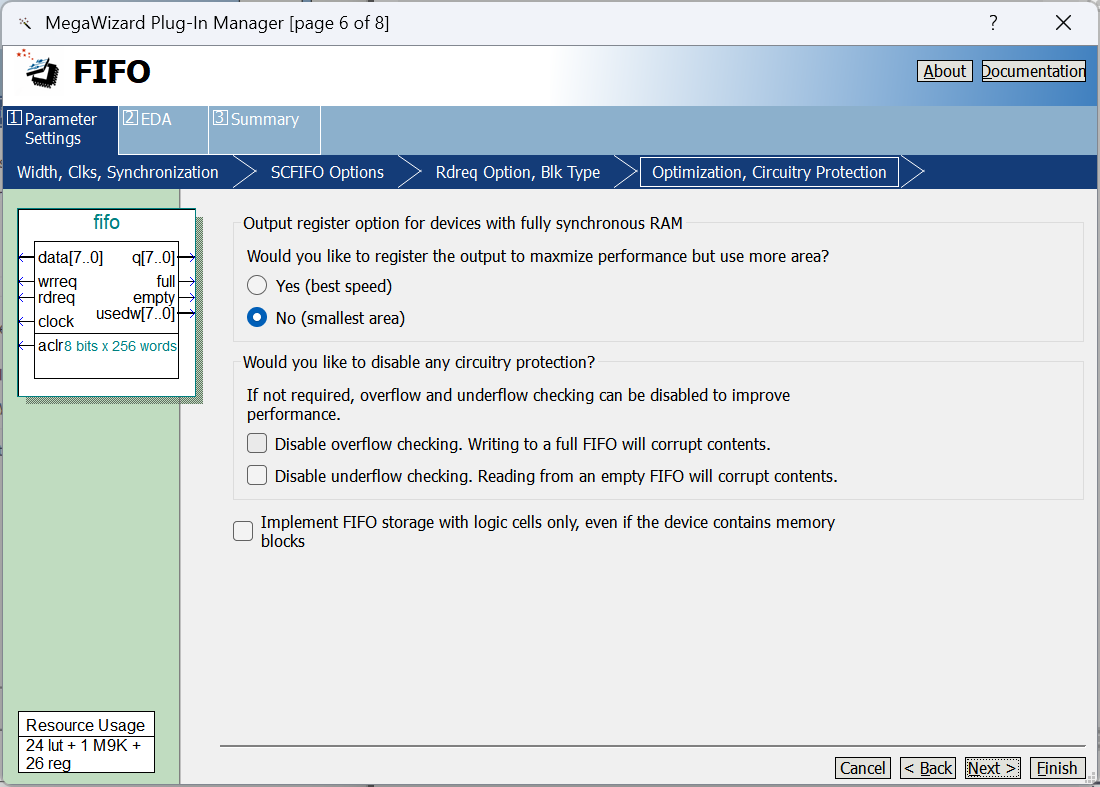

第一节 FIFO模块参数配置

1.在IP Catelog搜索FIFO,选择FIFO并添加,保存为fifo.v

- 选择读写使用同一个时钟

- 配置SCFIFO

- 默认即可,点击next

- 默认即可

- 勾选

fifo_inst.v和fifo_bb.v

第二节 配置FIFO

- 与前面相同,新建Verilog HDL File,写入如下代码并保存

模型代码:

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input [7:0] data ,input rdreq ,input wrreq ,output empty ,output full ,output [7:0] q ,output [7:0] usedw );// //FIFOfifo fifo_inst (.aclr ( ~rst_n ),.clock ( clk ),.data ( data ),.rdreq ( rdreq ),.wrreq ( wrreq ),.empty ( empty ),.full ( full ),.q ( q ),.usedw ( usedw ));

endmodule测试代码:

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;reg wrreq ;reg rdreq ;reg [7:0] data ;wire [7:0] q ;wire empty ;wire full ;wire usedw ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.data (data ),.rdreq (rdreq ),.wrreq (wrreq ),.empty (empty ), .full (full ), .q (q ), .usedw (usedw )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位rdreq = 1'b0;wrreq = 1'b0;data = 0;#200;rst_n = 1'b1;#200;//wrreq 50Mfor(i=0;i<256;i=i+1)beginwrreq = 1'b1;//高电平有效data = {$random};#20;endwrreq = 1'b0;//写完拉低#100;//rdreq 100Mfor(j=0;j<256;j=j+1)beginrdreq = 1'b1;#20;endrdreq = 1'b0;#200;$stop;

endendmodule- 全部编译通过

参考文献

[1] 潘松·EDA技术与Verilog HDL·北京:清华大学出版社,2010

[2] LPM(FPGA参数化模块库) -百度百科

[3] 锁相环(无线电术语)-百度百科

[4] 杨颂华,冯毛官,孙万蓉,初秀琴,胡力山编著·数字电子技术基础:西安电子科技大学出版社,2016.07

[5] FIFO存储器 -百度百科

[6] Quartus基本IP核调用及仿真

[7] 罗杰.Verilog HDL 与FPGA数字系统设计 第二版[M].机械工业出版社:北京,2022:198-210.

相关文章:

Quartus II的IP核调用及仿真测试

目录 第一章 什么是IP核?第二章 什么是LPM?第一节 设置LPM_COUNTER模块参数第二节 仿真 第三章 什么是PLL?第一节 设置ALTPLL(嵌入式锁相环)模块参数第二节 仿真 第四章 什么是RAM?第一节 RAM_1PORT的调用第…...

如何修改服务器TTL值

Windows默认返回的TTL值为128,Linux为64,我们怎么修改这个值呢? 目录 一. Windows 二. Linux 临时更改 永久更改 一. Windows WinR输入regedit,打开注册表 路径:计算机\HKEY_LOCAL_MACHINE\SYSTEM\CurrentContro…...

大模型LLM表格报表分析:markitdown文件转markdown,大模型markdown统计分析

整体流程:用markitdown工具文件转markdown,然后大模型markdown统计分析 markitdown https://github.com/microsoft/markitdown 在线体验:https://huggingface.co/spaces/AlirezaF138/Markitdown 安装: pip install markitdown…...

劫持SUID程序提权彻底理解Dirty_Pipe:从源码解析到内核调试

DirtyPipe(CVE-2022-0847)漏洞内核调试全流程指南 本文主要面向对内核漏洞挖掘与调试没有经验的初学者,结合 CVE-2022-0847——著名的 Dirty Pipe 漏洞,带你从零开始学习 Linux 内核调试、漏洞复现、原理分析与漏洞利用。该漏洞危害极大,并且概念简单明了,无需复杂前置知…...

React 组件样式

在这里插入图片描述 分为行内和css文件控制 行内 通过CSS中类名文件控制...

嵌入式人工智能应用-第三章 opencv操作3 图像平滑操作 下

5 高斯噪声(Gaussian Noise) 高斯噪声(Gaussian Noise)是一种符合正态(高斯)分布的随机噪声,广泛存在于传感器采集、信号传输等场景中。以下是关于高斯噪声的详细说明、添加方法及滤波方案。 …...

OSPF的接口网络类型【复习篇】

OSPF在不同网络环境下默认的不同工作方式 [a3]display ospf interface g 0/0/0 # 查看ospf接口的网络类型网络类型OSPF接口的网络类型(工作方式)计时器BMA(以太网)broadcast ,需要DR/BDR的选举hello:10s…...

maven编译jar踩坑[sqlite.db]

背景: 最近在项目中搞多数据源切换的job,在src/resource下有初始化的sqlite默认文件供后续拷贝使用,在测试阶段没有什么问题,但是一部署到服务器上运行就有问题。 报错现象: 找不到这个sqlite.db文件或者文件格式有问题&#x…...

【软考系统架构设计师】软件工程

1、 软件开发生命周期 软件定义时期:包括可行性研究和详细需求分析过程,任务是确定软件开发工程必须完成的总目标,具体分为问题定义、可行性研究、需求分析等 软件开发时期:软件的设计与实现,分为概要设计、详细设计、…...

蓝桥杯单片机刷题——ADC测量电位器的电压

设计要求 通过PCF8591的ADC通道测量电位器RB2的输出电压,并使用套件上提供的USB转串口功能,完成下列程序设计要求。 串口每次接收包含5个字符的字符串, 1)若接收的5个字符中有字符’a’或’A’,则数码管显示一位小数…...

:DataFrame 数据清洗与预处理 (下) - 类型转换、格式化、文本与日期处理)

零基础上手Python数据分析 (12):DataFrame 数据清洗与预处理 (下) - 类型转换、格式化、文本与日期处理

写在前面 上一篇博客,我们学习了如何使用 Pandas 处理数据分析中最常见的 “脏数据”:缺失值、重复值和异常值。 这为我们处理数据质量问题打下了坚实的基础。 然而,数据清洗的挑战远不止于此。 在实际数据中,我们还会经常遇到 数据类型不一致、数据格式不规范、文本数据混…...

免费下载 | 2025清华五道口:“十五五”金融规划研究白皮书

《2025清华五道口:“十五五”金融规划研究白皮书》的核心内容主要包括以下几个方面: 一、五年金融规划的重要功能与作用 凝聚共识:五年金融规划是国家金融发展的前瞻性谋划和战略性安排,通过广泛听取社会各界意见,凝…...

)

制造一只电子喵 (qwen2.5:0.5b 微调 LoRA 使用 llama-factory)

AI (神经网络模型) 可以认为是计算机的一种新的 “编程” 方式. 为了充分利用计算机, 只学习传统的编程 (编程语言/代码) 是不够的, 我们还要掌握 AI. 本文以 qwen2.5 和 llama-factory 举栗, 介绍语言模型 (LLM) 的微调 (LoRA SFT). 为了方便上手, 此处选择使用小模型 (qwen2…...

Java中parallelStream并行流使用指南

Java中parallelStream并行流使用指南 在 Java 中,parallelStream() 是 Java 8 引入的一个用于并行处理集合数据的工具,它基于 Fork/Join框架 实现,能够自动将任务拆分成子任务并利用多核处理器并行执行。以下是对 parallelStream的详细说明和…...

Python及C++中的列表

一、Python中的列表(List) Python的列表是动态数组,内置于语言中,功能强大且易用,非常适合算法竞赛。 1. 基本概念 定义:列表是一个有序、可变的序列,可以存储任意类型的元素(整数…...

mybatis plus 分页查询出来数据后对他二次 修改数据 封装返回

mybatis plus 分页查询出来数据后对他二次 修改数据 封装返回 /*** 搜索问卷** param keyword* param pageNo* param pageSize* return*/AutoLog(value "v_survey-搜索")ApiOperation(value"v_survey-搜索", notes"v_survey-搜索")GetMapping(v…...

海洋大地测量基准与水下导航系列之八我国海洋水下定位装备发展现状

中国国家综合PNT体系建设重点可概括为“51N”,“5”指5大基础设施,包括重点推进下一代北斗卫星导航系统、积极发展低轨导航增强系统、按需发展水下导航系统、大力发展惯性导航系统、积极探索脉冲星导航系统;“1”是实现1个融合发展࿰…...

基于单片机的电梯智能识别电动车阻车系统设计与实现

标题:基于单片机的电梯智能识别电动车阻车系统设计与实现 内容:1.摘要 随着电动车在日常生活中的普及,将电动车带入电梯带来的安全隐患日益凸显,如引发火灾等。本研究的目的是设计并实现一种基于单片机的电梯智能识别电动车阻车系统。方法上,…...

什么是柜台债

柜台债(柜台债券业务)是指通过银行等金融机构的营业网点或电子渠道,为投资者提供债券买卖、托管、结算等服务的业务模式。它允许个人、企业及机构投资者直接参与银行间债券市场的交易,打破了以往仅限机构参与的壁垒。以下是综合多…...

.py文件和.ipynb文件的区别:完整教程

一、概述 Python开发者常用的两种文件格式.py和.ipynb各有特点,本教程将通过对比分析、代码示例和场景说明,帮助开发者全面理解二者的区别与联系。 二、核心区别对比 1. 文件格式本质 特性.ipynb文件.py文件文件类型JSON结构化文档纯文本文件存储内容…...

Python中NumPy的逻辑和比较

在数据科学和科学计算领域,NumPy是一个不可或缺的Python库。它提供了高效的多维数组对象以及丰富的数组操作函数,其中逻辑和比较操作是NumPy的核心功能之一。通过灵活运用这些操作,我们可以轻松实现数据筛选、条件判断和复杂的数据处理任务。…...

tt_Docker

快速上手 查看 Docker 服务运行状态;查看本地镜像;从 Docker Hub 拉取基础镜像, 我们此处选择 ubuntu:18.04 镜像;再次查看本地镜像;使用 ubuntu:18.04 镜像构建容器,并交互式运行容器;在容器内部执行 LS 命令;退出容器;查看本地容器实例;再次启动停止的…...

虚幻引擎5-Unreal Engine笔记之“将MyStudent变量设置为一个BP_Student的实例”这句话如何理解?

虚幻引擎5-Unreal Engine笔记之“将MyStudent变量设置为一个BP_Student的实例”这句话如何理解? code review! 文章目录 虚幻引擎5-Unreal Engine笔记之“将MyStudent变量设置为一个BP_Student的实例”这句话如何理解?理解这句话的关键点1.类(…...

compose map 源码解析

目录 TileCanvas ZoomPanRotateState ZoomPanRotate 布局,手势处理完了,就开始要计算tile了 MapState TileCanvasState telephoto的源码已经分析过了.它的封装好,扩展好,适用于各种view. 最近又看到一个用compose写的map,用不同的方式,有点意思.分析一下它的实现流程与原…...

IDEA202403 常用设置【持续更新】

文章目录 1、设置maven2、设置JDK3、菜单栏固定展示4、连接Gitee第一步、安装插件第二步、Gitee账号配置 IDEA 是程序员的编程利器,需要具备其的各种配置,提高工作效率。Java项目启动,两个关键设置:Maven 和 JDK设置。 1、设置mav…...

从零开始开发纯血鸿蒙应用之语音输入

从零开始开发纯血鸿蒙应用 〇、前言一、认识 speechRecognizer1、使用方式2、依赖权限3、结果回写 二、实现语音识别功能1、创建语音识别引擎2、设置事件监听3、启动识别4、写入音频数据5、操作控制 三、总结 〇、前言 除了从图片中识别文本外,语音输入也是一种现代…...

c++ STL常用工具的整理和思考

蓝桥杯后,我整理了这些常用的C STL工具 作为一个算法竞赛的中等生,以前总觉得STL“花里胡哨”,不如自己写数组和循环踏实。但这次蓝桥杯发现,合理用STL能省很多时间,甚至避免低级错误。下面是我总结的常用知识点和踩过…...

Go:复合数据结构

数组 定义:数组是固定长度、元素数据类型相同的序列 。元素通过索引访问,索引从 0 到数组长度减 1 。可用len函数获取元素个数 。 初始化:默认元素初始值为类型零值(数字为 0 ) 。可使用数组字面量初始化,…...

)

SQL 语句基础(增删改查)

文章目录 一、SQL 基础概念1. SQL 简介2. 数据库系统的层次结构 二、SQL 语句分类1. DDL(Data Definition Language 数据定义语言)1.1 CREATE1.1.1 创建数据库1.1.2 创建数据表1.1.3 创建用户 1.2 ALTER1.2.1 AlTER 添加字段名1.2.2 ALTER 修改字段名1.2…...

【蓝桥杯 CA 好串的数目】题解

题目链接 考虑令 p r e [ i ] pre[i] pre[i] 表示 [ p r e [ i ] , i ] [pre[i], i] [pre[i],i] 是连续非递减子串,这可以类似双指针 O ( n ) O(n) O(n) 预处理: std::vector<int> pre(n); for (int r 1, l 0; r < n; r) {if (s[r] ! s[…...

——Linux命令)

Oracle for Linux安装和配置(11)——Linux命令

11.1. Linux命令 Linux是目前比较常用和流行的操作系统,现在很多生产环境就会用到它。随着其功能、性能、稳定性和可靠性等方面的日渐增强和完善,加之其成本上的优势,其市场占有率逐日攀升,也得到越来越多广大用户的关注和青睐。但作为一种操作系统,其安装、配置、管理和…...

Linux基础7

一、逻辑卷管理 查看所有物理卷:pvs 查看当前系统卷组:vgs 查看所有逻辑卷:lvs 新创建系统卷组:vgcreate [参数] [volume name] url/sdb[1-2] eg:vgcreate vg_Test /dev/sdb{1,2} >…...

C#打开文件及目录脚本

如果每天开始工作前都要做一些准备工作,比如打开文件或文件夹,我们可以使用代码一键完成。 using System.Diagnostics; using System.IO;namespace OpenFile {internal class Program{static void Main(string[] args){Console.WriteLine("Hello, …...

Docker 镜像 的常用命令介绍

拉取镜像 $ docker pull imageName[:tag][:tag] tag 不写时,拉取的 是 latest 的镜像查看镜像 查看所有本地镜像 docker images or docker images -a查看完整的镜像的数字签名 docker images --digests查看完整的镜像ID docker images --no-trunc只查看所有的…...

Python数组学习之旅:数据结构的奇妙冒险

Python数组学习之旅:数据结构的奇妙冒险 第一天:初识数组的惊喜 阳光透过窗帘缝隙洒进李明的房间,照亮了他桌上摊开的笔记本和笔记本电脑。作为一名刚刚转行的金融分析师,李明已经坚持学习Python编程一个月了。他的眼睛因为昨晚熬夜编程而微微发红,但脸上却挂着期待的微…...

Vue 3 和 Vue 2 的区别及优点

Vue.js 是一个流行的 JavaScript 框架,广泛用于构建用户界面和单页应用。自 Vue 3 发布以来,很多开发者开始探索 Vue 3 相较于 Vue 2 的新特性和优势。Vue 3 引入了许多改进,优化了性能、增强了功能、提升了开发体验。本文将详细介绍 Vue 2 和…...

特殊定制版,太给力了!

今天给大家分享一款超棒的免费录屏软件,真的是录屏的好帮手! 这款软件功能可以录制 MP4、AVI、WMV 格式的标清、高清、原画视频,满足你各种需求。 云豹录屏大师 多功能录屏神器 它的界面特别简洁,上手超快,用起来很顺…...

Vue事件修饰符课堂练习

Vue事件修饰符课堂练习 题目:基于 Vue 2.0,使用事件修饰符 .stop、.prevent、.capture、.self 和 .once,为按钮绑定 click 事件,并展示每个修饰符的作用。 要求: 创建一个 Vue 实例,并绑定到一个 HT…...

Y1——ST表

知识点 ST表 只能询问,不能修改 ST表的预处理: 使用了DP的思想,设a是要求区间最值的数列,f(i,j)表示从第i个数起连续2^j个数中的最大值 状态转移方程 f [ i , j ]max( f [ i , j-1 ], f [ i 2 ^ j-1,j - 1]) 建立ST表 vo…...

Python Cookbook-5.14 给字典类型增加排名功能

任务 你需要用字典存储一些键和“分数”的映射关系。你经常需要以自然顺序(即以分数的升序)访问键和分数值,并能够根据那个顺序检查一个键的排名。对这个问题,用dict 似乎不太合适。 解决方案 我们可以使用 dict 的子类,根据需要增加或者重…...

第二十二: go与k8s、docker相关编写dockerfile

实战演示k8s部署go服务,实现滚动更新、重新创建、蓝绿部署、金丝雀发布-CSDN博客 go 编写k8s命令: 怎么在go语言中编写k8s命令 • Worktile社区 k8s中如何使用go 在K8s编程中如何使用Go-阿里云开发者社区 go build - o : -o:指定输出文件…...

Servlet、HTTP与Spring Boot Web全面解析与整合指南

目录 第一部分:HTTP协议与Servlet基础 1. HTTP协议核心知识 2. Servlet核心机制 第二部分:Spring Boot Web深度整合 1. Spring Boot Web架构 2. 创建Spring Boot Web应用 3. 控制器开发实践 4. 请求与响应处理 第三部分:高级特性与最…...

事件过滤器

1.简介 事件过滤器是指在程序分发到event事件之前进行的一次高级拦截。 2.使用步骤 给控件安装事件过滤器重写eventfilter事件 3.具体实现 3.1安装事件过滤器 代码: //给label1安装事件过滤器ui->label->installEventFilter(this); 3.2重写eventfilter…...

AI识别与雾炮联动:工地尘雾治理新途径

利用视觉分析的AI识别用于设备联动雾炮方案 背景 在建筑工地场景中,人工操作、机械作业以及环境因素常常导致局部出现大量尘雾。传统监管方式存在诸多弊端,如效率低、资源分散、监控功能单一、人力效率低等,难以完美适配现代工程需求。例如…...

)

Kubernetes nodeName Manual Scheduling practice (K8S节点名称绑定以及手工调度)

Manual Scheduling 在 Kubernetes 中,手动调度框架允许您将 Pod 分配到特定节点,而无需依赖默认调度器。这对于测试、调试或处理特定工作负载非常有用。您可以通过在 Pod 的规范中设置 nodeName 字段来实现手动调度。以下是一个示例: apiVe…...

Nacos注册中心

Nacos注册中心 本地环境搭建 准备挂载的文件夹 在拉取 Nacos 镜像之前,在 E:\docker 文件夹下,创建一个 /nacos 文件夹,等会运行容器时,用于将 Nacos 容器中的配置文件、持久化文件挂载出来,防止容器重启时数据丢失…...

,还有CAUSAL_LM,QUESTION_ANS)

除了 `task_type=“SEQ_CLS“`(序列分类),还有CAUSAL_LM,QUESTION_ANS

task_type="SEQ_CLS"是什么意思:QUESTION_ANS 我是qwen,不同模型是不一样的 SEQ_CLS, SEQ_2_SEQ_LM, CAUSAL_LM, TOKEN_CLS, QUESTION_ANS, FEATURE_EXTRACTION. task_type="SEQ_CLS" 通常用于自然语言处理(NLP)任务中,SEQ_CLS 是 Sequence Classif…...

二战蓝桥杯所感

🌴 前言 今天是2025年4月12日,第十六届蓝桥杯结束,作为二战的老手,心中还是颇有不甘的。一方面,今年的题目比去年简单很多,另一方面我感觉并没有把能拿的分都拿到手,这是我觉得最遗憾的地方。不…...

深度解析自动化工作流工具:n8n 与 Dify 的对比分析

深度解析自动化工作流工具:n8n 与 Dify 的对比分析 随着企业数字化转型的加速,自动化工具在提高工作效率、降低人工成本方面扮演着越来越重要的角色。市面上有多种自动化工作流工具可供选择,其中 n8n 和 Dify 是两个备受关注的开源和商业产品…...

深度剖析Python中的生成器:高效迭代的秘密武器

深度剖析Python中的生成器:高效迭代的秘密武器 在Python的编程世界里,生成器(Generator)是一个强大而又迷人的特性,它为开发者提供了一种高效处理大量数据的方式,尤其在涉及到迭代操作时,能显著…...