高速电路设计概述

1.1 低速设计和高速设计的例子

本节通过一个简单的例子,探讨高速电路设计相对于低速电路设计需要考虑哪些不同的问题。希望读者通过本例,对高速电路设计建立一个表象的认识。至于高速电路设计中各方面的设计要点,将在后续章节展开详细的讨论。

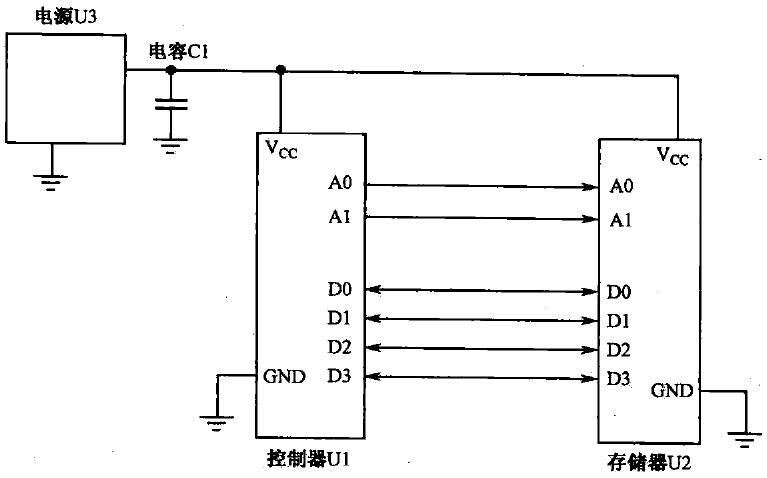

【案例1-1】简化的存储电路模块

下图是一个经简化后典型的存储模块原理图。对于同样的简化原理图,根据以下两种不同的客户需求,需要设计不同的存储系统,一种是低速系统,一种是高速系统。

1.1.1 低速设计

第一个客户需求是,设计一套机床台面振动监测系统,要求每20ms(ms:毫秒)检测一次振动信息,然后把数据存储到存储器内,每分钟把存储器内存储的3000个数据读取出来,并做一定的运算处理(该算法的实现方式是,读取一个数据即处理一次,数据处理完成即丢弃),得到一个体现一分钟内振动量的值,并在显示器上显示,数据读取和处理的过程不超过1s(s:秒),在此期间,可以暂停数据采样。

首先进行需求分析。这是一套采样率为0.02秒/次的采样系统,每0.02s对振动信息采样一次并存储到存储器里,则每60s需要对3000个数据进行运算处理并通过串口,将运算结果传送出去。振动传感器的选型及其放大电路的设计不在本例中讨论,本例主要研究该监测系统的存储部分。另外,假定传感器输出电信号的采样值用8位二进制,即一个字节表示。

从成本以及功能考虑,可以选择由单片机及小容量存储器组建在本存储系统。

U1选择某款51系列的单片机,主频为12MHz(MHz:兆赫兹),外部总线的最高运行速率可达1MHz。U2选择为能和该单片机直接接口的小容量RAM(随机存储器)。在本例中,采样速率的要求是50Hz(每0.02s采样一次),则存储器写入的速度可设定为0.0025秒/位(0.02/8位)。假定单片机对数据的处理时间相对于读取时间可以忽略,则存储器读取速度可设定为42微秒/位(1秒/3000/8位)。

主要芯片选型完成后,进行详细设计。

该电路耗电不多,因此电源U3选用LDO(低压差线性稳压器),电容C1是电源的去耦电容,根据U3器件资料的要求,选取为10uF(uF:微法)。本设计所要求的数据传输速率较慢,是一个典型的低速电路,可以采用集总式系统的思维来分析。在设计中需要考虑以下要点:

(1)CPU和存储器选型。选择51系列的单片机和小容量的RAM。这在需求分析阶段已经完成。

(2)总功耗。即U1、U2全速运行时,整个电路板的最大功耗,要求电源U3必须能提供该最大功率,且还有20%的裕量。例如,U1的最大功耗是140mW(mW:毫瓦),U2的最大功耗是60mW,则要求U3至少能提供240mW的功率。如果U1、U2的工作电源电压Vcc都是5V,则要求U3至少能提供电流50mA(mA:毫安)。

(3)电源U3选型。根据第4章的内容,可以选择低成本且应用简单的LDO类型的电源器件,如7805。

(4)电容C1选型。根据第4章的内容,选择10uF钽电容。

1.1.2 高速设计

第二个客户的需求是,设计一套应用在以太网交换机的主控板,该交换机需要支持12个GE(GE:千兆以太网),且支持全交换。本例仍仅讨论存储部分的设计。

简化后的原理图仍然采用图1.1,不过在本例中,我们将采用不同的芯片来组建高速电路。这是一个典型的高速电路,需要采用分布式系统的思维来分析。

(1)CPU选型。在三层交换机中,主控板CPU需要支持全系统的控制链路,还需要支持以太网的很多特性。经过仔细的性能分析后,U1选用内部工作频率达1.5GHz(GHz:吉赫兹,1GHz=10^9MHz)的Freescale公司的PowerPC MPC8547。

(2)存储器选型。根据性能需要,U2选用Micron公司的数据速率达667Mbps(Mbps:兆比特每秒)的DDR2 SDRAM DIMM条,总容量为1GB(GB:吉字节)。本书第4章将详细讨论DDR2 SDRAM存储器的选型与应用。

(3)电源选型。为简化描述,此处仅考虑MPC8547和DDR2 SDRAM DIMM条之间共同的电源1.8V,并假设图1.1中Vcc为1.8V。U3需选择能输出1.8V的DC/DC电源芯片,具体选型考虑的因素将在本书第4章中介绍。DC/DC电源芯片的工作需要配合电感、MOSFET(金属氧化物场效应管)、电容等器件。对电感、电容等器件的选型,可参考书第2章的内容,对MOSFET器件的选型,可参考书第4章的内容。

(4)电容C1选型。C1可选择为220uF的钽电容,具体选型的依据将在本书第4章中介绍;根据U1和U2的工作电压,C1的额定电压可以选择为6.3V;根据PCB(PCB:印制电路板)的空间要求,电容的尺寸可选择为2412(将在本书第2章中介绍)为保证U1和U2的稳定工作,要求电容精度达到10%;由于运行速度高,该电容还需要有较小的ESR(等效电阻)以实现快速响应。对电容的选型,将在第2章中详细介绍。

(5)除C1以外,还需要给Vcc提供其他电容,以滤除电源电路上的干扰。在本书第4章和第8章中将介绍,当器件高速运行时,在电源Vcc上将产生较大的高频噪声,为了保证高速器件获得干净的电源,需要在U1和U2的每个Vcc电源引脚处,就近放置一个容值为0.1μF或者1μF的陶瓷电容,根据PCB上可使用的面积,建议选择小尺寸封装的电容,如0402尺寸;在功耗较大的设计中,还应考虑放置稳定性,需要选用X7R的电容类型,根据器件工作电压,电容的额定电压可选择为10V。这一部分的选型,涉及本书第2、4章的相关内容。

(6)逻辑器件选型。在U1和U2之间,如果由于速率或者工作电压不同而无法直接接口,则还需要用到逻辑器件以实现桥接,可参考书第3章的相关内容进行逻辑器件的选型和应用。

(7)时序分析。高速电路中,信号在PCB上的走线长度对器件的时序要求至关重要,本书第5章将详细介绍时序分析和设计的方法。

(8)复位和时钟电路设计。MPC8547有多种复位要求,如上电复位、硬件复位、软件复位等,同时还要求提供多种时钟(如内核工作时钟,接口时钟等),关于复位和时钟电路的详细设计要求,可参考书第6章的内容。

(9)原理图和PCB的设计。经过前面的步骤,在完成对各种器件的选型后,对原理图的绘制,可参考书第1章的内容,而对PCB的设计,可参考书第5章的内容。

(10)防护和EMC(电磁兼容性)设计。对高速接口,还需要参考本书第8章的内容,以进行防护和EMC设计。

(11)调试。设计完成后,需要验证电路的功能。该设计属于高速设计,因此,还需要对单板上的电源、高速信号等进行相关测试,相关内容将在第4、7、8章介绍。

由此可见,相对低速电路设计,高速电路设计要求设计者考虑的因素更多,本书的后续章节,将一一探讨这些内容。

1.2 如何区分高速和低速

高速设计区别于低速设计,简单来说,就是分布式系统思维和集总式系统思维的区别。

那么,多高的信号速度才算高速?在讨论这个问题之前,需要注意避免进入以下两个误区:

误区1 信号周期频率Fclock高的才属于高速设计。事实上,设计中需要考虑的最高频率往往取决于信号的有效频率(或称转折频率)Fknee。

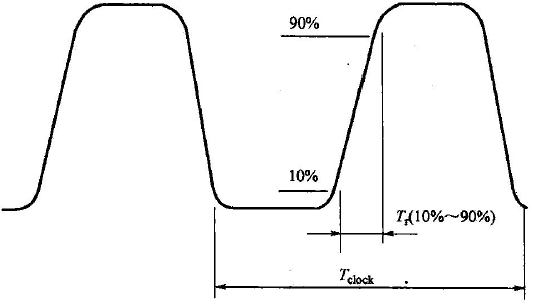

如图1.2所示,Tclock是信号的时钟周期,Tr(10%-90%)是信号的10%-90%上升时间,则信号的周期频率与有效频率分别定义为:

Fclock=1/Tclock(1.1)

Fknee=0.5/Tr(10%-90%)(1.2)

由数字信号处理的知识可知,现实世界中的任何信号都是由多个频率分量的正弦波叠加而成的。以方波为例,周期频率为F的理想方波,由频率为F的正弦波及其奇数次谐波(频率分别为3F、5F、7F等)组成,定义各正弦波分量的幅值为Vn,其计算公式为:

Vn=2/(3.14xn)(1.3)

根据式(1.3),一次谐波分量的幅值V1=0.64V,三次谐波分量的幅值V3=0.21V,五次谐波分量的幅值V5=0.13V。即随着频率的升高,各级谐波分量的幅值与频率成反比。

现实中的信号,随着频率的升高,其各级谐波分量的幅值比理想方波中相同频率正弦波分量的幅值下降得更快,直到某级谐波分量,其幅值下降到理想方波中对应分量的70%(即功率下降到50%),定义该谐波分量的频率为信号的有效频率[57]。对现实中的多数信号而言,有效频率可由式(1.2)计算。

误区2 电容、电感是理想的器件。

在低速领域,电容、电感的工作频段比较低,可以认为它们都是理想的器件。但在高速领域,电路板上的电容、电感等已经不能被简单地视为纯粹的电容、电感。例如,当电路的两端用一个电容C相连时,在低速电路中,这两端被视为断路,而在高速电路中,假定其工作频率为F,则电容C表现的电抗值为1/(2πFXC),在工作频率很高的情况下,该电容C的电抗值变得很小,表现为短路。同理,在低速电路中表现为短路的电感,在高速电路中表现为断路。本书第2章将详细介绍在何种频率点上,电容和电感将发生这种属性的变化。

在认清了以上两个误区后,我们再重新回到如何区分低速信号与高速信号的问题。

这里讲的低速信号为传输路径上各点的电平大致相同的信号,高速信号为传输路径上各点电平存在较大差异的信号。

对低速信号而言,由于传输路径上各点电平近似相同,因此,可采用集总式的思维来看待传输路径,即传输路径上各点的状态相同,在分析时,可被集中成一点;对高速信号而言,传输路径上各点的电平不同,需要用分布式的思维来看待传输路径,即不能将传输路径集中成一点来看待,而应视为多个状态不同的点。

由此可知,高速与低速的区分,不仅取决于信号频率,还取决于信号传输路径的长度,仅仅依据信号频率,并不能做出信号属于高速还是低速的结论。

一般而言,在信号传输路径的长度(即信号线的长度)小于信号有效波长的1/6时,可以在该传输路径上,各点的电平状态近似相同。

信号波长与信号频率的关系如下:

λ=c/F(1.4)

式中 λ——信号波长;

c——信号在PCB上传输的速度,该速度略低于光速,与信号走线所在的层有关,为讨论方便起见,此处将c视为常数;

F——信号的频率。

在c为常数的前提下,λ与F成反比,即信号频率F越高,其波长越短,则低速和高速分水岭的信号线长度越短,反之亦然。

因此,在信号频率已知的前提下,可以确定低速和高速分水岭的信号线长度。显然,根据前面的讨论,此处的信号频率应采用信号的有效频率Ftrans而不是信号的周期频率Fclock。

综合上述,区分高速和低速信号的步骤如下:

第一步,获得信号的有效频率Ftrans和走线长度L。

第二步,利用Ftrans计算出信号的有效波长λtrans。

第三步,判断L与1/6×λtrans之间的关系,若L>1/6×λtrans,则信号为高速信号,反之,则为低速信号。

在以上步骤中,需注意以下几点:

(1)如何获得信号的有效频率Ftrans呢?在有测试板等现成电路的情况下,可直接测量信号的10%90%上升时间,再利用式(1.2)即可计算得到Ftrans的值。而在没有现成电路的情况下,可假设信号的上升时间为信号周期的7%[67],此时,信号有效频率Ftrans约为信号周期频率Fclock的7倍,例如,周期频率为100MHz的时钟信号,可估计其有效频率约为700MHz。

(2)第一点对极高频信号(如频率在1GHz以上的信号)并不成立,极高频信号的上升沿很缓,上升时间甚至可能达到信号周期的20%,因此,再用Ftrans的估算公式已经没有意义,同时,判断极高频信号属于高速还是低速,本身也是一件没有意义的事情。

对所有的高速信号,应视做传输线处理,本书第8章将详细讨论传输线的应用及设计要点。

1.3 硬件设计流程

高速电路设计属于硬件设计,对从事高速电路设计的工程师而言,需要掌握从需求分析到大规模生产的各个环节。本小节将简单地对这些环节进行介绍,本节内容虽不针对高速电路设计,但却是高速电路设计者必须了解的。

硬件设计的流程分为以下几个步骤:需求分析、概要设计、详细设计、调试、测试、转产。

1.3.1 需求分析

需求分析是硬件设计的第一步,也是最关键的一步。在需求分析阶段,只有充分地理解了客户的需求,才能有针对性地开展器件选型、方案规划等工作。

需求的种类很多,与硬件开发相关的有以下几类。下文以某以太网产品的需求分析为例,进行简单的介绍。

(1)整体性能要求:如数据包转发能力、处理延时、最高处理带宽、CPU处理能力等。针对这些要求,可初步进行CPU、存储器、交换芯片等器件的选型。

(2)功能要求:如QoS(Quality of Service,服务质量)、各类以太网相关协议的实现等。针对功能要求,可对多个厂家提供的交换芯片等器件做进一步细分,筛选能满足所有功能要求的器件。

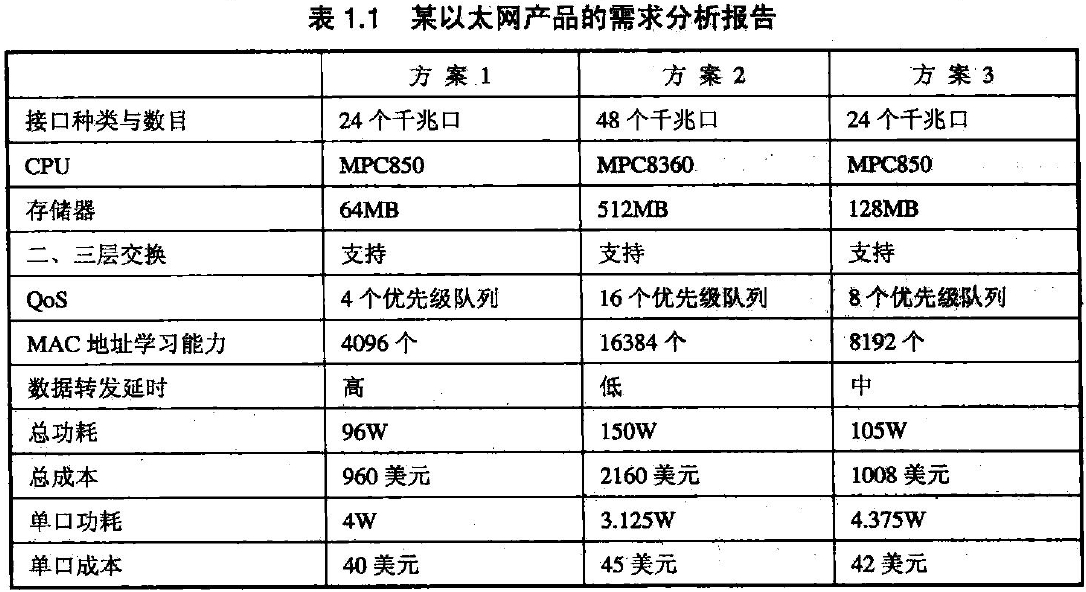

(3)成本要求:成本分析是需求分析中重要的一步,在满足客户需求的前提下,尽可能地降低成本,是硬件工程师的重要职责。在成本的分析中,应计算各套方案下单板的总成本,在某些场合,还需计算单个用户接口的成本。例如,某客户提出的需求是1000个以太网接口,针对该需求,提出了两套方案,分别是单块业务板提供24和48个接口,相对前者,后者对CPU和存储器的要求比较高,在这种情况下,计算单个接口的成本比计算整个单板的成本更有意义。

(4)用户接口要求:如接口的种类、数目、指示灯及其规范、复位键、电源按钮等。同时,该类需求还包括与用户操作相关的要求,如对单板状态的在线监控等。这类要求多着眼于细节,不太会影响关键器件的选型,但若忽略了其中的某一项,即可能导致整个产品的失败。例如,某产品的用户面板上提供有主、备两个串口,分别标识为“Master”和“Slave”,由于“Slave”在英文中有奴隶的含义,违反了某些地区对电子产品标识的规定,导致该产品在这些地区无法销售。

(5)功耗要求:功耗要求是单板上电源功率分配的依据,涉及电源架构的设计、电源电路器件的选型。

某以太网产品的需求分析报告如下表所示。

针对上表,补充说明一点,表中所计算得到的单口成本并未考虑机框、用户机房占用面积的成本,方案1和方案3的单口成本低于方案2,但方案2中,单块单板拥有更多的接口数目,因此,相对另外两种方案,更能节省机框和机房面积的成本,在这种情况下,又需要结合总成本来考虑。

需求分析阶段的工作是制定设计的大方向,不能忽略细节,但也不能拘泥于细节。需求分析阶段的工作并不是哪一个特定工程师的工作,而应由项目经理、系统工程师、电子设计工程师、软件工程师、逻辑工程师等协作完成。

1.3.2 概要设计

从概要设计阶段开始,软件、硬件工程师开始分头工作,本小节只讨论硬件方面的工作。

硬件概要设计的主要任务是设计系统框图、关键链路连接图、时钟分配框图等,并制定电源设计总体方案,对信号完整性及EMC的可行性、结构与散热的可行性、测试可行性等环节,做初步的分析。在这一阶段,需要电子设计工程师、电源工程师、信号完整性工程师、结构与热设计工程师、EMC工程师、测试工程师等协同工作。

需求分析的目标是选定一套最佳的方案,确定关键器件及总体架构,而概要设计则是对该架构做进一步的细化。在概要设计阶段,与硬件设计相关的各部门工程师开始介入并做可行性分析,若发现总体方案的某些方面不可行,应回馈给项目经理,重新进行需求分析,并更改方案。因此,可以认为,需求分析和概要设计这两个阶段是螺旋形前进并不断反复的过程。

1.3.3 详细设计

概要设计完成后,单板的总体框架已经确定,则在详细设计阶段需要完成的工作,是基于该框架,将每一个部分细化。以下简要地介绍各职能部门工程师的职责。

1• 电子设计工程师

电子设计工程师负责各个总线接口信号的定义,CPU存储空间分配,时钟、复位电路器件选型及其拓扑结构,中断链路拓扑结构,电源电路的详细框图(需注明各路电源的产生方式、电压值、电流值等),关键电源的滤波方式,逻辑器件功能及其寄存器说明书,面板上用户接口的定义及接口信号连接关系,指示灯器件的选型及其连接关系,最后绘制原理图并产生物料清单。在详细设计阶段的后期,应开始测试计划的制订。

2• PCB设计工程师

根据电子设计工程师提供的原图图及对应的网表,结合信号完整性工程师提供的走线规则和层叠结构,完成PCB的设计,并生成可供工厂生产使用的文件。

3• 信号完整性工程师

根据电子设计工程师提供的详细设计文档,同时根据板内高速信号的信号质量及时序要求,设计PCB层叠结构,基于前仿真的结果定义信号的走线规则,在PCB走线完成后,对高速信号进行仿真以初步验证信号完整性,对关键电源做电源完整性仿真,向电子设计工程师提供关于电源滤波的参考意见,最后协同电子设计工程师,共同完成测试计划的制订。

4• 逻辑设计工程师

根据电子设计工程师提供的逻辑器件说明书,编写逻辑器件的代码及测试代码,并进行相关的仿真。

5• 电源设计工程师

根据电子设计工程师提供的各关键器件的电源电压及电流值,汇总得到各类电源的总功耗需求,根据该结果,进行电源器件的选型及电源架构的设计。同时,对较复杂的电源电路,电源设计工程师还应给出推荐的电源电路和滤波方案。在调试和测试阶段,电源设计工程师负责协助电子设计工程师完成电源电路的调试与测试。在电源电路不是特别复杂的情况下,往往由电子设计工程师兼任电源设计工作。

6• 结构工程师

根据电子设计工程师提供的用户面板信息以及PCB设计工程师提供的PCB尺寸、定位、安装等信息,设计PCB的机械图,制定PCB的限布区(禁止布放器件的区域)和限高区(禁止布放超高器件的区域),在PCB上设定安装孔的位置,同时还负责面板的设计。这些设计图和数据将成为PCB设计的重要输入信息。

7• 热设计工程师

根据电子设计工程师提供的各器件总功耗,器件布放位置及器件的高度,进行热方面的仿真,结合仿真结果完成热设计,如散热片的选型、风道的规划、温度传感器的布放位置等。同时,热设计工程师应将单板的温度散布区域图提供给电子设计工程师,以作为PCB布局的参考。

8• EMC及防护设计工程师

根据电子设计工程师提供的用户接口信息、高速信号的速率和分布区域,以及PCB设计工程师提供的PCB层叠结构,定义高速信号走线规则,用户接口防护方案等。需要说明的是,信号完整性工程师和EMC设计工程师都会对高速信号的走线规则做出定义,两类走线规则可能会有冲突,此时应由电子设计工程师负责与这两位工程师协商,确定最终的规则。

9• 测试工程师

测试工程师包括边界扫描设计工程师、ICT工程师(ICT指在线测试,将在第8章介绍)、硬件测试工程师。前两类有专门的职能部门,一般不由其他工程师兼任,而硬件测试工程师往往可以由电子设计工程师兼任。

边界扫描设计工程师和ICT工程师根据电子设计工程师提供的原图图、器件资料,前者负责完成边界扫描链路的设计和程序的编写,后者负责完成ICT夹具的设计和程序的编写。需注意,由于ICT夹具的制作成本较高,在硬件设计稳定之前,一般不会完成夹具的设计,因此对一块新设计的单板而言,在前几版的生产中,一般无法使用ICT测试。

硬件测试工程师根据电子设计工程师提供的原图,进行可测试性分析,汇总需要测试的信号,并辅助PCB设计工程师,为各信号添加测试点。

10• 产品工程师

产品工程师是设计部门与生产部门沟通的纽带。根据电子设计工程师提供的物料清单,产品工程师检查各器件的厂家生产状况、生产部门备料情况,做出更换、推荐器件的建议,并将结果反馈给电子设计工程师。PCB设计完成后,产品工程师负责检查PCB设计是否符合可生产性、可加工性的规定,对违反规定的设计,提出修改建议,并反馈给PCB设计工程师。

11• 软件工程师

在这一阶段,软件工程师应开始软件的详细设计,但同时,还应与电子设计工程师协同工作,确定CPU速率、复位逻辑、中断拓扑、各器件之间的互连接口、用户监控等信息,以使软件设计与硬件设计相匹配。

由以上职责描述可知,在硬件详细设计阶段,电子设计工程师除负责电路设计外,同时在各部门间还发挥了协调的作用。电子设计工程师的输出,将作为其他各部门的输入,而其他各部门的输出,又成为电子设计工程师的输入,环环相扣。因此可以说,一个成功的硬件设计是一个有机的整体,需要多部门工程师的协调工作,任何一个环节出错都可能导致整个设计的失败。

1.3.4 调试

单板从工厂生产加工完成后,回到研发部门,由电子设计工程师、逻辑设计工程师、电源设计工程师、软件工程师协同进行调试。

对第一次回到研发部门的单板,首先需要做的是验证是否存在电源短路现象。例如,某块单板有以下几种电源:3.3V、2.5V、1.8V、1.2V,则调试阶段的第一个步骤就是验证这些电源是否与GND(单板上的信号地)发生了短路,以及各电源之间是否发生短路。对电源保护设计不完善的单板,这一步骤尤为重要。

第二个步骤是对单板上可编程器件程序的加载。

其后,对电源电路、逻辑设计、时钟和复位电路等功能模块的调试可并行进行。

当以上功能模块的调试通过后,可开始测试流程。流量测试是验证单板上各部分电路协调工作的最佳工具,在这一步,除时间正常流量的测试外,还需人为地模拟一些可能发生中断等告警功能的流量,以对相应功能模块进行验证。

1.3.5 测试

测试是对设计进行验证的重要阶段。硬件测试工程师是这一阶段的主要负责人,其关键输入为详细设计阶段后期电子设计工程师拟定的测试计划。

1• 测试计划的主要内容

(1)测试设备列表。列出测试中所需仪器的型号和数目,如电源、示波器、探头、万用表、信号发生器等。

(2)测试环境的搭建图。绘制测试仪器与被测单板的连接示意图,若测试中需要以太网口、串口等线缆的连接,示意图中还需标明线缆的规格、线缆连接的方式及对应端口的地址。

(3)电源测试。测试各电源的电压及电流(针对空载和满载两种情况)、纹波、噪声、上电顺序、下电顺序。

(4)各接口信号的信号完整性与时序。在测试计划中,应列出待测信号的网络名、时序要求等。

(5)各通用接口的功能测试。通用接口指I²C、RS-232等标准接口,在测试计划中应列出各接口的访问地址及测试代码。

(6)复位链路的测试。

(7)晶振、时钟驱动器、锁相环等与时钟相关的测试。测试时钟信号的频率、上升/下降边沿时间,对关键时钟信号,还应借助温箱,测试环境温度变化时时钟频率的稳定度。需注意,不推荐利用示波器测试时钟频率,而应采用专门的频率测试仪进行测试。

(8)指示灯、单板在位信号、槽位号等杂项的测试。

(9)流量的测试。测试计划中应列出流量测试的数据流向图,测试代码、测试时间、误码率要求等。

2• 其他测试

除以上常规测试外,在测试计划中还需包括某些强度测试的测试项。不同类型的单板有不同的强度测试项,以下仅举一些通用的例子。

(1)电源监控功能的测试。例如,通过强制将电源电压调整超出监控的阈值,判断监控电路是否报警。

(2)极限环境的测试。例如,调整板上电源输出电压到最高、最低极限值,调整温箱的温度变化率,在这些极限环境下对流量进行测试。

若单板上包括有某些特定用户接口,如以太网电口、光口,光传输的E1、T1等端口,都需要根据接口所对应的标准规范,验证接口是否满足规范的要求。

在测试阶段,硬件测试工程师的职责是按照测试计划书一项一项地测试,并将结果反馈给电子设计工程师,针对测试所发现的问题,提供相应的更改意见。

1.3.6 转产

在调试和测试完成后,硬件设计的最后一个阶段是将与生产相关的资料转给工厂,以便工厂开始大规模批量生产。

在这一阶段,ICT工程师的测试夹具和代码也应完成并提供给工厂。此时,电子设计工程师的职责是将单板知识和测试技能传授给工厂的测试人员。

理解要点:

① 硬件设计流程包括以下几个阶段:需求分析、概要设计、详细设计、调试、测试、转产。

② 一个设计的成功,需要来自多个部门的工程师通力合作。

1.4 原理图设计

本书后续部分将详细介绍硬件设计流程的各个阶段。在此之前,本节将简单地介绍原理图设计时的注意事项。

原理图是电路设计的中间文件,虽然其并不直接用于指导生产,但却是连接设计理念和最终产品的关键纽带。

电子设计工程师是原理图的责任人,多数设计者认为原理图不过是生成网表的源文件,至于其设计风格则完全可以依个人喜好而定。

事实上,原理图在整个设计过程中,起着非常关键的作用。

首先,原理图是设计思想的体现,混乱的原理图只能代表混乱的设计思想。

第二,原理图是电子设计工程师与PCB设计工程师沟通的重要工具,当单板复杂到一定程度时,电子设计工程师不可能通过语言将所有PCB设计时需注意的细节都告知PCB设计工程师,例如,PCB设计工程师从原理图获得网络连接关系(简称网表),虽然知道各器件的连接关系,但却无法获得器件摆放位置等信息,在这种情况下,原理图的设计将成为重要的工具,一方面使PCB设计工程师对设计的要求一目了然,另一方面也能对电子设计工程师起到提醒作用,避免在设计、测试时遗忘某些关键细节。

第三,脉络清晰的原理图有助于提高调试、测试、生产等环节的效率。

由以上看来,原理图并不只是一份中间文件,为了得到一份优质的原理图,在设计的过程中,有许多事项需要注意。

(1)在原理图的首页,应绘制单板的总体框架图。若单板较复杂,还应根据需要,在后续页上绘制电源架构框图、时钟拓扑图、复位链路拓扑图、中断链路拓扑图、边界扫描链路图等。若单板的面板接口较多,建议增加一页用于面板图示。若PC总线的拓扑较复杂,还需增加一页用于注释各PC器件的地址。

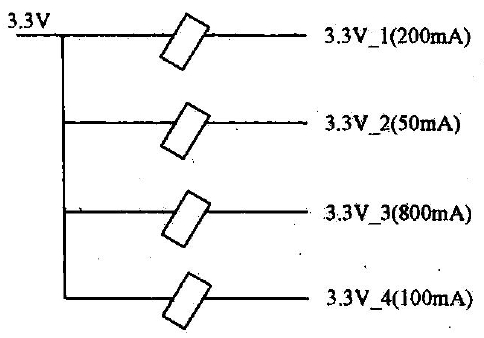

(2)在原理图上电源电路的输出端附近,应标注该路电源的电压值和电流值。例如,下图中,由磁珠从3.3V分出四路3.3V的支路,各支路电流不同,在原理图上标注电流后,有助于PCB工程师把握在哪些支路应做加粗走线、增加电源过孔等处理。需说明的是,图1.3中括号包含的部分(如200mA)只是注释,不属于网络名称的一部分。

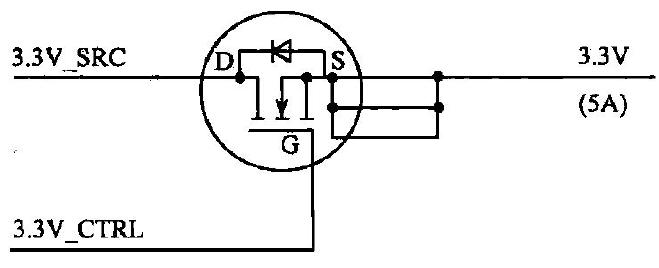

(3)标注关键电流通路。例如,在下图中,MOSFET的源极和漏极两端的路径属于关键电流通路,在原理图上标注电流值,有利于PCB设计者对该路径引起足够重视,做加粗走线等处理。

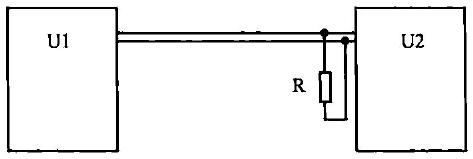

(4)绘制原理图时要兼顾在PCB设计中对器件布放位置的要求。在第8章将介绍阻抗匹配,阻抗匹配电路对器件的布放位置有一定的要求,例如,始端匹配电阻应靠近发送端器件放置,终端匹配电路应靠近接收端器件放置,在原理图的绘制中应体现这一原则。例如,U1和U2分别为发送、接收器件,R为终端匹配电阻,在PCB上应靠近U2放置,则推荐按下图方式绘制原理图。有时,U1和U2位于原理图上不同的页,则推荐将R放置在U2的那一页上。

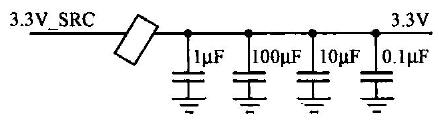

(5)按照PCB上电容的排列顺序绘制原理图的电容滤波电路。某3.3V滤波电路要求,在PCB上,1μF电容应放置在最外边,随后是100μF、10μF、0.1μF,则对应的原理图部分应绘制如下图所示。

(6)原理图上应标注关键信号的速率、走线层,若信号线之间有走线长度关系,也建议标注在原理图上。

(7)原理图上应标明高散热及热敏感器件,若有特殊要求的放置要求,也可在原理图上加以注释。

(8)对关键器件,在原理图上应标明其对应的料号、精度、尺寸等信息。这些关键器件包括保险管、分压电路中的电阻、电源滤波电路中的电感、磁珠、电容,电源电路中的电压及开关频率调节电阻、MOSFET、二极管、电压采样电阻等。

(9)在原理图上,应对跳线、选择器件的配置方法等进行注释。

(10)在原理图上,应标注与背板连接的连接器、面板上LED指示灯的排列顺序。

相关文章:

高速电路设计概述

1.1 低速设计和高速设计的例子 本节通过一个简单的例子,探讨高速电路设计相对于低速电路设计需要考虑哪些不同的问题。希望读者通过本例,对高速电路设计建立一个表象的认识。至于高速电路设计中各方面的设计要点,将在后续章节展开详细的讨论…...

Keil C51中32位变量赋值异常问题分析与解决

Keil C51中32位变量赋值异常问题分析与解决 问题描述 在使用Keil5对51单片机进行编程时,遇到一个32位变量赋值不正确的问题。具体代码如下: typedef unsigned long uint32;g_Flow_Time (uint32)Storage[2] << 24 | Storage[3] << 16 | S…...

)

python工程中的包管理(requirements.txt)

pip install -r requirements.txtpython工程通过requirements.txt来管理依赖库版本,上述命令,可以一把安装依赖库,类似java中maven的pom.xml文件。 参考 [](...

用Python修改字体字形与提取矢量数据:fontTools实战指南

字体设计与分析是NLP和视觉领域的交叉应用,而**fontTools** 是一款强大的Python库,可以让我们直接操作字体文件的底层结构。本文将通过两个实用函数,展示如何修改特定字形和提取所有字形的矢量数据,帮助开发者快速上手字体编辑与分…...

数据库守护神-WAL机制

什么是WAL机制? WAL(Write-Ahead Logging,预写日志)是一种保证数据库操作原子性和持久性的核心机制。其核心原则可概括为: 任何数据修改操作,必须在对应的日志记录持久化到磁盘之后,才能将实际…...

[MySQL]数据库与表创建

欢迎来到啾啾的博客🐱。 这是一个致力于构建完善 Java 程序员知识体系的博客📚。 它记录学习点滴,分享工作思考和实用技巧,偶尔也分享一些杂谈💬。 欢迎评论交流,感谢您的阅读😄。 本篇简单记录…...

工作记录 2015-05-27

工作记录 2015-05-27 序号 工作 相关人员 1 修改了指定短语的大小写的处理。 取消了一些逗号的处理。 郝 另: iCDA更新到了190的D:\Temp\CHTeam\iCDA_20150527下了 修改的文件: bin目录下是程序。 0223目录下是0223的一些设置和关键字。 更新…...

嵌入式汇编语言从小白到入门:从零开始的底层编程之旅

嵌入式汇编语言从小白到入门:从零开始的底层编程之旅 汇编语言作为最接近机器语言的编程方式,在嵌入式开发中扮演着不可替代的角色。本文将带你从零开始,逐步掌握嵌入式汇编语言的核心概念和实践技巧,最终能够独立编写简单的汇编程序并与C语言混合编程。 一、汇编语言与嵌…...

GPIO_ReadInputData和GPIO_ReadInputDataBit区别

目录 1、GPIO_ReadInputData: 2、GPIO_ReadInputDataBit: 总结 GPIO_ReadInputData 和 GPIO_ReadInputDataBit 是两个函数,通常用于读取微控制器GPIO(通用输入输出)引脚的输入状态,特别是在STM32系列微控制器中。它们之间的主要…...

不使用docker在本地安装与配置RAGFlow

RAGFlow 本地安装与配置(非docker方式) 一. 运行环境 windows10 CPU i7-12700F 2.10GHz内存 32GGPU RTX 4060 Ti 8G wsl 2 Ubuntu-22.04 1. 防火墙配置 wsl默认访问windows的本机服务需要配置防火墙,否则访问会失败。 windows10的防火墙配置: 打…...

sysfs 设备模型

介绍 Sysfs 设备文件系统与proc是同一类的文件系统,基于ramfs实现的内存文件系统。 1.1 为什么会有 sysfs?procfs 的局限性: 早期,Linux 使用 procfs 来提供内核与用户空间的交互接口。但 procfs 的设计不够层次化,设…...

彩讯携Rich AICloud与一体机智算解决方案亮相中国移动云智算大会

2025年4月10日,2025中国移动云智算大会在苏州盛大开幕,本次大会以“由云向智 共绘算网新生态”为主题,与会嘉宾围绕算力展开重点探讨。 大会现场特设区域展出各参会单位的最新算力成果,作为中国移动重要合作伙伴,彩讯…...

js触发隐式类型转换的场景

JavaScript 的隐式类型转换(Implicit Type Coercion)会在某些操作或上下文中自动触发,将值从一种类型转换为另一种类型。以下是常见的触发场景: 1. 使用 (宽松相等)比较时 会尝试将两边的值转换为相同类型后…...

《AI大模型应知应会100篇》第9篇:大模型的推理能力:原理与实现

第9篇:大模型的推理能力:原理与实现 摘要 近年来,随着大语言模型(LLM)的快速发展,其推理能力逐渐成为研究和应用中的热点话题。这些模型不仅能够生成流畅的文本,还能在一定程度上进行逻辑推理、…...

PODS_ROOT、BUILT_PRODUCTS_DIR和SRCROOT有什么区别

在 iOS/macOS 开发中,${PODS_ROOT}、${BUILT_PRODUCTS_DIR} 和 ${SRCROOT} 是三个核心的 Xcode 环境变量,它们的区别主要体现在 目录层级、内容归属 和 生命周期 上。以下是结构化对比和具体示例: 1. 定义与作用域对比 变量全称指向路径管理…...

Elasticsearch 系列专题 - 第六篇:高级功能与生态系统

Elasticsearch 不仅是一个强大的搜索引擎,还提供了高级功能和丰富的生态系统支持。本篇将深入探讨这些特性,并介绍如何与其他工具协同工作。 1. 高级特性 1.1 跨集群搜索(Cross-Cluster Search) 跨集群搜索允许查询多个独立集群的数据,适用于分布式系统。 配置远程集群:…...

)

python的web框架flask(hello,world版)

问题 最近需要基于一个开源项目进行二次开发,但是,现在的我主修java,从来没有接触过python的web开发。所以,我现在需要学习一下flask的hello,world。 python版本选择 通过这个Python版本状态页面Status of Python v…...

Vue学习笔记 - 逻辑复用 - 组合式函数

昨天参加了次视频面试,慢慢可以查漏补缺,继续学习Vue相关的知识,考虑找个实际的开源项目。 逻辑复用 组合式函数 在 Vue 应用的概念中,“组合式函数”(Composables) 是一个利用 Vue 的组合式 API 来封装和复用有状态逻辑的函数。 无状态的…...

Caffeine的两种实现方式

咱们来具体对比一下你之前给的这段配置代码👇: java Configuration EnableCaching public class CacheConfig { Bean public CacheManager cacheManager() { CaffeineCacheManager manager new CaffeineCacheManager("myCache"); manager.…...

单细胞Seurat标准分析流程R语言封装

单细胞Seurat标准分析流程R语言封装 数据预处理与质控(线粒体基因比例计算、QC图表生成)标准化与高变基因筛选PCA/UMAP降维与聚类分析 差异表达分析模块自动化输出PNG可视化图表(质控小提琴图、UMAP聚类图)结果将保存在results/和figures/目录下(RDS对象、差异基因CSV表格…...

MOS管的发热原因和解决办法

发热来源 如上图,MOS管的工作状态有4种情况,分别是开通过程,导通过程,关断过程和截止过程。 导致发热的损耗主要有两种:开关损耗、导通损耗。 导通损耗 导通损耗比较好计算,根据驱动电压VGS值可以得到MOS…...

航顺HK32M070电钻解决方案:驱动未来,掌控无限可能

一、市场规模与增长:电动工具行业持续扩容,电钻需求强劲 全球电动工具市场规模近年来保持稳定增长,2023年市场规模已达288.5亿美元,预计2024年将突破304.9亿美元,年复合增长率达6.9%。中国市场表现尤为亮眼࿰…...

关于nacos注册的服务的ip异常导致网关路由失败的问题

文章目录 关于nacos注册的服务的ip异常导致网关路由失败的问题相关处理方案为方案一:手动指定服务注册的 IP 地址方法二:设置优先使用的网络段方法三:指定网络接口方法四:忽略特定的网卡 备注 关于nacos注册的服务的ip异常导致网关路由失败的…...

UI测试流程与关键注意点解析

在当今以用户体验为核心的数字时代,用户界面(UI)作为软件与用户交互的直接窗口,其质量直接影响着产品的成败。UI测试作为软件测试的重要组成部分,确保应用程序不仅功能完善,而且在视觉呈现和交互体验上也能满足用户期望。 作为软…...

从零开始构建智能聊天机器人:Rasa与ChatGPT API实战教程

引言:AI对话系统的时代机遇 在数字化转型浪潮中,聊天机器人已成为连接用户与服务的关键纽带。无论是客服系统中的724小时即时响应,还是智能家居中的语音交互,聊天机器人正在重塑人机交互方式。本文将通过详细教程,手把…...

SSM aop切面编程的学习

面向切面的AOP编程的引入: 1. 代码缺陷 - 非核心代码对核心业务功能有干扰,导致程序员在开发核心业务功能时分散了精力 - 附加功能代码重复,分散在各个业务功能方法中!冗余,且不方便统一维护! 2. 解决思路 …...

Zen 5白色装机优选,华硕X870 AYW GAMING WIFI W主板来了!

华硕X870/X870E系列主板再次迎来新成员——华硕X870 AYW GAMING WIFI W主板正式发售!专为追求高性价比游戏玩家而量身打造,延续AYW系列经典SPACE太空元素,配合大面积银白色散热装甲,打造出了极具金属质感和科技感的外观࿰…...

第Y1周:调用YOLOv5官方权重进行检测

🍨 本文为🔗365天深度学习训练营 中的学习记录博客🍖 原作者:K同学啊 文章目录 1、前言2、下载源码3、运行代码 1、前言 YOLOv5分为YOLOv5s、YOLOv5m、YOLOv5l、YOLOv5x四个版本,这里以YOLOv5s为例。 2、下载源码 安…...

科技项目验收测试怎么做?验收测试报告如何获取?

科技项目从研发到上市需要一个很长的周期,并且在上市之前还有一个至关重要的交付过程,那就是项目验收,验收需要通过验收测试来呈现。科技项目验收测试是确保项目成功交付的关键步骤,那么是如何进行的呢?企事业单位想要获取科技项…...

C++笔记

C知识笔记 一、C概述 C是一种通用编程语言,它在C语言的基础上扩展而来,支持面向对象编程、泛型编程和过程化编程等多种编程范式。C具有高效、灵活、接近硬件等特点,广泛应用于系统软件、应用软件、嵌入式系统、游戏开发等领域。其强大的性能…...

国产Linux统信安装mysql8教程步骤

系统环境 uname -a Linux FlencherHU-PC 6.12.9-amd64-desktop-rolling #23.01.01.18 SMP PREEMPT_DYNAMIC Fri Jan 10 18:29:31 CST 2025 x86_64 GNU/Linux下载离线安装包 浏览器下载https://downloads.mysql.com/archives/get/p/23/file/mysql-test-8.0.33-linux-glibc2.28…...

)

如何应对“最后时刻任务堆积”(鼓包现象)

应对“最后时刻任务堆积”(鼓包现象)的方法包括:合理规划项目时间表、强化进度跟踪管理、明确任务优先级、有效的资源配置、提升团队沟通效率。其中,强化进度跟踪管理尤为关键。根据项目管理协会(PMI)的调查…...

C语言,原码、补码、反码

计算机是以补码来存储的 原码:正数最高位为:0;负数最高位为:1 (最高位是符号位) 正数:三码合一 如:2: 原码:0000 0000 0000 0000 0000 0000 0000 0010&#…...

Unifying Short and Long-Term Tracking with Graph Hierarchies—CVPR2023

Unifying Short and Long-Term Tracking with Graph Hierarchies 博客目录 Unifying Short and Long-Term Tracking with Graph Hierarchies摘要概况引言和相关介绍提出的观点 SUSHI核心构建跟踪图的层次结构构建分层剪辑分区 做第二个创新模块的需要将研究的重点从处理遮挡的问…...

深入解析 C# 中的模板方法设计模式

模板方法设计模式(Template Method Pattern)是行为型设计模式中的一种,它定义了一个操作中的算法框架,并允许子类在不改变算法整体结构的情况下,重新定义该算法的某些步骤。该模式通常用于类中包含一系列固定步骤的算法…...

0411 | 软考高项笔记:项目立项

在软考的项目管理知识体系中,技术可行性和经济可行性是项目立项阶段非常重要的两个分析维度。以下是对这两个考点的详细解释和记忆方法: 技术可行性分析 定义: 技术可行性分析是评估项目在现有技术条件和资源下是否能够成功实施。它主要回答…...

ubnetu 服务器版本常用端口和开放的端口对应的应用

1. 使用 netstat 查看端口与进程 netstat 是查看网络连接和监听端口的常用工具。通过以下命令可以列出所有开放的TCP/UDP端口及其关联的进程: sudo netstat -tulnp参数解析: -t:显示TCP端口。 -u:显示UDP端口。 -l࿱…...

【服务器端表单字符验证】

文章目录 一、实验目的二、核心代码实现三、调试关键问题四、总结 一、实验目的 掌握JSP表单验证在服务器端的实现技术,实现对用户输入字符的非空及长度为5的验证,返回对应提示信息并优化用户交互。 二、核心代码实现 前端表单 <form action"…...

pip 与 conda 的全面比较:Python 包管理的深度解析

在 Python 的生态系统中,包管理工具是开发者日常工作的重要组成部分。其中,pip 和 conda 是最常用的两种包管理工具。虽然它们在功能上有一些重叠,但在设计理念、功能范围、依赖管理、环境隔离等方面存在显著差异。本文将从多个维度深入…...

GTID不一致修复

背景描述 GTID模式下,mysql主从切换后,主从同步报错 Last_IO_Error: Got fatal error 1236 from master when reading data from binary log: The slave is connecting using CHANGE MASTER TO MASTER_AUTO_POSITION 1, but the master has purged bi…...

conda-pack打包环境到超算上。解决无法打包可编辑包

conda-pack 打包 使用 conda-pack 打包 Conda 环境可以将整个环境打包成一个独立的可移植压缩包,方便在其他机器上解压使用。以下是具体步骤: 1.安装 conda-pack 首先需要安装 conda-pack。你可以通过 conda 或 pip 安装: conda install …...

复杂度实现寻找数组第k小的数(快速选择算法))

O(n)复杂度实现寻找数组第k小的数(快速选择算法)

非堆排序实现,利用快速排序思想实现的快速选择 package algorithm;public class Test {public int quickSelect(int nums[], int left, int right, int k){if (left right) return nums[left];int i left - 1, j right 1, x nums[left];while (i < j){do i…...

利用 RNN 预测股票价格:从数据处理到可视化实战

在金融领域,预测股票价格走势一直是众多投资者和研究者关注的焦点。今天,我们将利用深度学习中的循环神经网络(RNN)来构建一个简单的股票价格预测模型,并详细介绍从数据加载、预处理、模型搭建、训练到最终结果可视化的…...

前端从全链路角度分析性能

在面试中回答“从全链路角度分析性能优化”时,需覆盖用户请求到页面渲染的完整链路。以下是结构化回答框架,结合业界实践和最新优化策略: 一、网络传输优化 1. CDN与协议升级 ◦ 使用CDN缩短资源物理距离,结合HTTP/2/3的多路复用和头部压缩特性,提升资源加载效率(如We…...

2025年第十八届“认证杯”数学中国数学建模网络挑战赛【BC题】完整版+代码+结果

# 问题一:随机森林回归from sklearn.ensemble import RandomForestRegressormodel_rf RandomForestRegressor()model_rf.fit(X_train, y_train)# 问题二:LSTM时间序列预测from tensorflow.keras.models import Sequentialmodel_lstm Sequential()model…...

权限管控与数据安全:衡石ChatBot在钉钉中的合规部署指南

数据安全是ChatBot落地的第一道门槛 在数字化转型浪潮下,企业数据查询正从“专业BI工具”向“自然语言交互”跃迁。衡石ChatBot通过钉钉等企业IM工具,让业务人员以对话方式实时获取数据,极大提升了决策效率。然而,数据开放的同时…...

什么是生产管理看板?

简单来说,生产管理看板就是一种把生产过程“摆在明面上”的工具——它可能是贴在墙上的白板,也可能是车间里一块大屏幕,主要作用就是让生产信息一目了然。 这种看板广泛用在工厂、制造车间、或者办公室里,它把生产计划、任务进度、库存情况、设备状态等重要数据通通“晒”…...

YOLO学习笔记 | 一文详解YOLOv11核心创新与实践方法

===================================================== github:https://github.com/MichaelBeechan CSDN:https://blog.csdn.net/u011344545 ===================================================== YOLOv11核心创新与实践 一、架构创新1. 模块升级与参数优化2. 多…...

198. 打家劫舍:动态规划

前言 本篇文章来自leedcode,是博主的学习算法的笔记心得。 如果觉得对你有帮助,可以点点关注,点点赞,谢谢你! 题目来源 198. 打家劫舍 - 力扣(LeetCode) 题目描述 思路 1.对于只有一个房间…...

算法基础模板

高精度加法 #include <bits/stdc.h> using namespace std; const int N10005; int A[N],B[N],C[N],al,bl,cl; void add(int A[],int B[],int C[]) {for(int icl-1;~i;i--){C[cl]A[i]B[i];C[cl1]C[cl]/10;C[cl]%10;}if(C[cl])cl; } int main() {string a,b;cin>>a&…...