特权FPGA之PS/2键盘解码

0 故事背景

见过这种接口的朋友们,大概都已经成家立业了吧。不过今天我们不讨论这种接口的历史,只讲讲这种接口的设计。(如果还没有成家的朋友也别生气,做自己想做的事情就对了!)

1 时序分析

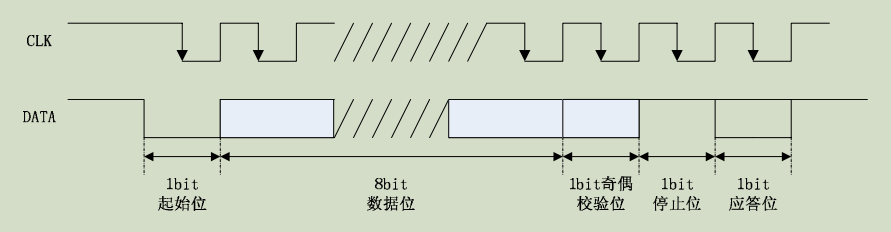

数据帧格式如图所示,起始位为低电平,停止位为高电平,应答位仅用在主机对设备的通讯中使用。如果数据位中1的个数为偶数,校验位就为1;如果数据位中1的个数为奇数,校验位就为0;总之,数据位中1的个数加上校验位中1的个数总为奇数,因此总进行奇校验。(是不是发现它的数据传输和串口很像呢!)[1]

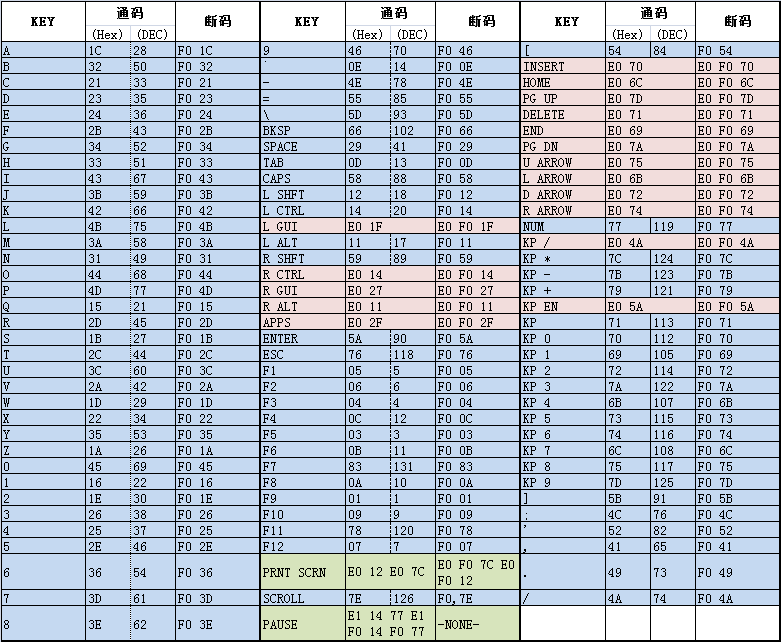

(为了简化)当一个键(A~Z)被按下或按住,就发送通码(都是f0);当一个键(A~Z)被释放,就发送断码。

键盘扫描码(实用于标准PC的101、102和104 键的键盘),按下发送通码,弹起发送断码。[2]了解即可。

2 接口定义

| 信号名称 | 方向 | 接口描述信息 |

| clk | input | 时钟信号,50MHz |

| rst_n | input | 复位信号,低电平有效 |

| ps2k_clk | input | PS/2接口时钟信号 |

| ps2k_data | input | PS/2接口数据信号 |

| rs232_tx | input | RS232发送数据信号 |

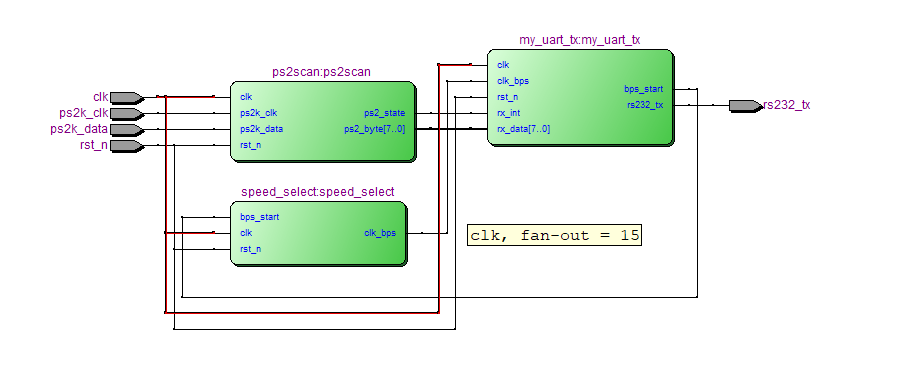

3 RTL视图

4 整体代码

Top层代码:

`timescale 1ns / 1ps// Company:

// Engineer:

//

// Create Date: 21:21:41 08/07/08

// Design Name:

// Module Name: ps2_key

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// 欢迎加入EDN的FPGA/CPLD助学小组一起讨论:http://group.ednchina.com/1375/module ps2_key(clk,rst_n,ps2k_clk,ps2k_data,rs232_tx);input clk; //50M时钟信号

input rst_n; //复位信号

input ps2k_clk; //PS2接口时钟信号

input ps2k_data; //PS2接口数据信号

output rs232_tx; // RS232发送数据信号wire[7:0] ps2_byte; // 1byte键值

wire ps2_state; //按键状态标志位wire bps_start; //接收到数据后,波特率时钟启动信号置位

wire clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点 ps2scan ps2scan( .clk(clk), //按键扫描模块.rst_n(rst_n), .ps2k_clk(ps2k_clk),.ps2k_data(ps2k_data),.ps2_byte(ps2_byte),.ps2_state(ps2_state));speed_select speed_select( .clk(clk),.rst_n(rst_n),.bps_start(bps_start),.clk_bps(clk_bps));my_uart_tx my_uart_tx( .clk(clk),.rst_n(rst_n),.clk_bps(clk_bps),.rx_data(ps2_byte),.rx_int(ps2_state),.rs232_tx(rs232_tx),.bps_start(bps_start));endmodule

ps2scan代码

`timescale 1ns / 1ps// Company:

// Engineer:

//

// Create Date: 21:25:06 08/07/08

// Design Name:

// Module Name: ps2scan

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// module ps2scan(clk,rst_n,ps2k_clk,ps2k_data,ps2_byte,ps2_state);input clk; //50M时钟信号

input rst_n; //复位信号

input ps2k_clk; //PS2接口时钟信号

input ps2k_data; //PS2接口数据信号

output[7:0] ps2_byte; // 1byte键值,只做简单的按键扫描

output ps2_state; //键盘当前状态,ps2_state=1表示有键被按下 //------------------------------------------

reg ps2k_clk_r0,ps2k_clk_r1,ps2k_clk_r2; //ps2k_clk状态寄存器//wire pos_ps2k_clk; // ps2k_clk上升沿标志位

wire neg_ps2k_clk; // ps2k_clk下降沿标志位always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginps2k_clk_r0 <= 1'b0;ps2k_clk_r1 <= 1'b0;ps2k_clk_r2 <= 1'b0;endelse begin //锁存状态,进行滤波ps2k_clk_r0 <= ps2k_clk;ps2k_clk_r1 <= ps2k_clk_r0;ps2k_clk_r2 <= ps2k_clk_r1;end

endassign neg_ps2k_clk = ~ps2k_clk_r1 & ps2k_clk_r2; //下降沿//------------------------------------------

reg[7:0] ps2_byte_r; //PC接收来自PS2的一个字节数据存储器

reg[7:0] temp_data; //当前接收数据寄存器

reg[3:0] num; //计数寄存器always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginnum <= 4'd0;temp_data <= 8'd0;endelse if(neg_ps2k_clk) begin //检测到ps2k_clk的下降沿case (num)4'd0: num <= num+1'b1;4'd1: beginnum <= num+1'b1;temp_data[0] <= ps2k_data; //bit0end4'd2: beginnum <= num+1'b1;temp_data[1] <= ps2k_data; //bit1end4'd3: beginnum <= num+1'b1;temp_data[2] <= ps2k_data; //bit2end4'd4: beginnum <= num+1'b1;temp_data[3] <= ps2k_data; //bit3end4'd5: beginnum <= num+1'b1;temp_data[4] <= ps2k_data; //bit4end4'd6: beginnum <= num+1'b1;temp_data[5] <= ps2k_data; //bit5end4'd7: beginnum <= num+1'b1;temp_data[6] <= ps2k_data; //bit6end4'd8: beginnum <= num+1'b1;temp_data[7] <= ps2k_data; //bit7end4'd9: beginnum <= num+1'b1; //奇偶校验位,不做处理end4'd10: beginnum <= 4'd0; // num清零enddefault: ;endcaseend

endreg key_f0; // 松键标志位,置1表示接收到数据8'hf0,再接收到下一个数据后清零

reg ps2_state_r; // 键盘当前状态,ps2_state_r=1表示有键被按下 always @ (posedge clk or negedge rst_n) begin //接收数据的相应处理,这里只对1byte的键值进行处理if(!rst_n) beginkey_f0 <= 1'b0;ps2_state_r <= 1'b0;endelse if(num==4'd10) begin //刚传送完一个字节数据if(temp_data == 8'hf0) key_f0 <= 1'b1;else beginif(!key_f0) begin //说明有键按下ps2_state_r <= 1'b1;ps2_byte_r <= temp_data; //锁存当前键值endelse beginps2_state_r <= 1'b0;key_f0 <= 1'b0;endendend

endreg[7:0] ps2_asci; //接收数据的相应ASCII码always @ (ps2_byte_r) begincase (ps2_byte_r) //键值转换为ASCII码,这里做的比较简单,只处理字母8'h15: ps2_asci <= 8'h51; //Q8'h1d: ps2_asci <= 8'h57; //W8'h24: ps2_asci <= 8'h45; //E8'h2d: ps2_asci <= 8'h52; //R8'h2c: ps2_asci <= 8'h54; //T8'h35: ps2_asci <= 8'h59; //Y8'h3c: ps2_asci <= 8'h55; //U8'h43: ps2_asci <= 8'h49; //I8'h44: ps2_asci <= 8'h4f; //O8'h4d: ps2_asci <= 8'h50; //P 8'h1c: ps2_asci <= 8'h41; //A8'h1b: ps2_asci <= 8'h53; //S8'h23: ps2_asci <= 8'h44; //D8'h2b: ps2_asci <= 8'h46; //F8'h34: ps2_asci <= 8'h47; //G8'h33: ps2_asci <= 8'h48; //H8'h3b: ps2_asci <= 8'h4a; //J8'h42: ps2_asci <= 8'h4b; //K8'h4b: ps2_asci <= 8'h4c; //L8'h1a: ps2_asci <= 8'h5a; //Z8'h22: ps2_asci <= 8'h58; //X8'h21: ps2_asci <= 8'h43; //C8'h2a: ps2_asci <= 8'h56; //V8'h32: ps2_asci <= 8'h42; //B8'h31: ps2_asci <= 8'h4e; //N8'h3a: ps2_asci <= 8'h4d; //Mdefault: ;endcase

endassign ps2_byte = ps2_asci;

assign ps2_state = ps2_state_r;endmodule

speed_select代码

`timescale 1ns / 1ps// Company:

// Engineer:

//

// Create Date: 17:27:40 08/28/08

// Design Name:

// Module Name: speed_select

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// module speed_select(clk,rst_n,bps_start,clk_bps);input clk; // 50MHz主时钟

input rst_n; //低电平复位信号

input bps_start; //接收到数据后,波特率时钟启动信号置位

output clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点 /*

parameter bps9600 = 5207, //波特率为9600bpsbps19200 = 2603, //波特率为19200bpsbps38400 = 1301, //波特率为38400bpsbps57600 = 867, //波特率为57600bpsbps115200 = 433; //波特率为115200bpsparameter bps9600_2 = 2603,bps19200_2 = 1301,bps38400_2 = 650,bps57600_2 = 433,bps115200_2 = 216;

*///以下波特率分频计数值可参照上面的参数进行更改

`define BPS_PARA 5207 //波特率为9600时的分频计数值

`define BPS_PARA_2 2603 //波特率为9600时的分频计数值的一半,用于数据采样reg[12:0] cnt; //分频计数

reg clk_bps_r; //波特率时钟寄存器//----------------------------------------------------------

reg[2:0] uart_ctrl; // uart波特率选择寄存器

//----------------------------------------------------------always @ (posedge clk or negedge rst_n)if(!rst_n) cnt <= 13'd0;else if((cnt == `BPS_PARA) || !bps_start) cnt <= 13'd0; //波特率计数清零else cnt <= cnt+1'b1; //波特率时钟计数启动always @ (posedge clk or negedge rst_n)if(!rst_n) clk_bps_r <= 1'b0;else if(cnt == `BPS_PARA_2) clk_bps_r <= 1'b1; // clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点else clk_bps_r <= 1'b0;assign clk_bps = clk_bps_r;endmodulemy_uart_tx代码

`timescale 1ns / 1ps// Company:

// Engineer:

//

// Create Date: 17:11:32 08/28/08

// Design Name:

// Module Name: my_uart_rx

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// module my_uart_tx(clk,rst_n,clk_bps,rx_data,rx_int,rs232_tx,bps_start);input clk; // 50MHz主时钟

input rst_n; //低电平复位信号

input clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点

input[7:0] rx_data; //接收数据寄存器

input rx_int; //接收数据中断信号,接收到数据期间始终为高电平,在此利用它的上升沿来启动发送数据

output rs232_tx; // RS232发送数据信号

output bps_start; //接收或者要发送数据,波特率时钟启动信号置位//---------------------------------------------------------

reg rx_int0,rx_int1,rx_int2; //rx_int信号寄存器,捕捉下降沿滤波用

wire pos_rx_int; // rx_int下降沿标志位always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrx_int0 <= 1'b0;rx_int1 <= 1'b0;rx_int2 <= 1'b0;endelse beginrx_int0 <= rx_int;rx_int1 <= rx_int0;rx_int2 <= rx_int1;end

endassign pos_rx_int = rx_int1 & ~rx_int2; //捕捉到上升沿后,neg_rx_int拉地保持一个主时钟周期//---------------------------------------------------------

reg[7:0] tx_data; //待发送数据的寄存器

//---------------------------------------------------------

reg bps_start_r;

reg tx_en; //发送数据使能信号,高有效

reg[3:0] num;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginbps_start_r <= 1'bz;tx_en <= 1'b0;tx_data <= 8'd0;endelse if(pos_rx_int) begin //接收数据完毕,准备把接收到的数据发出去bps_start_r <= 1'b1;tx_data <= rx_data; //把接收到的数据存入发送数据寄存器tx_en <= 1'b1; //进入发送数据状态中endelse if(num==4'd11) begin //数据发送完成,复位bps_start_r <= 1'b0;tx_en <= 1'b0;end

endassign bps_start = bps_start_r;//---------------------------------------------------------

reg rs232_tx_r;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginnum <= 4'd0;rs232_tx_r <= 1'b1;endelse if(tx_en) beginif(clk_bps) beginnum <= num+1'b1;case (num)4'd0: rs232_tx_r <= 1'b0; //发送起始位4'd1: rs232_tx_r <= tx_data[0]; //发送bit04'd2: rs232_tx_r <= tx_data[1]; //发送bit14'd3: rs232_tx_r <= tx_data[2]; //发送bit24'd4: rs232_tx_r <= tx_data[3]; //发送bit34'd5: rs232_tx_r <= tx_data[4]; //发送bit44'd6: rs232_tx_r <= tx_data[5]; //发送bit54'd7: rs232_tx_r <= tx_data[6]; //发送bit64'd8: rs232_tx_r <= tx_data[7]; //发送bit74'd9: rs232_tx_r <= 1'b1; //发送结束位default: rs232_tx_r <= 1'b1;endcaseendelse if(num==4'd11) num <= 4'd0; //复位end

endassign rs232_tx = rs232_tx_r;endmodule5 总结

代码中有详细的解释,有问题随时讨论。

知识是相互贯通的,夯实基础,才能筑高楼。欢迎大家批评指正!

参考文献

[1]特权FPGA PS2键盘解码实验

[2]PS2键盘扫描码:通码与断码 - JustXIII - 博客园

相关文章:

特权FPGA之PS/2键盘解码

0 故事背景 见过这种接口的朋友们,大概都已经成家立业了吧。不过今天我们不讨论这种接口的历史,只讲讲这种接口的设计。(如果还没有成家的朋友也别生气,做自己想做的事情就对了!) 1 时序分析 数据帧格式如图…...

SpringBoot 接口限流Lua脚本接合Redis 服务熔断 自定义注解 接口保护

介绍 Spring Boot 接口限流是防止接口被频繁请求而导致服务器负载过重或服务崩溃的一种策略。通过限流,我们可以控制单位时间内允许的请求次数,确保系统的稳定性。限流可以帮助防止恶意请求、保护系统资源,并优化 API 的可用性,避…...

FPAG_BUFFER学习

在FPGA设计中,缓冲器(Buffer)是信号传输和管理的核心组件,用于处理输入/输出信号、时钟分配以及信号完整性。以下是FPGA中常见缓冲器的详细介绍,分类说明其功能、应用场景和设计注意事项: --- ### **1. 输…...

《认知觉醒》下篇·第六章第一节“清晰:一个观念,重构你的行动力” 总结

《认知觉醒》下篇第六章第一节“清晰:一个观念,重构你的行动力”的核心内容总结: 1. 清晰的力量:行动力的第一性原理 定义 清晰是对目标、路径和结果的明确认知,是破除拖延与内耗的核心前提。 模糊的代价: …...

idea手动创建resources文件夹

有时maven没有构建成功可能造成,resources文件夹不创建的现象 此时我们可以手动创建 手动创建...

Scala相关知识学习总结6

1、集合计算高级函数说明 - 过滤:遍历集合,提取满足特定条件的元素组成新集合。 - 转化/映射(map):将集合里的每个元素应用到指定函数进行转换。 - 扁平化:文档未详细阐述其具体含义和操作。 - 扁平化映射&…...

IDEA 调用 Generate 生成 Getter/Setter 快捷键

快捷键不会用? 快捷键:AltInsert 全选键:CtrlA IDEA 调用 Generate 生成 Getter/Setter 快捷键 - 爱吃西瓜的番茄酱 - 博客园...

)

【SpringCloud】从入门到精通(下)

网关与路由 什么是网关?顾明思议,网关就是网络的关口。数据在网络间传输,从一个网络传输到另一网络时就需要经过网关来做数据的路由和转发以及数据安全的校验。 现在前端不能请求各个微服务地址,只能去请求网关 网关可以做安全控…...

深入探索 C++23:特性测试与编译器支持

文章目录 一、C23 新特性概览(一)语言特性(二)标准库特性 二、特性测试程序三、主流编译器支持情况(一)GCC(二)Clang(三)MSVC 四、开发者建议(一&…...

Electron 应用太重?试试 PakePlus 轻装上阵

Electron 作为将 Web 技术带入桌面应用领域的先驱框架,让无数开发者能够使用熟悉的 HTML、CSS 和 JavaScript 构建跨平台应用。然而,随着应用规模的扩大,Electron 应用的性能问题逐渐显现——内存占用高、启动速度慢、安装包体积庞大…...

加密与 SQL Server 建立安全连接)

驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建立安全连接

驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建立安全连接 原因描述 项目中有使用到 SQL Server 数据库, 在启动项目时, 出现报错信息: 【驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建立安全连接。错误:“The server selected protocol version…...

Java 设计模式:原型模式详解

Java 设计模式:原型模式详解 原型模式(Prototype Pattern)是一种创建型设计模式,它通过复制现有对象来创建新对象,而无需依赖其具体类。这种模式特别适合创建复杂对象或需要频繁创建相似对象的场景。本文将详细介绍原…...

——大模型训练和推理的显存估计)

NLP高频面试题(三十七)——大模型训练和推理的显存估计

在训练和推理大型语言模型时,显存(GPU 内存)的需求是一个关键考虑因素。准确估计这些需求有助于选择合适的硬件配置,确保模型高效运行。 推理阶段的显存需求 在推理过程中,显存主要用于存储模型权重和中间激活值。模型权重的显存需求可以通过以下公式估算: 模型权重…...

PHP 阿里云oss 使用指南

1.介绍 把图片放到阿里云上的空间上,可以使用cdn加速。 可以在程序里直接调用 要使用阿里云 oss sdk ,请先到阿里云下载 或用 copmposer 安装 相关链接: 安装OSS PHP SDK_对象存储(OSS)-阿里云帮助中心 composer require aliyuncs/oss…...

leetcode_面试题 02.07. 链表相交_java

面试题 02.07. 链表相交https://leetcode.cn/problems/intersection-of-two-linked-lists-lcci/ 1、题目 给你两个单链表的头节点 headA 和 headB ,请你找出并返回两个单链表相交的起始节点。如果两个链表没有交点,返回 null 。 图示两个链表在节点 c…...

空间——排序+一次遍历)

LeetCode 3375.使数组的值全部为 K 的最少操作次数:O(1)空间——排序+一次遍历

【LetMeFly】3375.使数组的值全部为 K 的最少操作次数:O(1)空间——排序一次遍历 力扣题目链接:https://leetcode.cn/problems/minimum-operations-to-make-array-values-equal-to-k/ 给你一个整数数组 nums 和一个整数 k 。 如果一个数组中所有 严格…...

紫光展锐5G SoC T8300:影像升级,「定格」美好世界

影像能力已成为当今衡量智能手机性能的重要标尺之一。随着消费者对手机摄影需求日益提升,手机厂商纷纷在影像硬件和算法上展开激烈竞争,力求为用户带来更加出色的拍摄体验。 紫光展锐专为全球主流用户打造的畅享影音和游戏体验的5G SoC——T8300&#x…...

java基础 关键字static

static static使用简介static结合类的生命周期1.加载2.链接(1) 验证(Verification)(2) 准备(Preparation)(3) 解析(Resolution) 3. 初始化4.使用5.卸载总结 staic作用总结静态变量静态代码块静态方法静态内…...

-大数据组件分析)

大数据学习(105)-大数据组件分析

🍋🍋大数据学习🍋🍋 🔥系列专栏: 👑哲学语录: 用力所能及,改变世界。 💖如果觉得博主的文章还不错的话,请点赞👍收藏⭐️留言📝支持一…...

Spark运行

一文读懂Spark:从核心概念到实战编程 在大数据处理领域,Spark凭借其高效的计算能力和灵活的架构脱颖而出。今天,就来和大家深入聊聊Spark,帮助初学者快速入门。Spark采用经典的master - slave结构。Driver如同master,…...

在macOS的docker中如何安装及运行ROS2

1、macOS环境及版本 2、docker for macos版本 3、拉取ROS2镜像 docker pull ros:iron 4、查看容器 docker images 5、启动 ROS2 容器 docker run -it --rm ros:iron -it :以交互模式运行容器。 --rm :退出时自动删除容器(测试时推荐&am…...

FFmpeg安装和使用

1. 安装与环境配置 Windows # 方法1:官网下载预编译二进制包 https://ffmpeg.org/download.html#build-windows 解压后添加bin目录到系统PATH# 方法2:通过Chocolatey安装 choco install ffmpegmacOS # 使用Homebrew安装 brew install ffmpegLinux # …...

基于多模态大模型的ATM全周期诊疗技术方案

基于多模态大模型的ATM全周期诊疗技术方案 1. 数据预处理模块 算法1:多模态数据融合伪代码 def multimodal_fusion(data_dict):# 输入:包含MRI、EEG、实验室指标的字典# 输出:对齐后的张量序列# 模态对齐aligned_data = temporal_alignment(data_dict,sampling_rate...

)

写时复制Copy-on-Write(COW)

简单理解写时复制 读的时候,直接访问原对象。 写的时候,对复制原对象,对副本进行写操作,最后将副本替换原对象。 写时复制多用于读多写少的场景,因为写操作是用悲观锁进行的,如果写的场景多,…...

S7-1200 PLC热电偶和热电阻模拟量模块

热电偶和热电阻模拟量模块 S7-1200 PLC有专用用于对温度进行采集的热电偶模块SM1231 TC和SM 1231RTD。热电偶模块有4AI和8AI两种,下面以SM1231 TC 4AI为例看一下接线图。 该模块一共有4个通道,每个通道有两个接线端子,比如0,0-。…...

)

ffmpeg函数简介(封装格式相关)

文章目录 🌟 前置说明:FFmpeg 中 AVFormatContext 是什么?🧩 1. avformat_alloc_context功能:场景: 🧩 2. avformat_open_input功能:说明:返回值: ǹ…...

操作数组的工具类

Arrays 它里面的每一个方法基本上都是static静态修饰的,如果想要调用里面的方法,不需要创建对象,直接用类名.就可以了 操作数组的工具类 方法: public static String toString(数组) 把数组拼接成…...

小刚说C语言刷题——第19讲 循环之continue和break

在循环中,当我们得到想要的答案时,这时我们可能要提前结束循环,这个时候我们就会用到break。而我们有时需要结束某一次循环时,我们可以用continue。 1.break语句 (1)在循环中想要提前终止循环,要用break。 (2)语法格…...

FairMOT复现过程中cython_bbox库问题

cython_bbox库就该这么安装_cython-bbox库就应该-CSDN博客...

记录学习的第二十四天

还是每日一题。 题解很巧,我根本想不到。 class Solution { public: int minOperations(vector<int>& nums, int k) { int count; int mnnums[0]; //接下来查找nums数组中最小值 for(int i1;i<nums.size();i) { if(nums[i]<mn) { mnnums[i]; } } …...

Kubernetes 入门篇之网络插件 calico 部署与安装

在运行kubeadm init 和 join 命令部署好master和node节点后,kubectl get nodes 看到节点都是NotReady状态,这是因为没有安装CNI网络插件。 kubectl get nodes NAME STATUS ROLES AGE VERSION k8s-master Not…...

)

HTTP 压力测试工具autocannon(AI)

简介 autocannon 是一款基于 Node.js 的高性能 HTTP 压力测试工具,适用于评估 Web 服务的并发处理能力和性能瓶颈。 一、工具特点 高性能:利用 Node.js 异步非阻塞机制模拟高并发请求。实时监控:测试过程中动态展示请求统计和性能…...

【面试】封装、继承、多态的具象示例 模板编程的理解与应用场景 链表适用的场景

文章目录 C面试:封装、继承、多态的具象示例1. 封装 (Encapsulation)2. 继承 (Inheritance)3. 多态 (Polymorphism)综合示例:封装、继承、多态 C模板编程的理解与应用场景我对模板编程的理解C中最常用的模板编程场景1. STL (标准模板库)2. 通用容器实现3…...

机器学习02——概要

一、简介 机器学习是一门在没有明确编程的情况下让计算机学习的科学。 监督学习是有目标的,输入数据对应明确的输出;无监督学习则是“探索”型的,模型的目标是从数据中发现潜在的模式或结构,而不需要预先知道标签。 二、机器学…...

常用的网络安全靶场、工具箱

转载:https://blog.csdn.net/zjzqxzhj/article/details/137945444 打CTF很好玩。可以试一下 1.CTF在线工具 1、CTF在线工具箱:http://ctf.ssleye.com/ 包含CTF比赛中常用的编码、加解密、算法。 2、CTF加解密工具箱:http://www.atoolbox.…...

)

excel中的VBA指令示例(一)

示例注释: Sub 宏1() sub是宏开头,宏1是宏的名称,自定义,在按钮中可指定用某个宏 后面是注释 Sheets("装配材料").Select ‘选择表 装配材料 Ce…...

)

神经网络 | 基于脉冲耦合神经网络PCNN图像特征提取与匹配(附matlab代码)

内容未发表论文基于脉冲耦合神经网络(PCNN)的图像特征提取与匹配研究 摘要 本文提出一种基于脉冲耦合神经网络(Pulse-Coupled Neural Network, PCNN)的图像特征提取与匹配方法。通过模拟生物视觉皮层神经元的脉冲同步发放特性,PCNN能够有效捕捉图像纹理与边缘特征。实验表…...

Linux 内核中的 TCP 早期多路分解机制解析

一、引言 在现代高性能网络环境中,Linux 内核需要快速处理大量的 TCP 数据包,同时保持低延迟和高吞吐量。为了实现这一目标,Linux 内核引入了 早期多路分解(Early Demultiplexing) 机制。这种机制允许内核在数据包进入传输层之前,快速找到对应的套接字(socket)并关联数…...

——错误类型)

Yalmip工具箱(3)——错误类型

在yalmip中,不可避免地我们会遇到求解出问题的情况,理解和处理错误信息是至关重要的环节。在这里我们查看yalmip的所有错误类型(详细见 yalmiperror.m 函数) 函数概述 yalmiperror函数的主要作用是根据YALMIP产生的错误代码&…...

【KWDB 创作者计划】_KWDB:开源引领数据库创新变革

在数字化浪潮汹涌澎湃的当下,数据已然成为驱动各行各业发展的核心要素。数据库作为数据管理的关键工具,其性能、功能以及开放性,对企业和社会的数字化进程起着举足轻重的作用。KWDB,作为数据库领域的一颗璀璨新星,正以…...

HarmonyOS学习 实验八:显式动画与属性动画的实现

鸿蒙系统动画开发实战:显式动画与属性动画的探索 引言 在鸿蒙系统的开发过程中,动画效果是提升用户体验的重要一环。通过巧妙运用动画,可以使应用界面更加生动、交互更加流畅。鸿蒙系统提供了丰富的动画开发能力,其中显式动画和…...

高校智慧能源系统解决方案:推动绿色校园建设的智能化实践

高校智慧能源系统解决方案:推动绿色校园建设的智能化实践 一、建设背景:政策驱动与绿色发展需求 为响应国家“碳达峰、碳中和”战略目标,教育部印发《绿色低碳发展国民教育体系建设实施方案》,明确提出需完善校园能源管理体系&a…...

win日志

以第一个为例子 打开后,右上角(将所有事件另存为xx)然后一般写今天的日期,进行备份 然后选择下语言即可 日志备份时间的选择(根据实际情况选择日志时间) 点击右侧事件属性,然后xml视图即可 常见的安全事件…...

与LED灯的故事)

嵌入式开发之51单片机入门(一)与LED灯的故事

得而不惜就该死。 --小泽 继续傻冒开始,这次的傻冒之旅是关于嵌入式的51单片机开发,这个系列只讲程序开发逻辑,如需初始环境安装配置,建议移步B站江协科技大佬,本系列也是对大佬所讲内容的复刻,同时添加一…...

TCP 与 UDP

TCP 与 UDP 的区别(重要) 是否面向连接:UDP 在传送数据之前不需要先建立连接。而 TCP 提供面向连接的服务,在传送数据之前必须先建立连接,数据传送结束后要释放连接。是否是可靠传输:远地主机在收到 UDP 报…...

Linux:进程地址空间

在讲述本篇文章之前,我们先来看一段代码。 从上图输出可以看到,我们的子进程继承了父进程的全局变量val,当子进程中的val产生了修改时,父进程的val值并没有变化,但父子进程在打印val的地址时,会发现val的地…...

【Linux】Linux 操作系统 - 03 ,初步指令结尾 + shell 理解

文章目录 前言一、打包和压缩二、有关体系结构 (考)面试题 三、重要的热键四、shell 命令及运行原理初步理解五、本节命令总结总结 前言 本篇文章 , 笔者记录的笔记内容包含 : 基础指令 、重要热键 、shell 初步理解 、权限用户的部分问题 。 内容皆是重要知识点 , 需要认真理…...

华为数通不同级别的认证路径和要求是什么?

一、认证路径 HCIA:无需前置认证,通过一门考试(代码H12-811)即可拿证。 HCIP:建议先通过HCIA-Datacom,再选择子方向(如高级路由、安全)。 HCIE:最好有hcia/hcip的基础…...

电子电气架构 --- 新能源汽车电子电气系统功能需求

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。 老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师: 周末洗了一个澡,换了一身衣服,出了门却不知道去哪儿,不知道去找谁,漫无目的走着,大概这就是成年人最深的孤独吧! 旧人不知我近况,新人不知我过…...

《从单体到分布式:一个订单系统的架构升级》

1. 问题爆发:单体架构的极限 原来的订单系统长这样: 技术栈:SpringBoot MyBatis MySQL(主从)部署:单机跑所有模块(订单、支付、库存)痛点ÿ…...