特权FPGA之UART串口

0.简介

通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。一般UART由专用芯片如8250,16450来实现,但专用芯片引脚都较多,内含许多辅助功能,在实际使用时往往只需要用到UART的基本功能,使用专用芯片会造成资源浪费和成本提高。

一般而言UART和外界通信只需要两条信号线RXD和TXD,其中RXD是UART的接收端,TXD是UART的发送端,接收与发送是全双工形式。由于可编程逻辑器件技术的快速发展,FPGA的功能日益强大,其开发周期短、可重复编程的优点也越来越明显,在FPGA芯片上集成UART功能模块并和其他模块组合可以很方便地实现一个能与其他设备进行串行通信的片上系统。

FPGA(Field Programmable Gate Array)现场可编程门阵列在数字电路的设计中已经被广泛使用。这种设计方式可以将以前需要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活性。[1]

1. Uart时序

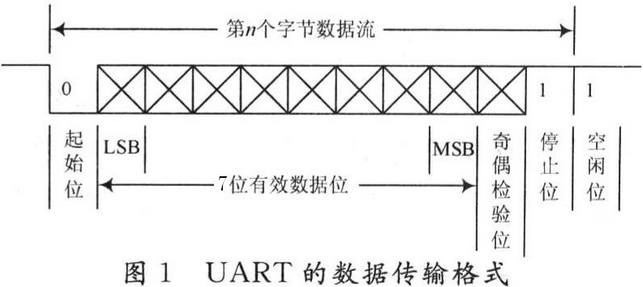

UART的一帧由四部分组成起始位(1bit),数据位(6\7\8bit),奇偶校验位(1bit),停止位(1\1.5\2bit)

uart 是将传输数据的每个字符一位接一位地传输。 其中每一位(Bit)的意义如下:

空闲位:高电平,表明当前无传输事务。

起始位:一位低电平信号,标志着数据传输的开始。

数据位:紧接着起始位之后。数据位的个数可以是 6、7、8 等,构 成一个字符。通常采用 ASCII 码。从最低位开始传送,依靠时钟定位。

奇偶校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或 奇数(奇校验),以此来校验数据传送的正确性。

停止位:一个字符数据的结束标志。可以是 1 位、1.5 位、2 位的高电平。

由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通 信中两台设备间出现了小小的不同步。因此停止位不仅仅是表示传输的结束, 并且提供计算机校正时钟同步的机会。停止位的位数越多,不同时钟同步的容 忍程度越大,但是数据传输率同时也越慢。[2]

1.1 通信协议

UART(Universal Asynchronous Receiver/Transmitter),通用异步收发器,是一种异步全双工串行通信协议,可实现单工通信、半双工通信和全双工通信。

单工通信方式:主机只能发送数据,从机只能接收数据,数据流向始终由发送端流向接收端;

半双工通信方式:同一时刻,只能由主机向从机或从机向主机发送数据;

全双工通信方式:同一时刻,主机和从机都可以互发数据。

想实现奇偶校验功能的朋友,可以参考下面的代码[4]:

test

用以确定奇偶校验,其中0为无校验位,1为偶校验,2为奇校验

case(test)2'b00 : test_reg <= 1'b0;2'b01 : test_reg <= !(^rx_out_reg);2'b10 : test_reg <= (^rx_out_reg);default : test_reg <= 1'b0;endcase

- 1、无校验(no parity)。

- 2、奇校验(odd parity):如果数据位中“1”的数目是偶数,则校验位为“1”,如果“1”的数目是奇数,校验位为“0”。

- 3、偶校验(even parity):如果数据为中“1”的数目是偶数,则校验位为“0”,如果为奇数,校验位为“1”。[5]

2. 串口的物理层

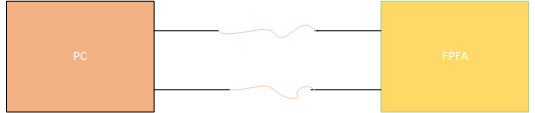

UART通信只有两根信号线,一根是发送数据端口线叫tx(Transmitter),一根是接收数据端口线叫rx(Receiver),如图所示,对于PC来说它的tx要和对于FPGA来说的rx连接,同样PC的rx要和FPGA的tx连接,如果是两个tx或者两个rx连接那数据就不能正常被发送出去和接收到[6]。

3 Top层代码实现:

`timescale 1ns / 1psmodule my_uart_top(clk,rst_n,rs232_rx,rs232_tx);input clk ; // 50MHz主时钟

input rst_n ; // 低电平复位信号input rs232_rx ; // RS232接收数据信号

output rs232_tx ; // RS232发送数据信号wire bps_start1,bps_start2; // 接收到数据后,波特率时钟启动信号置位,高电平有效

wire clk_bps1,clk_bps2; // clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点

wire[7:0] rx_data; // 接收数据寄存器,保存直至下一个数据来到

wire rx_int; // 接收数据中断信号,接收到数据期间始终为高电平speed_select speed_rx( .clk(clk), //波特率选择模块.rst_n(rst_n),.bps_start(bps_start1),.clk_bps(clk_bps1));my_uart_rx my_uart_rx( .clk(clk), //接收数据模块.rst_n(rst_n),.rs232_rx(rs232_rx),.rx_data(rx_data),.rx_int(rx_int),.clk_bps(clk_bps1),.bps_start(bps_start1));///

speed_select speed_tx( .clk(clk), //波特率选择模块.rst_n(rst_n),.bps_start(bps_start2),.clk_bps(clk_bps2));my_uart_tx my_uart_tx( .clk(clk), //发送数据模块.rst_n(rst_n),.rx_data(rx_data),.rx_int(rx_int),.rs232_tx(rs232_tx),.clk_bps(clk_bps2),.bps_start(bps_start2));endmodule

speed_select代码

`timescale 1ns / 1psmodule speed_select(clk,rst_n,bps_start,clk_bps);input clk ; // 50MHz主时钟

input rst_n ; //低电平复位信号

input bps_start ; //接收到数据后,波特率时钟启动信号置位

output clk_bps ; // clk_bps的高电平为接收或者发送数据位的中间采样点 /*

parameter bps9600 = 5207, //波特率为9600bpsbps19200 = 2603, //波特率为19200bpsbps38400 = 1301, //波特率为38400bpsbps57600 = 867, //波特率为57600bpsbps115200 = 433; //波特率为115200bpsparameter bps9600_2 = 2603,bps19200_2 = 1301,bps38400_2 = 650,bps57600_2 = 433,bps115200_2 = 216;

*///以下波特率分频计数值可参照上面的参数进行更改

`define BPS_PARA 5207 //波特率为9600时的分频计数值

`define BPS_PARA_2 2603 //波特率为9600时的分频计数值的一半,用于数据采样reg[12:0] cnt ; //分频计数

reg clk_bps_r ; //波特率时钟寄存器//----------------------------------------------------------

//reg[2:0] uart_ctrl ; // uart波特率选择寄存器

//----------------------------------------------------------always @ (posedge clk or negedge rst_n)if(!rst_n) cnt <= 13'd0;else if((cnt == `BPS_PARA) || !bps_start) cnt <= 13'd0; //波特率计数清零,bps_start信号来自uart_rx模块的输出else cnt <= cnt+1'b1; //波特率时钟计数启动always @ (posedge clk or negedge rst_n)if(!rst_n) clk_bps_r <= 1'b0;else if(cnt == `BPS_PARA_2) clk_bps_r <= 1'b1; // clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点else clk_bps_r <= 1'b0;assign clk_bps = clk_bps_r;endmodulemy_uart_rx代码

`timescale 1ns / 1psmodule my_uart_rx(clk,rst_n,rs232_rx,rx_data,rx_int,clk_bps,bps_start);input clk ; // 50MHz主时钟

input rst_n ; // 低电平复位信号

input rs232_rx ; // RS232接收数据信号,可以是仿真输入激励产生

input clk_bps ; // clk_bps的高电平为接收或者发送数据位的中间采样点

output bps_start ; // 接收到数据后,波特率时钟启动信号置位

output[7:0] rx_data ; // 接收数据寄存器,保存直至下一个数据来到

output rx_int ; // 接收数据中断信号,接收到数据期间始终为高电平//----------------------------------------------------------------

reg rs232_rx0,rs232_rx1,rs232_rx2,rs232_rx3 ; //接收数据寄存器,滤波用

wire neg_rs232_rx ; //表示数据线接收到下降沿always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrs232_rx0 <= 1'b0;rs232_rx1 <= 1'b0;rs232_rx2 <= 1'b0;rs232_rx3 <= 1'b0;endelse beginrs232_rx0 <= rs232_rx;rs232_rx1 <= rs232_rx0;rs232_rx2 <= rs232_rx1;rs232_rx3 <= rs232_rx2;end

end

//下面的下降沿检测可以滤掉<20ns-40ns的毛刺(包括高脉冲和低脉冲毛刺),

//这里就是用资源换稳定(前提是我们对时间要求不是那么苛刻,因为输入信号打了3拍)

//(当然我们的有效低脉冲信号肯定是远远大于40ns的)

assign neg_rs232_rx = rs232_rx3 & rs232_rx2 & ~rs232_rx1 & ~rs232_rx0; //接收到下降沿后neg_rs232_rx置高一个时钟周期//----------------------------------------------------------------

reg bps_start_r ;

reg[3:0] num ; //移位次数

reg rx_int ; //接收数据中断信号,接收到数据期间始终为高电平always @ (posedge clk or negedge rst_n)if(!rst_n) beginbps_start_r <= 1'bz;rx_int <= 1'b0;endelse if(neg_rs232_rx) begin //接收到串口接收线rs232_rx的下降沿标志信号,起始位信号拉低bps_start_r <= 1'b1; //启动串口准备数据接收rx_int <= 1'b1; //接收数据中断信号使能endelse if(num==4'd12) begin //接收完有用数据信息,1bit start +8bit数据 + 没有奇偶检验 +2bit停止位=11, 12是空闲位bps_start_r <= 1'b0; //数据接收完毕,释放波特率启动信号rx_int <= 1'b0; //接收数据中断信号关闭endassign bps_start = bps_start_r;//----------------------------------------------------------------

reg[7:0] rx_data_r; //串口接收数据寄存器,保存直至下一个数据来到

//----------------------------------------------------------------reg[7:0] rx_temp_data; //当前接收数据寄存器always @ (posedge clk or negedge rst_n)if(!rst_n) beginrx_temp_data <= 8'd0;num <= 4'd0;rx_data_r <= 8'd0;endelse if(rx_int) begin //接收数据处理if(clk_bps) begin //读取并保存数据,接收数据为一个起始位,8bit数据,1或2个结束位 num <= num+1'b1; // 跳过第一个num,起始位case (num) // 然后是8bit的数据,先发送低bit数据,再发送高bit数据4'd1: rx_temp_data[0] <= rs232_rx; //锁存第0bit4'd2: rx_temp_data[1] <= rs232_rx; //锁存第1bit4'd3: rx_temp_data[2] <= rs232_rx; //锁存第2bit4'd4: rx_temp_data[3] <= rs232_rx; //锁存第3bit4'd5: rx_temp_data[4] <= rs232_rx; //锁存第4bit4'd6: rx_temp_data[5] <= rs232_rx; //锁存第5bit4'd7: rx_temp_data[6] <= rs232_rx; //锁存第6bit4'd8: rx_temp_data[7] <= rs232_rx; //锁存第7bitdefault: ; // 不用careendcaseendelse if(num == 4'd12) begin //我们的标准接收模式下只有1+8+1(2)=11bit的有效数据num <= 4'd0; //TQ老师说接收到STOP位后结束,num清零,FIXME:这里的代码有歧义rx_data_r <= rx_temp_data; //把数据锁存到数据寄存器rx_data中endendassign rx_data = rx_data_r; endmodule

uart_tx代码

`timescale 1ns / 1psmodule my_uart_tx(clk,rst_n,rx_data,rx_int,rs232_tx,clk_bps,bps_start);input clk; // 50MHz主时钟

input rst_n; // 低电平复位信号

input clk_bps; // clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点

input [7:0] rx_data; //接收数据寄存器

input rx_int; //接收数据中断信号,接收到数据期间始终为高电平,在该模块中利用它的下降沿来启动串口发送数据

output rs232_tx; // RS232发送数据信号

output bps_start; //接收或者要发送数据,波特率时钟启动信号置位//---------------------------------------------------------

reg rx_int0,rx_int1,rx_int2; //rx_int信号寄存器,捕捉下降沿滤波用

wire neg_rx_int; // rx_int下降沿标志位always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrx_int0 <= 1'b0;rx_int1 <= 1'b0;rx_int2 <= 1'b0;endelse beginrx_int0 <= rx_int;rx_int1 <= rx_int0;rx_int2 <= rx_int1;end

endassign neg_rx_int = ~rx_int1 & rx_int2; //捕捉到下降沿后,neg_rx_int拉高保持一个主时钟周期//---------------------------------------------------------

reg[7:0] tx_data; //待发送数据的寄存器

//---------------------------------------------------------

reg bps_start_r;

reg tx_en; //发送数据使能信号,高有效

reg[3:0] num;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginbps_start_r <= 1'bz;tx_en <= 1'b0;tx_data <= 8'd0;endelse if(neg_rx_int) begin //接收数据完毕,准备把接收到的数据发回去bps_start_r <= 1'b1 ;tx_data <= rx_data ; //把接收到的数据存入发送数据寄存器tx_en <= 1'b1 ; //进入发送数据状态中endelse if(num==4'd11) begin //数据发送完成,复位bps_start_r <= 1'b0;tx_en <= 1'b0;end

endassign bps_start = bps_start_r;//---------------------------------------------------------

reg rs232_tx_r;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginnum <= 4'd0;rs232_tx_r <= 1'b1;endelse if(tx_en) beginif(clk_bps) beginnum <= num+1'b1;case (num)4'd0: rs232_tx_r <= 1'b0; //发送起始位4'd1: rs232_tx_r <= tx_data[0]; //发送bit04'd2: rs232_tx_r <= tx_data[1]; //发送bit14'd3: rs232_tx_r <= tx_data[2]; //发送bit24'd4: rs232_tx_r <= tx_data[3]; //发送bit34'd5: rs232_tx_r <= tx_data[4]; //发送bit44'd6: rs232_tx_r <= tx_data[5]; //发送bit54'd7: rs232_tx_r <= tx_data[6]; //发送bit64'd8: rs232_tx_r <= tx_data[7]; //发送bit74'd9: rs232_tx_r <= 1'b1; //发送结束位default: rs232_tx_r <= 1'b1; //空闲位拉高endcaseendelse if(num==4'd11) num <= 4'd0; //复位end

endassign rs232_tx = rs232_tx_r;endmodule特权老师实现的代码,比较简单些,没有用到奇偶校验位,也没有用到FIFO。功能基本上都已经实现了。

总结

人生总会起起伏伏,总有一篇文章,适合你!加油!期待明天美好的事情发生!

参考文献:

[1]FPGA——UART Verilog程序设计_uart verilog状态转移图-CSDN博客

[2]Verilog UART串口详解(代码及整体思路)-CSDN博客

[3]【Verilog实战】UART通信协议,半双工通信方式(附源码)_uart 半双工-CSDN博客

[4]【数字IC】从零开始的Verilog UART设计_ic数字前端verilog设计-CSDN博客

[5]【FPGA协议篇】UART通信及其verilog实现(代码采用传参实现模块通用性,适用于快速开发)_fpga 串口波特率-CSDN博客

[6]FPGA实现串口(UART)_fpga uart-CSDN博客

相关文章:

特权FPGA之UART串口

0.简介 通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。一般UART由专用芯片如8250,1645…...

oracle 索引失效

在 Oracle 11g 中,索引失效的常见原因包括函数修改列、隐式类型转换、统计信息过时等,解决方法需结合版本特性(如虚拟列、索引跳跃扫描)。通过执行计划分析、统计信息维护和合理使用提示(Hints),…...

MySQL查看binlog执行情况

因数据丢失,被要求使用binlog查看 执行SQL的具体情况。 拿到数据库压缩包,解压缩获得文件和文件夹若干。 如图,有17个binlog文件,目标数据库名应为corr。 已知这个数据库是安装在windows下,版本8.0. 先下载一个mysq…...

kotlin,Android,jetpack compose,日期时间设置

AI生成,调试出来学习,这些小组件会用了,就可以组合一个大点的程序了。 package com.example.mydatetimeimport android.app.AlertDialog import android.os.Bundle import androidx.activity.ComponentActivity import androidx.activity.co…...

sql-labs靶场 less-2

文章目录 sqli-labs靶场less 2 联合注入 sqli-labs靶场 每道题都从以下模板讲解,并且每个步骤都有图片,清晰明了,便于复盘。 sql注入的基本步骤 注入点注入类型 字符型:判断闭合方式 (‘、"、’、“”…...

ssh密钥连接远程服务器并用scp传输文件

ssh密钥连接远程服务器 私钥的权限必须是600chmod 600 id_rsa连接时在命令中加上私钥的地址ssh -i PATH_to_id_rsa usernameip -p port scp -P port -i PATH_to_id_rsa file usernameip:PATH...

)

【锂电池SOH预测】PSO-BP锂电池健康状态预测,锂电池SOH预测(Matlab完整源码和数据)

预测效果 基于PSO-BP算法的锂电池健康状态预测研究 一、引言 1.1 研究背景与意义 在当今社会,锂电池凭借其高能量密度、长寿命及环境友好等特性,在现代能源系统中占据着举足轻重的地位。从消费电子领域如智能手机、笔记本电脑,到动力领域中…...

找搭子系统 搭子经济新风口 基于精准匹配的社交新生态探索

一、市场前景:为什么现在需要"找搭子"? 孤独经济爆发 超60%年轻人存在"精准陪伴"需求(2024社交报告) 传统社交App无法满足"非婚恋、非熟人"的中间态需求 线下活动复苏 剧本杀/飞盘等兴趣活动年增…...

《Spring Boot+策略模式:企业级度假订单Excel导入系统的架构演进与技术实现》

前言 在数字化时代背景下,订单管理系统的高效性与灵活性成为企业竞争力的核心要素。本文档详细剖析了一个基于 策略模式 的度假订单导入系统,通过分层架构设计实现了多源异构数据的标准化处理。系统以 Spring Boot 为核心框架,结合 MyBatis …...

软件需求分析习题汇编

需求工程练习题 一、选择题 1. 软件需求规格说明书的内容不应包括对( )的描述。 A. 主要功能B. 算法的详细过程C. 用户界面及运行环境D. 软件的性能 *正确答案:*B:算法的详细过程; 2. 需求分析最终结果是产生( ) A. 项目开发…...

51单片机的汇编伪指令

目录 一、ORG 汇编起始地址命令 1、功能 2、语法格式 3、使用示例 4、注意事项 二、END 汇编终止命令 1、功能 2、语法格式 3、使用示例 4、注意事项 三、EQU 赋值命令 1、功能 2、语法格式 3、使用示例 4、注意事项 四、BIT 位定义命令 1、功能 2、语法格式…...

深入探究Python的re模块及其在爬虫中的应用

深入探究Python的re模块及其在爬虫中的应用 一、引言 在Python的强大生态系统中,re模块作为处理正则表达式的核心工具,发挥着举足轻重的作用。正则表达式是一种描述文本模式的强大语言,能够高效地进行字符串的匹配、查找、替换等操作。无论…...

aosp13增加摄像头控制功能实现

A13中,可以要求做一个开关来控制摄像头是否可用,约束所有使用摄像头的应用。思路:设置中增加开关设置一个属性值,在摄像头调用实现层增该值判断即可 一 开关的开发: 设置-安全中增加开关选项 代码部分&#x…...

Kotlin 之 vararg 参数向下传递的几种方式

在 Kotlin 中,vararg 参数是一种特殊的参数类型,用于表示可变数量的参数。vararg 参数是否可以向下传递,需要根据目标方法的参数类型来决定。 1、目标方法参数也是vararg类型,可直接向下传递 在 method 方法中,通过 …...

Kotlin学习

kotlin android 开源,Kotlin开源项目集合_晚安 呼-华为开发者空间 干货来袭,推荐几款开源的Kotlin的Android项目...

AI写程序:图片批量重命名工具 - 自动化整理您的图片库

图片批量重命名工具 - 自动化整理您的图片库 GitHub项目地址: https://github.com/dependon/renameImage 项目介绍 这是一个基于Python开发的图形界面工具,用于批量重命名文件夹中的图片文件。它能够递归处理选定文件夹及其所有子文件夹中的图片,按照…...

git命令自动拉去远程分支到本地

是的,可以通过 Git 命令自动拉取远程分支并在本地创建同名分支。以下是几种方法: 方法 1:直接拉取远程分支并创建同名本地分支 git fetch origin <远程分支名> # 拉取远程分支 git checkout -b <本地分支名> origin/<远程分…...

[创业之路-364]:穿透表象:企业投资的深层逻辑与误区规避

前言: 透过现象看本质 企业一生与人生相似 看企业如同看人 三岁看大,七岁看老 三十年河东,三十年河西 企业也有品行、文化、气质、性格、赚钱、生命周期与赚钱曲线 投资公司的目的是未来赚钱,赚未来赚钱。投资创业中的企业主要看…...

UE5 蓝图里的声音

文章目录 支持的格式设置循环播放在场景中放置音频设置音频的衰减与不衰减在UI动画中播放声音使用蓝图节点播放声音按钮本身就可以播放声音 支持的格式 支持:WAV 不支持:MP3 设置循环播放 双击音频,打开音频设置,勾选Looping …...

Spring Boot 邮件发送配置遇到的坑:解决 JavaMailSenderImpl 未找到的错误

在使用 Spring Boot 开发时,我们经常需要通过邮件发送功能来实现某些业务逻辑。为了方便快速集成,Spring Boot 提供了一个非常好用的 spring-boot-starter-mail 模块,帮助我们轻松发送邮件。但是,在配置过程中可能会遇到一些问题&…...

路由表的最终地址 root 路由跟踪,最终到哪里去

在路由跟踪(如tranceroute或trancert命令)中,最终地址是目标主机或服务器的IP地址或域名所对应的实际网络地址; 路由跟踪的目的是显示数据包从本地主机到目标主机所经过的每一跳路由器或网络节点,而最终地址是数据包要到达的目标设备。 1.路由跟踪的最终地址 目标主机:路…...

:镜像打包、容器运行与高频问题解析)

Docker面试全攻略(一):镜像打包、容器运行与高频问题解析

引言 在云原生和微服务架构盛行的今天,Docker 已成为后端开发的必备技能。本文从 面试高频考点 出发,系统梳理 Docker 镜像构建、容器运行的核心知识点,助你轻松应对 Docker 相关的技术面试! 一、Docker 镜像构建核心(面试必问) 1. Dockerfile 核心命令与参数 FROM:基…...

方法的重写

目录 1、重写的概念2、方法重写的规则3、重写 VS 重载 1、重写的概念 重写,也称为覆盖,是子类对父类的非构造、非静态、非 final 修饰、非 private 修饰的方法的实现过程的重新编写。重写可以让子类根据需要来实现父类的方法。方法重写是子类与父类的一…...

搭建hadoop集群模式并运行

3.1 Hadoop的运行模式 先去官方看一看Apache Hadoop 3.3.6 – Hadoop: Setting up a Single Node Cluster. 本地模式:数据直接存放在Linux的磁盘上,测试时偶尔用一下 伪分布式:数据存放在HDFS,公司资金不足的时候用 完全分布式&a…...

)

【学Rust写CAD】39 over_in_in 函数(alpha256补充方法)

源码 // Similar to over_in but includes an additional clip alpha value#[inline]pub fn over_in_in(self,src: Argb, dst: Argb, clip: Alpha) -> Argb {let src_alpha self * clip;let dst_alpha !(src_alpha*src.alpha_t());// we sum src and dst before reducing…...

Visual Studio 2022 UI机器学习训练模块

VS你还是太超标了,现在机器学习都不用写代码了吗!! 右键项目解决方案,选择机器学习模型...

c# 企业级ADB通信示例

using System; using System.Collections.Generic; using System.Diagnostics; using System.Linq; using System.Text; using System.Threading.Tasks;namespace ADB_Demo {/// <summary>/// ADB管理器,提供与Android设备的通信功能/// </summary>publ…...

linux上todesk无法使用问题

安装 x11 查看是否已安装 X11 dpkg -l | grep xserver-xorg-core 安装 X11,大概需要 17 - 222 MB(前者是在服务器上装,后者在自己的 WSL 装,具体视情况而定) sudo apt-get install xorg sudo apt-get install xauth s…...

数字IC后端项目典型问题之后端实战项目问题记录

Q1:为了更高效过掉Calibre LVS,我们要求学员在chipfinish阶段需要先做Online LVS检查。该学员在做verifyConnectivity检查发现设计中存在大量的M1 VDD_CORE Un-Connect Pin的violation,具体violation如下图所示。 数字后端培训实战项目六大典型后端实现…...

【机器学习】决策树

一、什么是决策树? 想象一下你玩“二十个问题”游戏的场景,你通过问一系列“是”或“否”的问题来猜测对方心中的物体。决策树的工作方式与此非常相似。它本质上是一个流程图结构,其中: 每个内部节点(Internal Node&…...

大模型格式化输出的几种方法

大模型格式化输出的几种方法 在开发一些和LLM相关的应用的时候,如何从大模型的反馈中拿到结构化的输出数据是非常重要的,那么本文就记录几种常用的方法。 OpenAI提供的新方法 在 OpenAI 的 Python 库中,client.beta.chat.completions.parse 是一个用于生成结构化输出的方法…...

250408_解决加载大量数据集速度过慢,耗时过长的问题

250408_解决加载Cifar10等大量数据集速度过慢,耗时过长的问题(加载数据时多线程的坑) 在做Cifar10图像分类任务时,发现每个step时间过长,且在资源管理器中查看显卡资源调用异常,主要表现为,显卡…...

Linux网络多进程并发服务器和多线程并发服务器

多进程 还是以大小写转换为例子 #include <stdio.h> #include <stdlib.h> #include <string.h> #include <unistd.h> #include <pthread.h> #include <sys/socket.h> #include <arpa/inet.h> #include "wrap.h" #include…...

模型微调专题(中))

LLMs基础学习(五)模型微调专题(中)

文章目录 LLMs基础学习(五)模型微调专题(中)Adapter 类的微调1 背景2 技术原理3 具体细节4 Adapter 类其他方法的微调 Prefix 类的微调1 Prefix Tuning2 Prompt Tuning3 P - tuning4 P - Tuning v25 总结 LoRA 篇a. 什么是 LoRA?…...

不同路由器网段之间的组建

实现PC1到PC7之间的通信 先将基础的ip都配置好 在AR6中将跳板配置好,ip route-static 192.168.5.0 24 64.1.1.2 在AR3中将跳板配置好,ip route-static 192.168.1.0 24 64.1.1.1 如此我们将可以实现通信了 还有第二种,实现PC1到…...

java设计模式-建造者模式

建造者模式(build) 建造者模式的四个角色 1、Product(产品角色): 一个具体的产品对象。 2、Builder(抽象建造者): 创建一个Product对象的各个部件指定的 接口或者抽象类。 3、ConcreteBuild(具体建造者):实现接口,构建和装配各个部…...

【泛函分析】

E.Kreyszig, Introductory functional analysis with applications, Wiley, 1989 1.1 Metric space 满足下面四个性质的映射称为度量:正定、0、对称性和三角不等式 推论:广义的三角不等式 度量可以看成一个映射,验证欧式距离&am…...

【NLP 面经 6】

当上帝赐予你荒野时,就意味着,他要你成为高飞的鹰 —— 25.4.3 一、机器翻译任务,Transformer结构模型改进 在自然语言处理的机器翻译任务中,你采用基于 Transformer 架构的模型。在翻译一些具有丰富文化内涵、习语或隐喻的句子时…...

地质科研智能革命:当大语言模型“扎根”地质现场、大语言模型本地化部署与AI智能体协同创新实践

在地质学迈向“深时数字地球”(Deep-time Digital Earth)的进程中,传统研究方法正面临海量异构数据(地质图件、遥感影像、地震波谱等)的解析挑战。大语言模型(LLM)与AI智能体的本地化部署技术&a…...

)

蓝桥王国(Dijkstra优先队列)

问题描述 小明是蓝桥王国的王子,今天是他登基之日。 在即将成为国王之前,老国王给他出了道题,他想要考验小明是否有能力管理国家。 题目的内容如下: 蓝桥王国一共有 N 个建筑和 M 条单向道路,每条道路都连接着两个…...

美团mtgsig1.1 分析 mtgsig

声明 本文章中所有内容仅供学习交流使用,不用于其他任何目的,抓包内容、敏感网址、数据接口等均已做脱敏处理,严禁用于商业用途和非法用途,否则由此产生的一切后果均与作者无关! 逆向过程 mtgsig有问题的请求3次左右…...

基于STM32、HAL库的CH224Q快充协议芯片简介及驱动程序设计

一、简介: CH224Q是一款USB Type-C快充协议芯片,支持多种快充协议,包括: USB PD 3.0 QC4 QC3.0/2.0 AFC FCP SCP APPLE 2.4A BC1.2 该芯片通过I2C接口与主控MCU通信,可以灵活配置输出电压和获取充电状态信息…...

—— 浅层路由和 Packaging)

SvelteKit 最新中文文档教程(18)—— 浅层路由和 Packaging

前言 Svelte,一个语法简洁、入门容易,面向未来的前端框架。 从 Svelte 诞生之初,就备受开发者的喜爱,根据统计,从 2019 年到 2024 年,连续 6 年一直是开发者最感兴趣的前端框架 No.1: Svelte …...

蓝桥杯-数字诗意

问题描述 在诗人的眼中,数字是生活的韵律,也是诗意的表达。 小蓝,当代顶级诗人与数学家,被赋予了"数学诗人"的美誉。他擅长将冰冷的数字与抽象的诗意相融合,并用优雅的文字将数学之美展现于纸上。 某日&a…...

深入探索 Node.js 文件监听机制:从前端工程化到原理剖析

在现代化前端开发中,文件监听(File Watching)是实现高效开发体验的核心技术之一。从 webpack 的热模块替换到 Vite 的即时刷新,从 CSS 预处理到静态资源打包,背后都依赖于稳健的文件监听机制。本文将深入探讨基于 Node…...

2025 年河北交安安全员考试:巧用行业报告丰富知识储备

河北交通行业发展迅速,各类行业报告蕴含大量有价值信息。考生可从河北省交通运输行业发展报告、安全专项检查报告等资料入手。在行业发展报告中,了解本省交通建设规模、重点项目规划等内容,这些信息与交安安全员工作紧密相关。比如࿰…...

Java9新特性

新的Jshell Java9引入了交互式编程工具jshell,可用于快速测试和学习Java。 特性 该工具可用于快速测试代码片段,无需创建java文件。支持自动补全和历史命令支持保存和加载会话 不可变集合工厂方法 Java9新增了List.of()、Set.of()、Map.of()和Map.o…...

?)

CS内网渗透 - 如何通过冰蝎 Webshell 上线 Weblogic 服务器到 Cobalt Strike 并绕过杀软检测(360、火绒)?

目录 1. 冰蝎连接上 Weblogic 服务器如何上线到 Cobalt Strike 2. 服务器安装杀毒工具如何绕过杀软上线到 Cobalt Strike 2.1 杀软对 Webshell 命令执行的检测及绕过 2.2 杀软对 Cobalt Strike 上线木马的检测及绕过 2.3 杀软对这两方面的限制及综合绕过 3. 如何生成免杀…...

Linux开发过程中常用命令整理

docker ps -a查看所有(包括已经停止的) systemctl 功能:控制系统服务的启动关闭等 语法:systemctl start | stop | restart | disable | enable | status 服务名 start,启动stop,停止status,查看状态disable…...

触想工业一体机助力打造安全智能的数字化配电系统

一、项目开发背景 现代社会运行依赖稳定的电力供应,尤其在工业生产、城市基础设施、商业建筑等关键领域,即便是0.1秒的电力中断也可能导致严重后果。同时,随着全球用电负荷加剧及能源结构转型,对电力系统的运维效率、能源利用和数…...