FPGA_DDR(一) 仿真

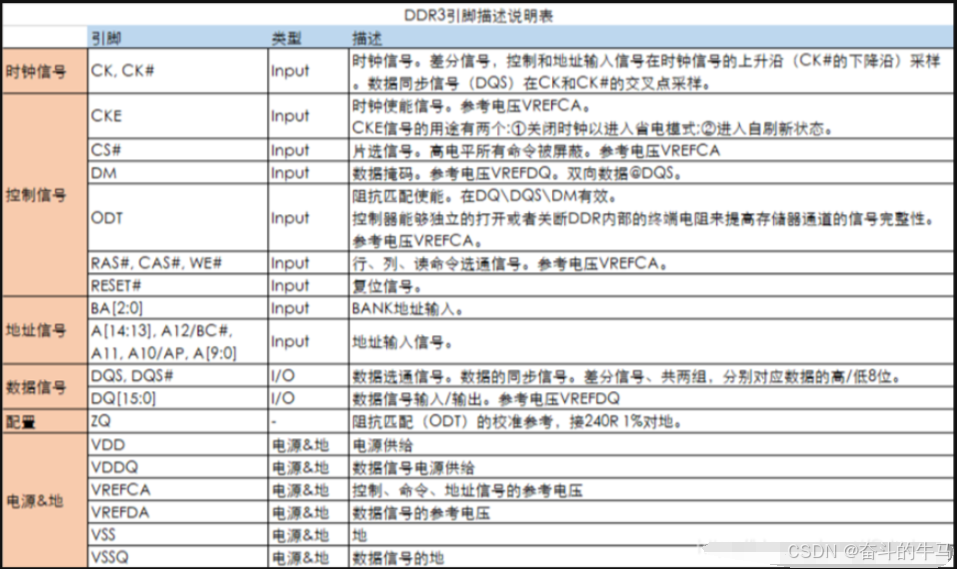

对ddr进行读写实验,用了vivado的ddr的模型进行仿真

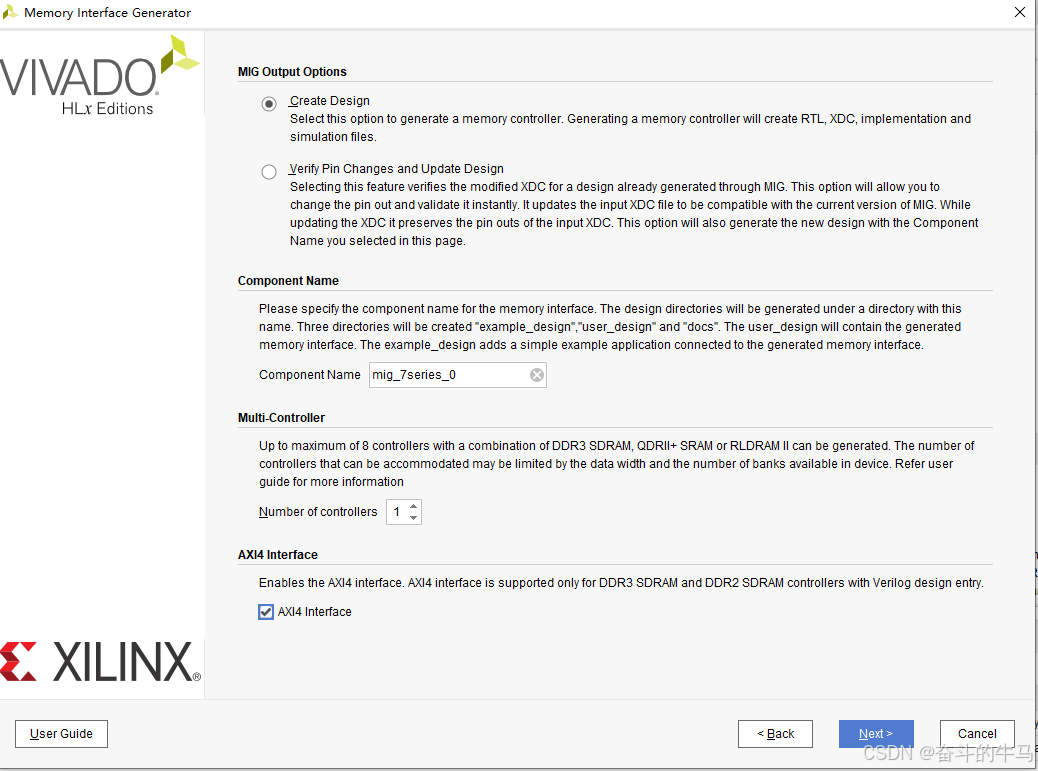

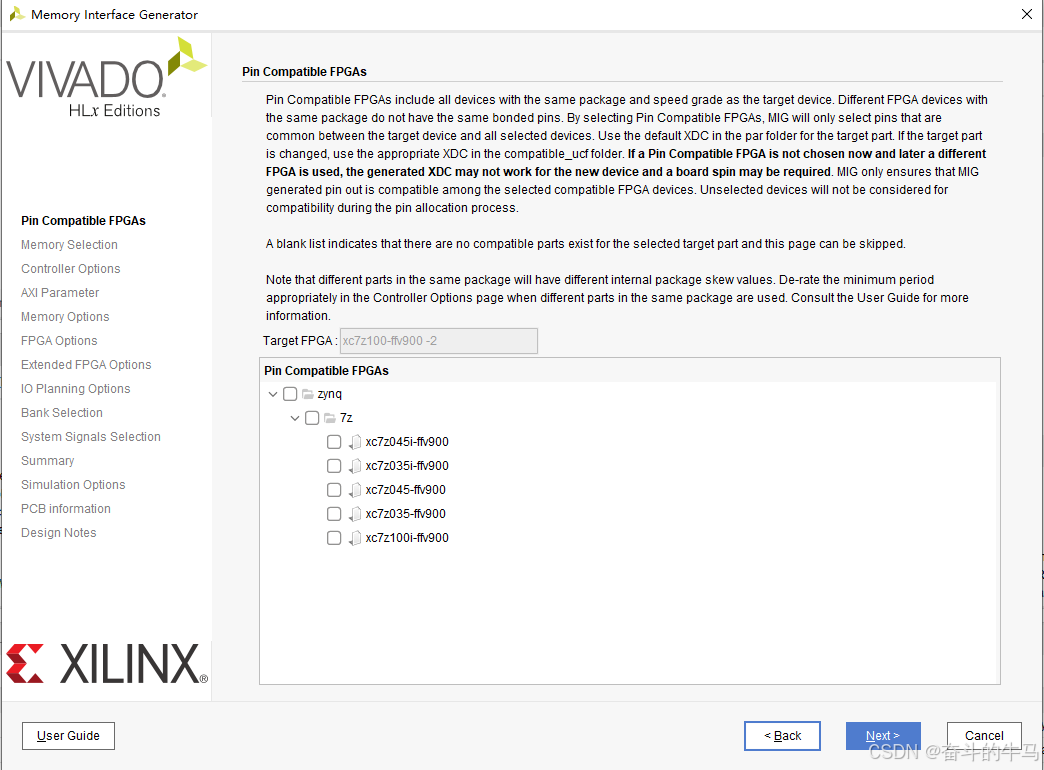

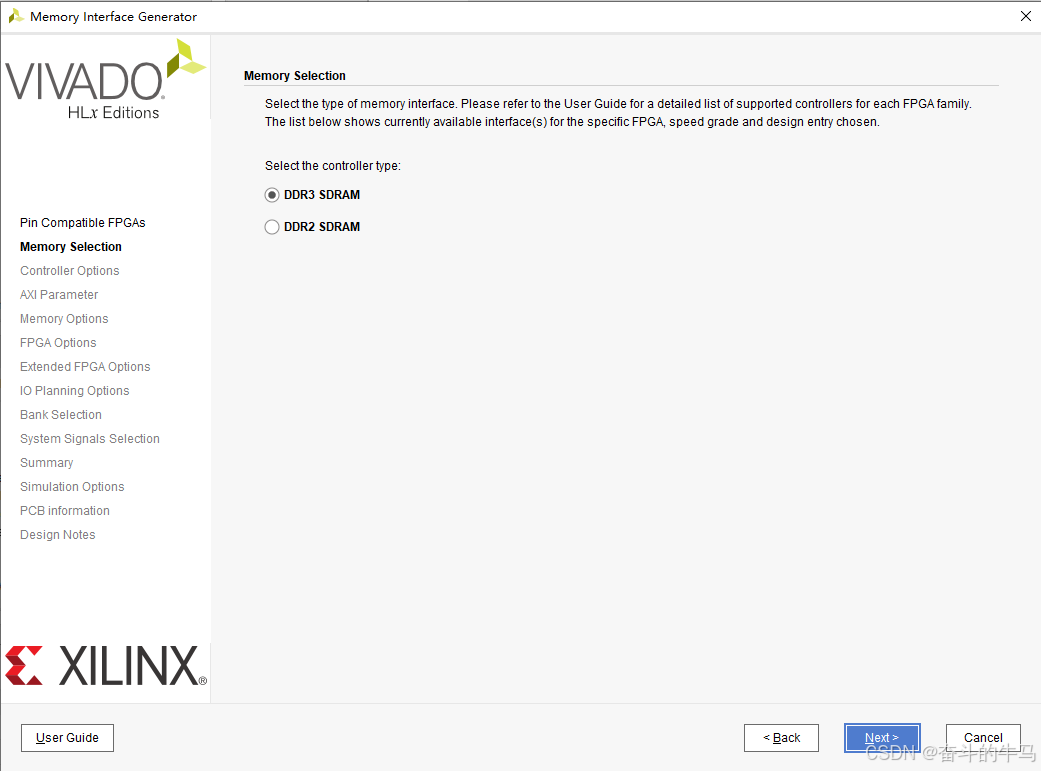

1 创建AXI_mig的ip核

选择axi

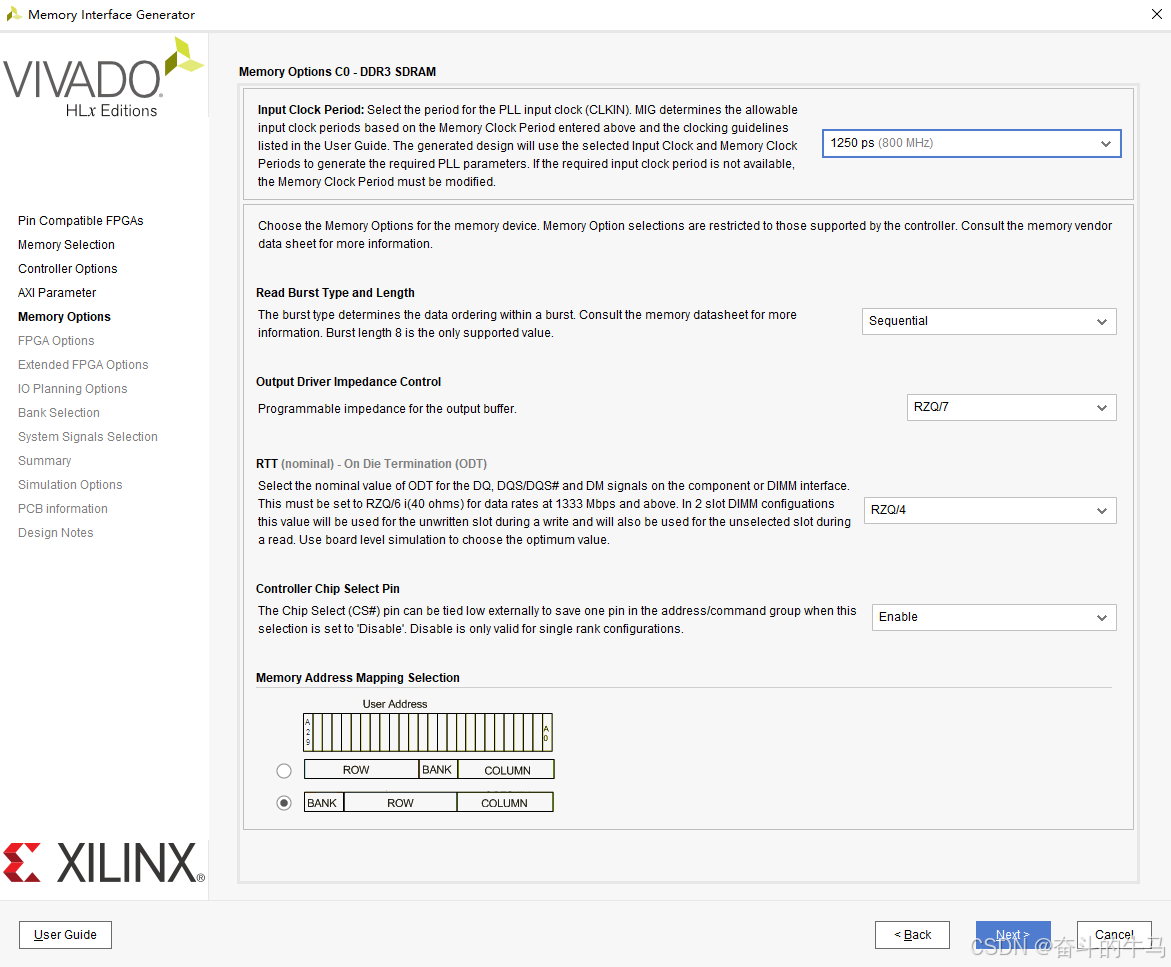

选择自己的型号,这里是ddr的位宽32,但是axi的话是256位宽

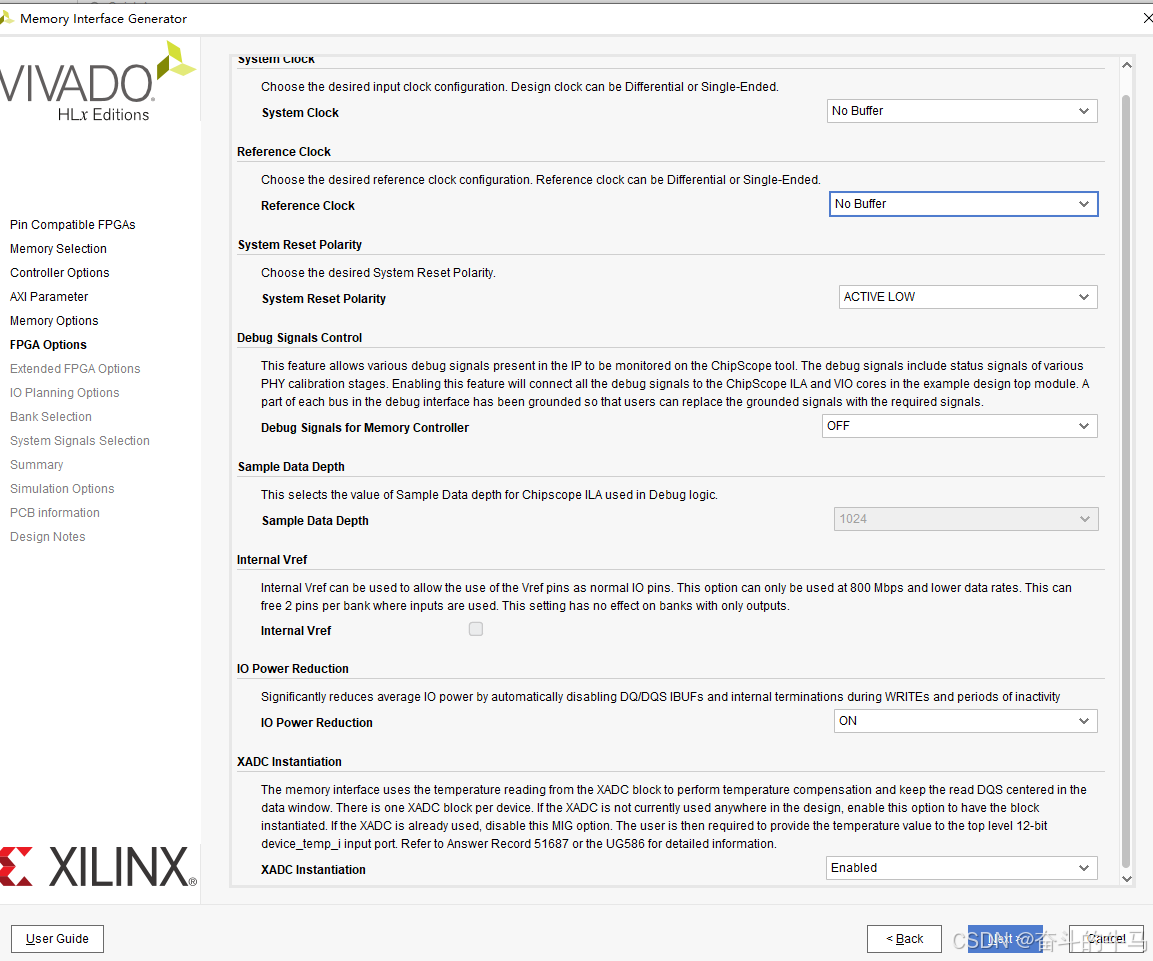

选择nobuffer,没有缓冲器

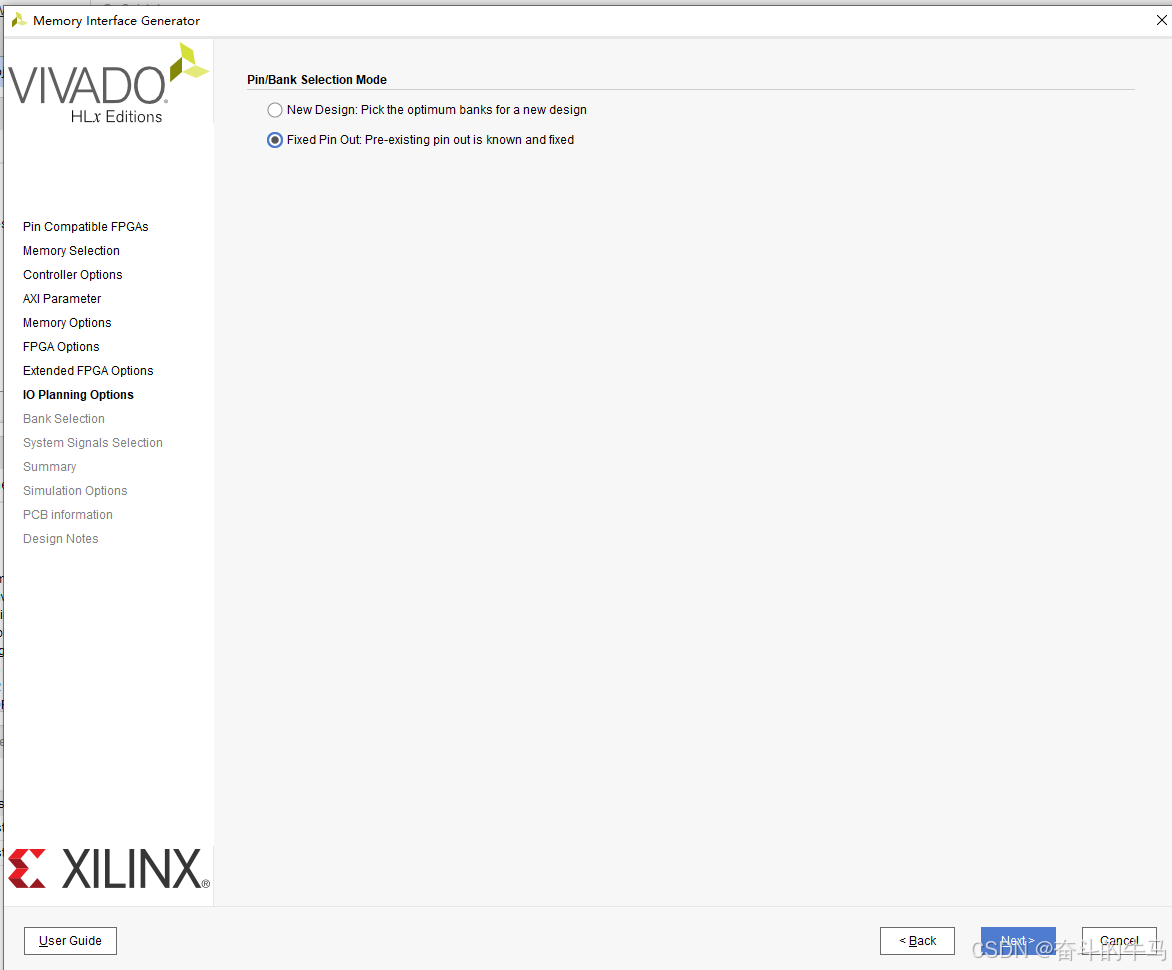

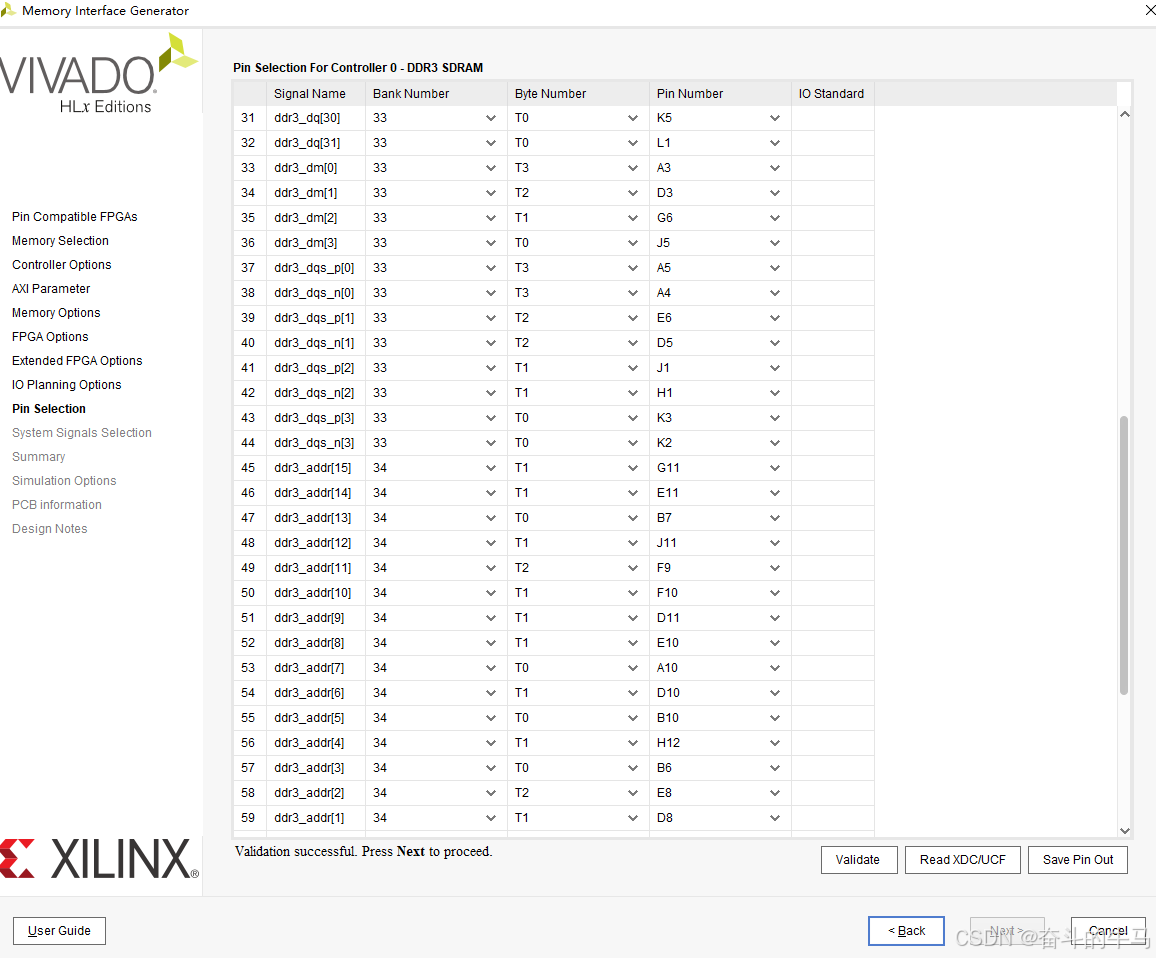

选择自己匹配引脚

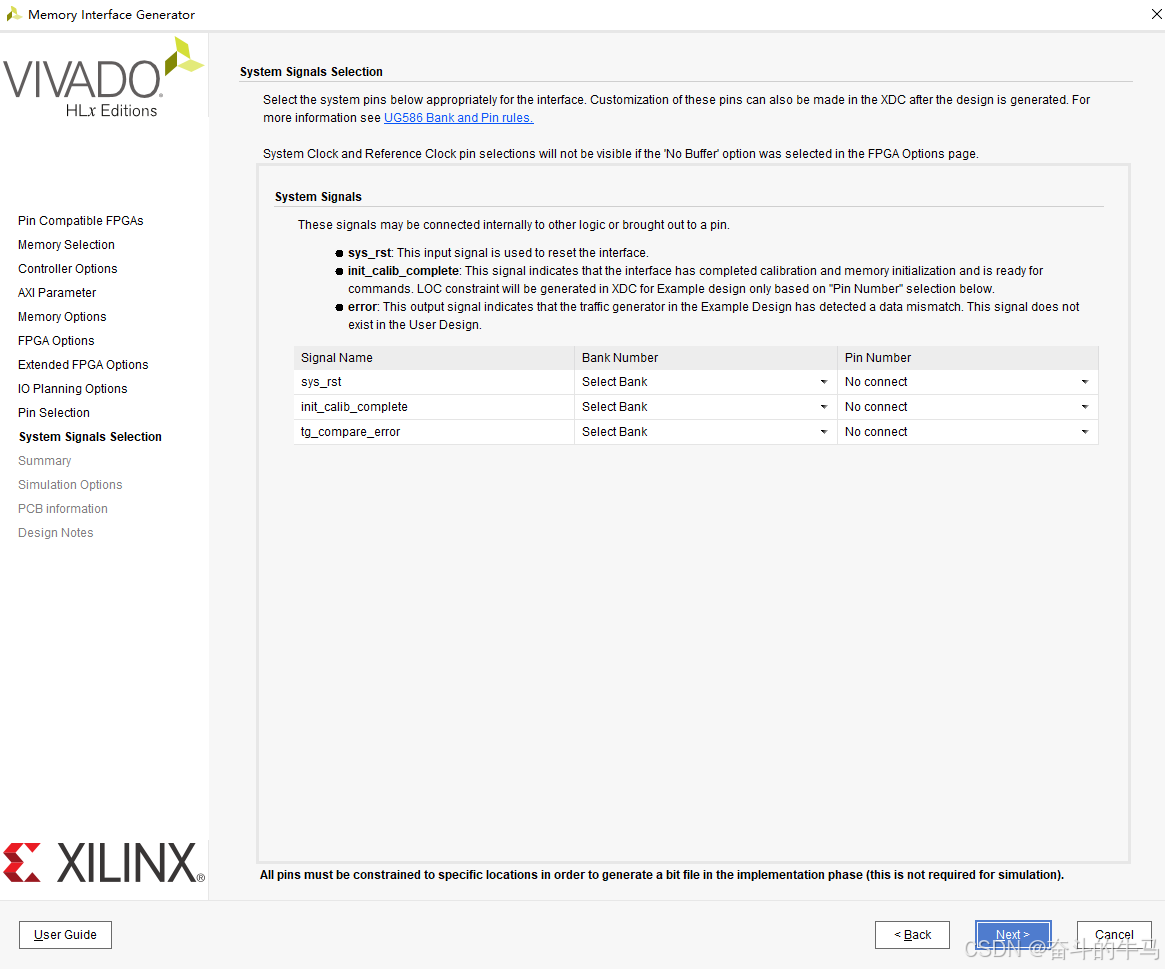

默认

后面默认即可

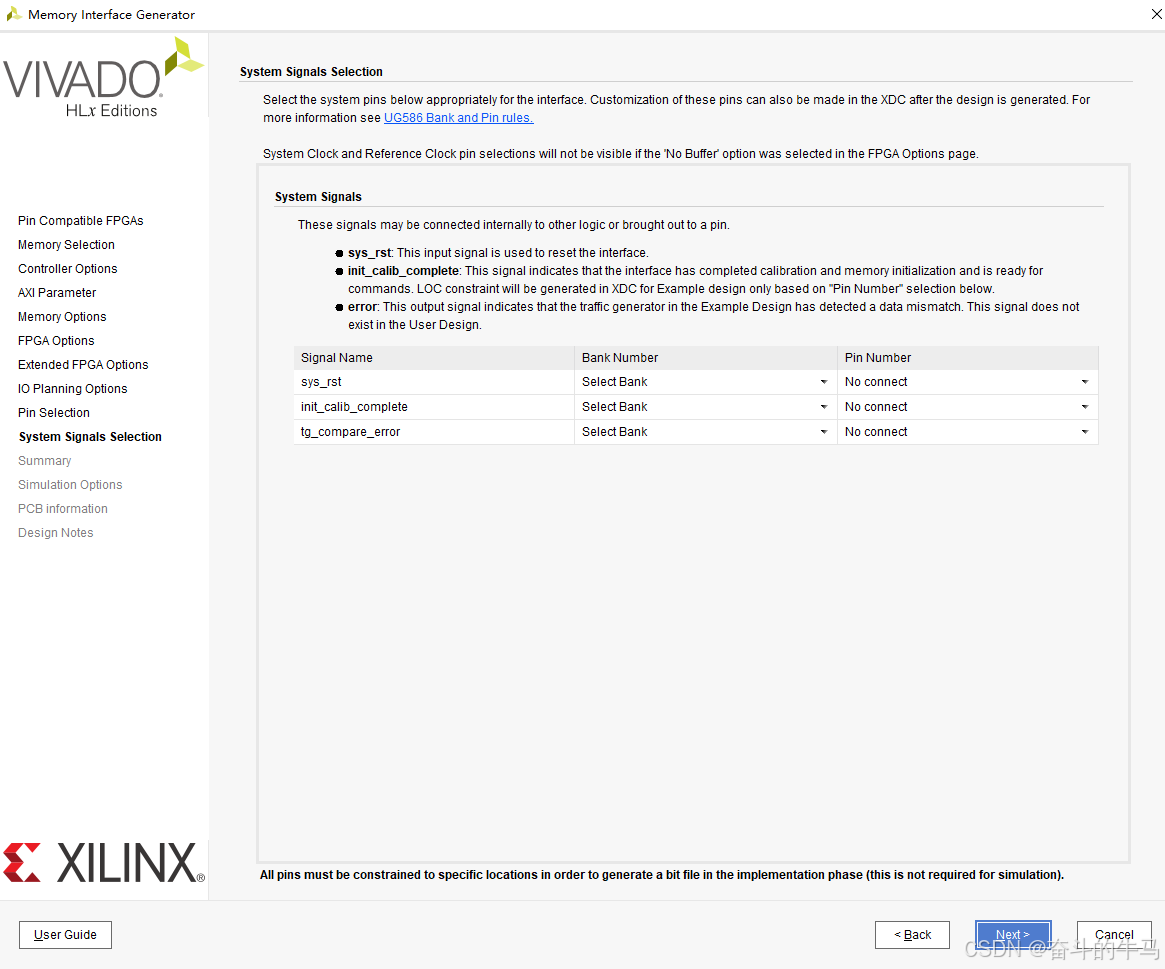

生成ip,时间很长。

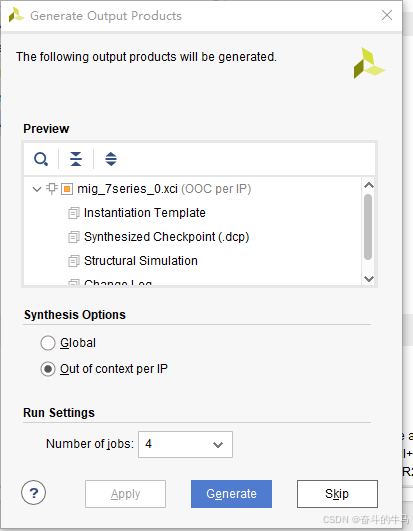

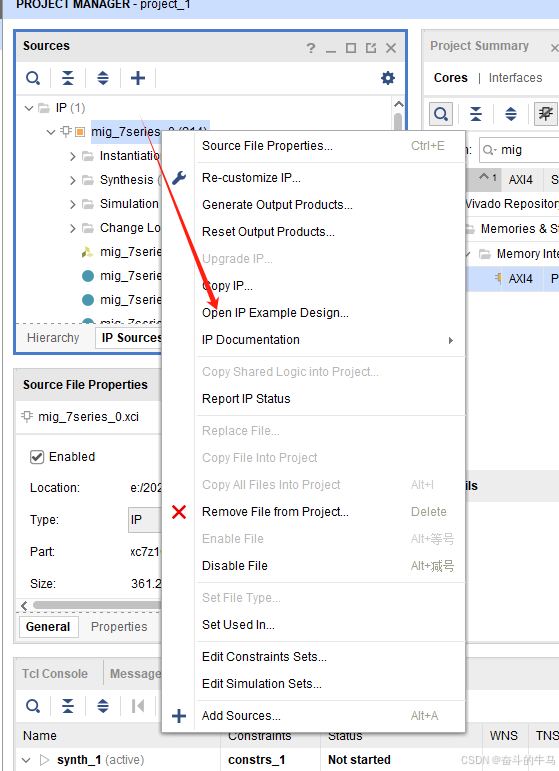

2 打开mig的工程寻找模型文件

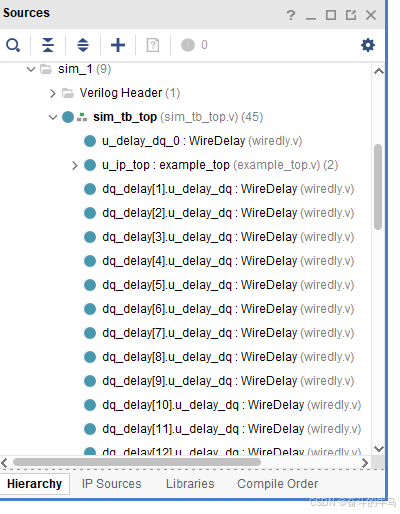

仿真模型 这个tb是xlinx自己的仿真代码以及模型

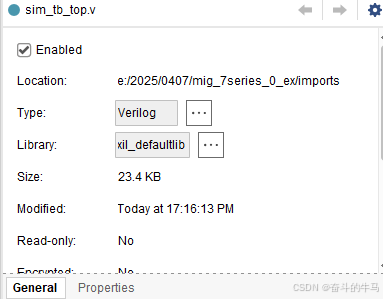

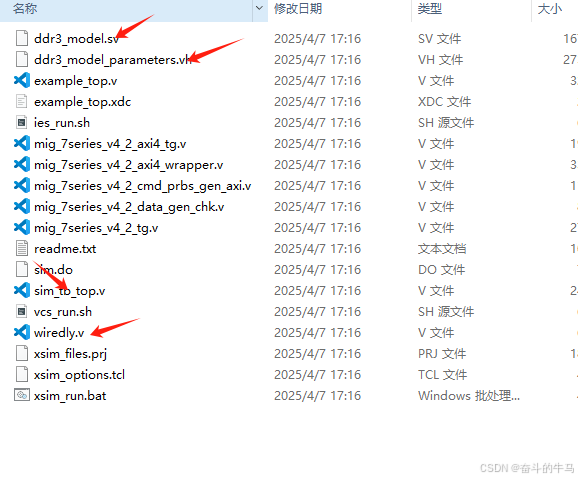

根据路径找到需要的代码

需要的文件如下都拷到自己的工程

3.写驱动模块代码

顶层模块

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2025/04/01 20:38:55 // Design Name: // Module Name: axi_ddr // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //module axi_ddr_top(input clk , input rst , input wen , input [31:0] wr_len , input rd_en , input [31:0] rd_len, output [15:0] ddr3_addr, output [2:0] ddr3_ba, output ddr3_cas_n, output [0:0] ddr3_ck_n, output [0:0] ddr3_ck_p, output [0:0] ddr3_cke, output ddr3_ras_n, output ddr3_reset_n, output ddr3_we_n, inout [31:0] ddr3_dq, inout [3:0] ddr3_dqs_n, inout [3:0] ddr3_dqs_p, input init_calib_complete, output [0:0] ddr3_cs_n, output [3:0] ddr3_dm, output [0:0] ddr3_odt);localparam integer C_S_AXI_ID_WIDTH = 4;localparam integer C_S_AXI_DATA_WIDTH = 256;localparam integer C_S_AXI_ADDR_WIDTH = 31;localparam integer C_S_AXI_AWUSER_WIDTH = 0;localparam integer C_S_AXI_ARUSER_WIDTH = 0;localparam integer C_S_AXI_WUSER_WIDTH = 0;localparam integer C_S_AXI_RUSER_WIDTH = 0;localparam integer C_S_AXI_BUSER_WIDTH = 0;wire S_AXI_ACLK;wire S_AXI_ARESETN;wire [C_S_AXI_ID_WIDTH-1 : 0] S_AXI_AWID;wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_AWADDR;wire [7 : 0] S_AXI_AWLEN;wire [2 : 0] S_AXI_AWSIZE;wire [1 : 0] S_AXI_AWBURST;wire S_AXI_AWLOCK;wire [3 : 0] S_AXI_AWCACHE;wire [2 : 0] S_AXI_AWPROT;wire [3 : 0] S_AXI_AWQOS;wire [3 : 0] S_AXI_AWREGION;wire [C_S_AXI_AWUSER_WIDTH-1 : 0] S_AXI_AWUSER;wire S_AXI_AWVALID;wire S_AXI_AWREADY;wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_WDATA;wire [(C_S_AXI_DATA_WIDTH/8)-1 : 0] S_AXI_WSTRB;wire S_AXI_WLAST;wire [C_S_AXI_WUSER_WIDTH-1 : 0] S_AXI_WUSER;wire S_AXI_WVALID;wire S_AXI_WREADY;wire [C_S_AXI_ID_WIDTH-1 : 0] S_AXI_BID;wire [1 : 0] S_AXI_BRESP;wire [C_S_AXI_BUSER_WIDTH-1 : 0] S_AXI_BUSER;wire S_AXI_BVALID;wire S_AXI_BREADY;wire [C_S_AXI_ID_WIDTH-1 : 0] S_AXI_ARID;wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_ARADDR;wire [7 : 0] S_AXI_ARLEN;wire [2 : 0] S_AXI_ARSIZE;wire [1 : 0] S_AXI_ARBURST;wire S_AXI_ARLOCK;wire [3 : 0] S_AXI_ARCACHE;wire [2 : 0] S_AXI_ARPROT;wire [3 : 0] S_AXI_ARQOS;wire [3 : 0] S_AXI_ARREGION;wire [C_S_AXI_ARUSER_WIDTH-1 : 0] S_AXI_ARUSER;wire S_AXI_ARVALID;wire S_AXI_ARREADY;wire [C_S_AXI_ID_WIDTH-1 : 0] S_AXI_RID;wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_RDATA;wire [1 : 0] S_AXI_RRESP;wire S_AXI_RLAST;wire [C_S_AXI_RUSER_WIDTH-1 : 0] S_AXI_RUSER;wire S_AXI_RVALID;wire S_AXI_RREADY;axi_addr_m axi_addr_m_inst (.clk ( ui_clk ),.rst ( rst ),.wen ( wen ),.wr_len ( wr_len ),.rd_en ( rd_en ),.rd_len ( rd_len ),.init_calib_complete (init_calib_complete) ,.s_axi_awid ( S_AXI_AWID ),.s_axi_awaddr ( S_AXI_AWADDR ),.s_axi_awlen ( S_AXI_AWLEN ),.s_axi_awsize ( S_AXI_AWSIZE ),.s_axi_awburst ( S_AXI_AWBURST ),.s_axi_awlock ( S_AXI_AWLOCK ),.s_axi_awcache ( S_AXI_AWCACHE ),.s_axi_awprot ( S_AXI_AWPROT ),.s_axi_awqos ( S_AXI_AWQOS ),.s_axi_awvalid ( S_AXI_AWVALID ),.s_axi_awready ( S_AXI_AWREADY ),.s_axi_wdata ( S_AXI_WDATA ),.s_axi_wstrb ( S_AXI_WSTRB ),.s_axi_wlast ( S_AXI_WLAST ),.s_axi_wvalid ( S_AXI_WVALID ),.s_axi_wready ( S_AXI_WREADY ),.s_axi_bid ( S_AXI_BID ),.s_axi_bresp ( S_AXI_BRESP ),.s_axi_bvalid ( S_AXI_BVALID ),.s_axi_bready ( S_AXI_BREADY ),.s_axi_arid ( S_AXI_ARID ),.s_axi_araddr ( S_AXI_ARADDR ),.s_axi_arlen ( S_AXI_ARLEN ),.s_axi_arsize ( S_AXI_ARSIZE ),.s_axi_arburst ( S_AXI_ARBURST ),.s_axi_arlock ( S_AXI_ARLOCK ),.s_axi_arcache ( S_AXI_ARCACH ),.s_axi_arprot ( S_AXI_ARPROT ),.s_axi_arqos ( S_AXI_ARQOS ),.s_axi_arvalid ( S_AXI_ARVALID ),.s_axi_arready ( S_AXI_ARREADY ),.s_axi_rid ( S_AXI_RID ),.s_axi_rdata ( S_AXI_RDATA ),.s_axi_rresp ( S_AXI_RRESP ),.s_axi_rlast ( S_AXI_RLAST ),.s_axi_rvalid ( S_AXI_RVALID ),.s_axi_rready ( S_AXI_RREADY )); // //axi_full_test_v1_0_S00_AXI # ( // .C_S_AXI_ID_WIDTH(C_S_AXI_ID_WIDTH), // .C_S_AXI_DATA_WIDTH(C_S_AXI_DATA_WIDTH), // .C_S_AXI_ADDR_WIDTH(C_S_AXI_ADDR_WIDTH), // .C_S_AXI_AWUSER_WIDTH(C_S_AXI_AWUSER_WIDTH), // .C_S_AXI_ARUSER_WIDTH(C_S_AXI_ARUSER_WIDTH), // .C_S_AXI_WUSER_WIDTH(C_S_AXI_WUSER_WIDTH), // .C_S_AXI_RUSER_WIDTH(C_S_AXI_RUSER_WIDTH), // .C_S_AXI_BUSER_WIDTH(C_S_AXI_BUSER_WIDTH) //) //axi_full_test_v1_0_S00_AXI_inst ( // .S_AXI_ACLK ( clk ), // .S_AXI_ARESETN ( rst ), // .S_AXI_AWID (S_AXI_AWID ), // .S_AXI_AWADDR (S_AXI_AWADDR ), // .S_AXI_AWLEN (S_AXI_AWLEN ), // .S_AXI_AWSIZE (S_AXI_AWSIZE ), // .S_AXI_AWBURST (S_AXI_AWBURST ), // .S_AXI_AWLOCK (S_AXI_AWLOCK ), // .S_AXI_AWCACHE (S_AXI_AWCACHE ), // .S_AXI_AWPROT (S_AXI_AWPROT ), // .S_AXI_AWQOS (S_AXI_AWQOS ), // .S_AXI_AWREGION (S_AXI_AWREGION ), // .S_AXI_AWUSER (S_AXI_AWUSER ), // .S_AXI_AWVALID (S_AXI_AWVALID ), // .S_AXI_AWREADY (S_AXI_AWREADY ), // .S_AXI_WDATA (S_AXI_WDATA ), // .S_AXI_WSTRB (S_AXI_WSTRB ), // .S_AXI_WLAST (S_AXI_WLAST ), // .S_AXI_WUSER (S_AXI_WUSER ), // .S_AXI_WVALID (S_AXI_WVALID ), // .S_AXI_WREADY (S_AXI_WREADY ), // .S_AXI_BID (S_AXI_BID ), // .S_AXI_BRESP (S_AXI_BRESP ), // .S_AXI_BUSER (S_AXI_BUSER ), // .S_AXI_BVALID (S_AXI_BVALID ), // .S_AXI_BREADY (S_AXI_BREADY ), // .S_AXI_ARID (S_AXI_ARID ), // .S_AXI_ARADDR (S_AXI_ARADDR ), // .S_AXI_ARLEN (S_AXI_ARLEN ), // .S_AXI_ARSIZE (S_AXI_ARSIZE ), // .S_AXI_ARBURST (S_AXI_ARBURST ), // .S_AXI_ARLOCK (S_AXI_ARLOCK ), // .S_AXI_ARCACHE (S_AXI_ARCACH ), // .S_AXI_ARPROT (S_AXI_ARPROT ), // .S_AXI_ARQOS (S_AXI_ARQOS ), // .S_AXI_ARREGION (S_AXI_ARREGION ), // .S_AXI_ARUSER (S_AXI_ARUSER ), // .S_AXI_ARVALID (S_AXI_ARVALID ), // .S_AXI_ARREADY (S_AXI_ARREADY ), // .S_AXI_RID (S_AXI_RID ), // .S_AXI_RDATA (S_AXI_RDATA ), // .S_AXI_RRESP (S_AXI_RRESP ), // .S_AXI_RLAST (S_AXI_RLAST ), // .S_AXI_RUSER (S_AXI_RUSER ), // .S_AXI_RVALID (S_AXI_RVALID ), // .S_AXI_RREADY (S_AXI_RREADY ) //);mig_7series_0 u_mig_7series_0 ( // Memory interface ports .ddr3_addr ( ddr3_addr ), // output [15:0] ddr3_addr .ddr3_ba ( ddr3_ba ), // output [2:0] ddr3_ba .ddr3_cas_n ( ddr3_cas_n ), // output ddr3_cas_n .ddr3_ck_n ( ddr3_ck_n ), // output [0:0] ddr3_ck_n .ddr3_ck_p ( ddr3_ck_p ), // output [0:0] ddr3_ck_p .ddr3_cke ( ddr3_cke ), // output [0:0] ddr3_cke .ddr3_ras_n ( ddr3_ras_n ), // output ddr3_ras_n .ddr3_reset_n ( ddr3_reset_n ), // output ddr3_reset_n .ddr3_we_n ( ddr3_we_n ), // output ddr3_we_n .ddr3_dq ( ddr3_dq ), // inout [31:0] ddr3_dq .ddr3_dqs_n ( ddr3_dqs_n ), // inout [3:0] ddr3_dqs_n .ddr3_dqs_p ( ddr3_dqs_p ), // inout [3:0] ddr3_dqs_p .init_calib_complete ( init_calib_complete ), // output init_calib_complete .ddr3_cs_n ( ddr3_cs_n ), // output [0:0] ddr3_cs_n .ddr3_dm ( ddr3_dm ), // output [3:0] ddr3_dm .ddr3_odt ( ddr3_odt ), // output [0:0] ddr3_odt // Application interface ports .ui_clk ( ui_clk ), // output ui_clk .ui_clk_sync_rst ( ui_clk_sync_rst ), // output ui_clk_sync_rst .mmcm_locked ( mmcm_locked ), // output mmcm_locked .aresetn ( ~ui_clk_sync_rst ), // input aresetn .app_sr_req ( 1'b0 ), // input app_sr_req .app_ref_req ( 1'b0 ), // input app_ref_req .app_zq_req ( 1'b0 ), // input app_zq_req .app_sr_active ( app_sr_active ), // output app_sr_active .app_ref_ack ( app_ref_ack ), // output app_ref_ack .app_zq_ack ( app_zq_ack ), // output app_zq_ack // Slave Interface Write Address Ports .s_axi_awid ( S_AXI_AWID ), // input [3:0] s_axi_awid .s_axi_awaddr ( S_AXI_AWADDR ), // input [31:0] s_axi_awaddr .s_axi_awlen ( S_AXI_AWLEN ), // input [7:0] s_axi_awlen .s_axi_awsize ( S_AXI_AWSIZE ), // input [2:0] s_axi_awsize .s_axi_awburst ( S_AXI_AWBURST ), // input [1:0] s_axi_awburst .s_axi_awlock ( S_AXI_AWLOCK ), // input [0:0] s_axi_awlock .s_axi_awcache ( S_AXI_AWCACHE ), // input [3:0] s_axi_awcache .s_axi_awprot ( S_AXI_AWPROT ), // input [2:0] s_axi_awprot .s_axi_awqos ( S_AXI_AWQOS ), // input [3:0] s_axi_awqos .s_axi_awvalid ( S_AXI_AWVALID ), // input s_axi_awvalid .s_axi_awready ( S_AXI_AWREADY ), // output s_axi_awready // Slave Interface Write Data Ports .s_axi_wdata ( S_AXI_WDATA ), // input [255:0] s_axi_wdata .s_axi_wstrb ( S_AXI_WSTRB ), // input [31:0] s_axi_wstrb 都有效 .s_axi_wlast ( S_AXI_WLAST ), // input s_axi_wlast .s_axi_wvalid ( S_AXI_WVALID ), // input s_axi_wvalid .s_axi_wready ( S_AXI_WREADY ), // output s_axi_wready // Slave Interface Write Response Ports .s_axi_bid ( S_AXI_BID ), // output [3:0] s_axi_bid .s_axi_bresp ( S_AXI_BRESP ), // output [1:0] s_axi_bresp .s_axi_bvalid ( S_AXI_BVALID ), // output s_axi_bvalid .s_axi_bready ( S_AXI_BREADY ), // input s_axi_bready // Slave Interface Read Address Ports .s_axi_arid ( S_AXI_ARID ), // input [3:0] s_axi_arid .s_axi_araddr ( S_AXI_ARADDR ), // input [31:0] s_axi_araddr .s_axi_arlen ( S_AXI_ARLEN ), // input [7:0] s_axi_arlen .s_axi_arsize ( S_AXI_ARSIZE ), // input [2:0] s_axi_arsize .s_axi_arburst ( S_AXI_ARBURST ), // input [1:0] s_axi_arburst .s_axi_arlock ( S_AXI_ARLOCK ), // input [0:0] s_axi_arlock .s_axi_arcache ( S_AXI_ARCACH ), // input [3:0] s_axi_arcache .s_axi_arprot ( S_AXI_ARPROT ), // input [2:0] s_axi_arprot .s_axi_arqos ( S_AXI_ARQOS ), // input [3:0] s_axi_arqos .s_axi_arvalid ( S_AXI_ARVALID ), // input s_axi_arvalid .s_axi_arready ( S_AXI_ARREADY ), // output s_axi_arready // Slave Interface Read Data Ports .s_axi_rid ( S_AXI_RID ), // output [3:0] s_axi_rid .s_axi_rdata ( S_AXI_RDATA ), // output [255:0] s_axi_rdata .s_axi_rresp ( S_AXI_RRESP ), // output [1:0] s_axi_rresp .s_axi_rlast ( S_AXI_RLAST ), // output s_axi_rlast .s_axi_rvalid ( S_AXI_RVALID ), // output s_axi_rvalid .s_axi_rready ( S_AXI_RREADY ), // input s_axi_rready // System Clock Ports .sys_clk_i ( clk ), // Reference Clock Ports .clk_ref_i ( clk ), .sys_rst ( rst ) // input sys_rst axi低电平复位 );endmodule

axi_addr_m模块代码

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2025/04/01 20:49:57 // Design Name: // Module Name: axi_addr_m // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //module axi_addr_m( input clk, input rst, input wen, input [31:0] wr_len, input rd_en, input [31:0] rd_len, input init_calib_complete,// Slave Interface Write Address Ports output [3:0] s_axi_awid , output [30:0] s_axi_awaddr , output [7:0] s_axi_awlen , output [2:0] s_axi_awsize , output [1:0] s_axi_awburst , output s_axi_awlock , output [3:0] s_axi_awcache , output [2:0] s_axi_awprot , output [3:0] s_axi_awqos , output s_axi_awvalid , input s_axi_awready , // Slave Interface Write Data Ports output [255:0] s_axi_wdata , output [31:0] s_axi_wstrb , output s_axi_wlast , output s_axi_wvalid , input s_axi_wready , // Slave Interface Write Response Ports input [3:0] s_axi_bid , input [1:0] s_axi_bresp , input s_axi_bvalid , output s_axi_bready , // Slave Interface Read Address Ports output [3:0] s_axi_arid , output [30:0] s_axi_araddr , output [7:0] s_axi_arlen , output [2:0] s_axi_arsize , output [1:0] s_axi_arburst , output [0:0] s_axi_arlock , output [3:0] s_axi_arcache , output [2:0] s_axi_arprot , output [3:0] s_axi_arqos , output s_axi_arvalid , input s_axi_arready , // Slave Interface Read Data Ports input [3:0] s_axi_rid , input [255:0] s_axi_rdata , input [1:0] s_axi_rresp , input s_axi_rlast , input s_axi_rvalid , output s_axi_rready );(* syn_keep = "true", mark_debug = "true" *) reg [31:0] w_cnt ; (* syn_keep = "true", mark_debug = "true" *) reg [31:0] r_cnt ; (* syn_keep = "true", mark_debug = "true" *) reg [31:0] wr_cnt_num ; (* syn_keep = "true", mark_debug = "true" *) reg [31:0] rd_cnt_num ; (* syn_keep = "true", mark_debug = "true" *) reg [255:0] s_axi_rdata_d ; (* syn_keep = "true", mark_debug = "true" *) reg s_axi_awvalid_r ; (* syn_keep = "true", mark_debug = "true" *) reg [30:0] s_axi_awaddr_r ;(* syn_keep = "true", mark_debug = "true" *) reg s_axi_wvalid_r ; (* syn_keep = "true", mark_debug = "true" *) reg s_axi_wlast_r ; (* syn_keep = "true", mark_debug = "true" *) reg [255:0] s_axi_wdata_r ; (* syn_keep = "true", mark_debug = "true" *) reg s_axi_arvalid_r ; (* syn_keep = "true", mark_debug = "true" *) reg [30:0] s_axi_araddr_r ; (* syn_keep = "true", mark_debug = "true" *) reg s_axi_rready_r ; (* syn_keep = "true", mark_debug = "true" *) reg wen_d1; (* syn_keep = "true", mark_debug = "true" *) reg wen_d2; (* syn_keep = "true", mark_debug = "true" *) reg rd_en_d1; (* syn_keep = "true", mark_debug = "true" *) reg rd_en_d2; (* syn_keep = "true", mark_debug = "true" *) (* syn_keep = "true", mark_debug = "true" *) reg [7:0] s_axi_awlen_d1 ; (* syn_keep = "true", mark_debug = "true" *) reg [7:0] s_axi_arlen_d1 ; (* syn_keep = "true", mark_debug = "true" *) reg init_calib_complete_d1; (* syn_keep = "true", mark_debug = "true" *) reg init_calib_complete_d2; (* syn_keep = "true", mark_debug = "true" *) wire wr_en_flag; (* syn_keep = "true", mark_debug = "true" *) wire rd_en_flag;reg [7:0] test_cnt;assign s_axi_awid =4'd0 ; assign s_axi_awlen =8'd255 ; assign s_axi_awsize =3'd5 ; assign s_axi_awburst =2'b01 ; assign s_axi_awlock =1'b0 ; assign s_axi_awcache =4'b0010 ; assign s_axi_awprot =3'd0 ; assign s_axi_awqos =4'd0 ; assign s_axi_wstrb =32'hffffffff ; assign s_axi_arid = 4'd0 ; assign s_axi_arlen = 8'd255 ; assign s_axi_arsize = 3'd5 ; assign s_axi_arburst = 2'b01 ; assign s_axi_arlock = 1'b0 ; assign s_axi_arcache = 4'b0010 ; assign s_axi_arprot = 3'd0 ; assign s_axi_arqos = 4'd0 ; assign s_axi_bready = 1'b1 ;assign s_axi_awvalid = s_axi_awvalid_r ; assign s_axi_awaddr = s_axi_awaddr_r ; assign s_axi_wvalid = s_axi_wvalid_r ; assign s_axi_wlast = s_axi_wlast_r ; assign s_axi_wdata = s_axi_wdata_r ; assign s_axi_arvalid = s_axi_arvalid_r ; assign s_axi_araddr =s_axi_araddr_r ; assign s_axi_rready = s_axi_rready_r ; assign wr_en_flag = wen_d1 & (~wen_d2) ; assign rd_en_flag = rd_en_d1 & (~rd_en_d2) ;always @(posedge clk or negedge rst) beginif (rst == 1'b0) begininit_calib_complete_d1 <= 1'b0;init_calib_complete_d2 <= 1'b0;endelse begininit_calib_complete_d1<= init_calib_complete;init_calib_complete_d2<= init_calib_complete_d1;end end//always @(posedge clk or negedge rst) begin // if (rst == 1'b0) begin // wen_d1 <= 1'b0; // wen_d2 <= 1'b0; // end // else begin // wen_d1<= wen; // wen_d2<= wen_d1; // end //end // // //always @(posedge clk or negedge rst) begin // if (rst == 1'b0) begin // rd_en_d1 <= 1'b0; // rd_en_d2 <= 1'b0; // end // else begin // rd_en_d1<= rd_en; // rd_en_d2<= rd_en_d1; // end //end //==============test==================always @(posedge clk or negedge rst) beginif (rst == 1'b0)test_cnt <=8'd0;else if( init_calib_complete_d2 == 1'b1 ) test_cnt <= test_cnt + 8'd1;else if (test_cnt == 8'd100)test_cnt <=8'd0;else; end//===========写地址========== always @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_awvalid_r <= 1'b0;else if(s_axi_awvalid && s_axi_awready ) s_axi_awvalid_r <= 1'b0;else if (s_axi_wlast_r == 1'b1 && wr_cnt_num != wr_len -1'b1 )s_axi_awvalid_r <= 1'b1;else if (test_cnt == 8'd100 && init_calib_complete_d2 == 1'b1 ) //wen_d2 == 1'b1s_axi_awvalid_r <= 1'b1;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_awaddr_r <=31'd0;else if(s_axi_awvalid_r && s_axi_awready ) s_axi_awaddr_r <= s_axi_awaddr_r + 31'd256;else; end //==========写数据=========== always @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_wvalid_r <= 1'b0;else if(s_axi_awvalid_r && s_axi_awready ) s_axi_wvalid_r <= 1'b1;else if (s_axi_wlast == 1'b1)s_axi_wvalid_r <= 1'b0;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)w_cnt <= 32'd0;else if (s_axi_wlast_r == 1'b1)w_cnt <= 32'd0;else if(s_axi_wvalid_r == 1'b1 && s_axi_wready == 1'b1 ) w_cnt <= w_cnt + 1'b1;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)wr_cnt_num <= 32'd0;else if (wr_cnt_num == wr_len -1'b1 )wr_cnt_num <= 32'd0;else if(s_axi_wvalid_r == 1'b1 && s_axi_wready == 1'b1 ) wr_cnt_num <= wr_cnt_num + 1'b1;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_wlast_r <= 1'b0;else if(w_cnt == 8'd254 ) s_axi_wlast_r <= 1'b1;else s_axi_wlast_r <= 1'b0; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_wdata_r <= 256'd0;else if(s_axi_wvalid_r == 1'b1 && s_axi_wready == 1'b1 ) s_axi_wdata_r <= s_axi_wdata_r + 1'b1;else; end//==========响应=============//==========读地址===========always @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_arvalid_r <= 1'b0;else if( s_axi_wlast_r == 1'b1 && init_calib_complete_d2 == 1'b1 ) //rd_en == 1'b1 s_axi_arvalid_r <= 1'b1;else if (s_axi_arvalid_r == 1'b1 && s_axi_arready == 1'b1 ) s_axi_arvalid_r <= 1'b0; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_araddr_r <= 31'd0;else if(s_axi_arvalid_r == 1'b1 && s_axi_arready == 1'b1 ) s_axi_araddr_r <=s_axi_araddr_r + 31'd256;else; end//==========读数据=============always @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_rready_r <= 1'b0;else if(s_axi_arvalid_r == 1'b1 && s_axi_arready == 1'b1 ) s_axi_rready_r <= 1'b1;else if (s_axi_rlast == 1'b1)s_axi_rready_r <= 1'b0;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)s_axi_rdata_d <= 256'd0;else if (s_axi_rlast == 1'b1)s_axi_rdata_d <= 256'd0;else if(s_axi_rvalid == 1'b1 && s_axi_rready == 1'b1 ) s_axi_rdata_d <=s_axi_rdata;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)r_cnt <= 32'd0;else if (s_axi_rlast == 1'b1)r_cnt <= 32'd0;else if(s_axi_rvalid == 1'b1 && s_axi_rready == 1'b1 ) r_cnt <= r_cnt + 1'b1;else; endalways @(posedge clk or negedge rst) beginif (rst == 1'b0)rd_cnt_num <= 32'd0;else if (rd_cnt_num == rd_len -1'b1 )rd_cnt_num <= 32'd0;else if(s_axi_rvalid == 1'b1 && s_axi_rready == 1'b1 ) rd_cnt_num <= rd_cnt_num + 1'b1;else; end endmodule

4.仿真

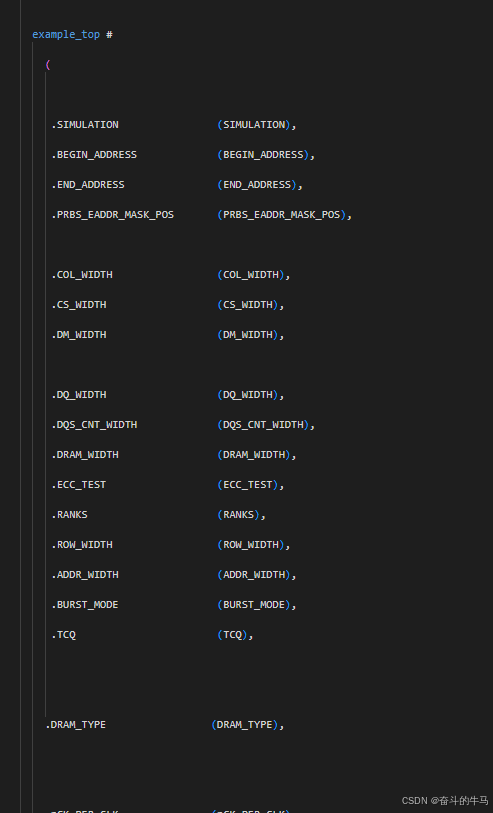

需要把xilinx的tb文件中的顶层改成自己的顶层

改成自己的

5仿真结果

尤其是注意ddr的init_calib_complete 信号拉高,表示ddr初始化完成,但是对于模型的初始地址并不是0 ,这个仿真是需要10分钟左右才能看到他拉高。

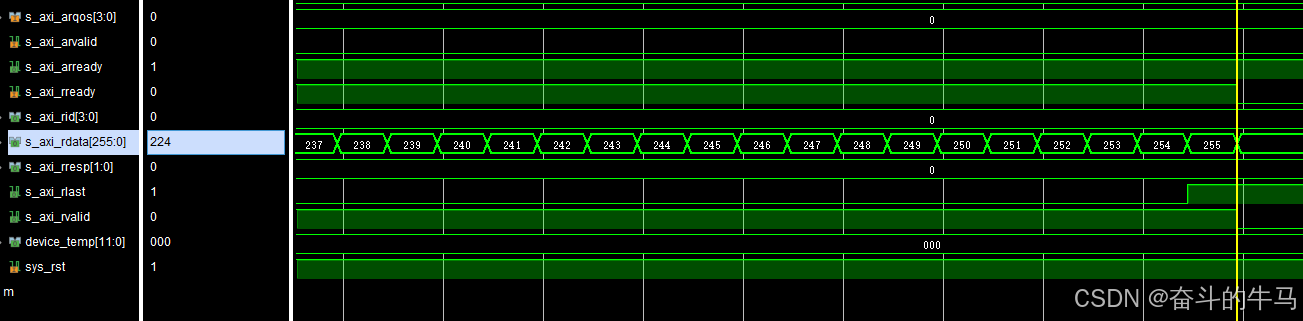

写入0-255 读0-255

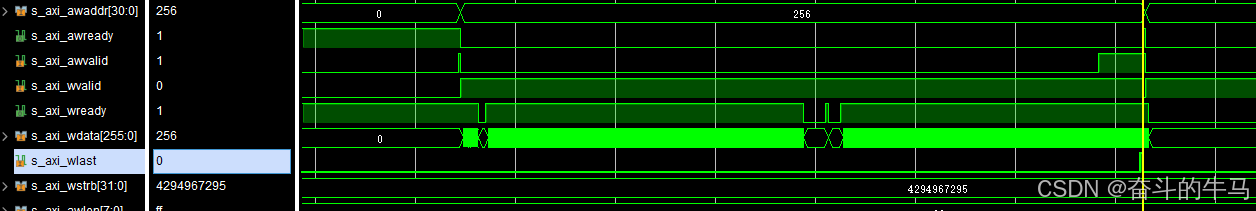

写

读

相关文章:

仿真)

FPGA_DDR(一) 仿真

对ddr进行读写实验,用了vivado的ddr的模型进行仿真 1 创建AXI_mig的ip核 选择axi 选择自己的型号,这里是ddr的位宽32,但是axi的话是256位宽 选择nobuffer,没有缓冲器 选择自己匹配引脚 默认 后面默认即可 生成ip,时间…...

【Spec2MP:项目管理之项目人力管理】

芯片设计项目中如何打造战斗力强悍的团队? 引言:芯片设计项目的核心是人 芯片设计是一项高度复杂、跨学科协作的工程,团队的专业性、协作效率和凝聚力直接影响项目成败。本文结合某芯片项目人力管理文档,从目标、职责、价值观、架…...

windows10下PointNet官方代码Pytorch实现

PointNet模型运行 1.下载源码并安装环境 GitCode - 全球开发者的开源社区,开源代码托管平台GitCode是面向全球开发者的开源社区,包括原创博客,开源代码托管,代码协作,项目管理等。与开发者社区互动,提升您的研发效率和质量。https://gitcode.com/gh_mirrors/po/pointnet.pyto…...

阿里云大模型训练与推理开发

本文主要描述阿里云大模型开发环境的搭建、训练数据集的制作流程、大模型如何训练数据集以及如何利用已训练完成的模型执行推理。 开发环境搭建 ModelScope社区是阿里云通义千问开源的大模型开发者社区。 如上所示,安装ModelScope社区大模型基础库开发框架的命令行…...

图灵逆向——题一-动态数据采集

目录列表 过程分析代码实现 过程分析 第一题比较简单,直接抓包即可,没有任何反爬(好像头都不用加。。。) 代码实现 答案代码如下: """ -*- coding: utf-8 -*- File : .py author : 鲨鱼爱兜兜 T…...

GS069W电动工具直流调速电路深度解析

产品概述 GS069W是我们推出的CMOS专用调速集成电路,采用SOP8封装,内置15V稳压结构,具有宽电压输入(4-24V)、低功耗、强抗干扰等特点,专为电动工具调速设计。 核心参数 工作电压:4-24Vÿ…...

PyQt6实例_A股日数据维护工具_下载某个股票未复权数据

目录 前置: 相关代码: 1 工作类 2 数据库交互 3 主界面调用 视频 前置: 1 本系列将以 “PyQt6实例_A股日数据维护工具” 开头放置在“PyQt6实例”专栏 2 日数据可在“数据库”专栏,“PostgreSQL_”开头系列博文中获取 3 权…...

【蓝桥杯】算法笔记6

1. 可行性剪枝应用 1.1. 题目 题目描述: 给定一个正整数n和一个正整数目标值target,以及一个由不同正整数组成的数组nums。要求从nums中选出若干个数,每个数可以被选多次,使得这些数的和恰好等于target。问有多少种不同的组合方式? 输入: 第一行:n和target,表示数组…...

C++ 中日期类的输入输出操作符重载实践

目录 引言 预备知识 输出流操作符 operator<< 重载 为什么要返回 ostream& 输入流操作符 operator>> 重载 实现思路 测试代码 总结 引言 在 C 编程中,当我们自定义数据类型时,为了让其能像内置类型一样方便地进行输入输出操…...

图论:最小生成树

最小生成树 (无向无环图) 概念 1.Prim算法 P3366 【模板】最小生成树 - 洛谷 邻接矩阵实现 #include<iostream> #include<cstring> using namespace std; const int INF 0x3f3f3f3f; const int N 5e3 10; int dis[N]; //记录每个结点到…...

)

linux中CosyVoice声音克隆安装教程——TTS文本转语音(数字人组件)

CosyVoice 作为一款先进的语音合成解决方案,其设计理念在于提供高效、稳定且灵活的语音生成工具。本教程将从环境配置、依赖安装、模型下载到服务部署全流程进行详细介绍,旨在为用户提供前瞻性的技术指导,同时兼顾细节解析和专业名词解释&…...

智能手表该存什么音频和文本?场景化存储指南

文章目录 为什么需要“场景化存储”?智能手表的定位手机替代不了的场景碎片化的场景存储 音频篇:智能手表该存什么音乐和音频?运动场景通勤场景健康场景 文本篇:哪些文字信息值得放进手表?(部分情况可使用图…...

怎么检查网站CDN缓存是否生效

为什么要使用CDN缓存? 网站使用缓存可显著提升加载速度,减少服务器负载和带宽消耗,优化用户体验,增强架构稳定性,助力SEO优化,实现资源高效利用与性能平衡。 通过合理配置 CDN 缓存策略,可降低…...

win10安装gitbash工具

问题描述:在Windows下没有预装bash命令处理工具 # WInR输入cmd回车进入命令行,执行以下命令出现乱码 bash 无法使用bash命令 解决方案:下载安装gitbash命令行工具 Git Bash 是一个在 Windows 上运行的终端仿真器,集成了 Git 和 Bash shell࿰…...

买不起了,iPhone 或涨价 40% ?

周知的原因,新关税对 iPhone 的打击,可以说非常严重。 根据 Rosenblatt Securities分析师的预测,若苹果完全把成本转移给消费者。 iPhone 16 标配版的价格,可能上涨43%。 iPhone 16 标配的价格是799美元,上涨43%&am…...

企业级 ClickHouse Docker 离线部署实践指南20250407

企业级 ClickHouse Docker 离线部署实践指南 引言 在数据分析与日志处理日益重要的今天,ClickHouse 凭借其高性能、列式存储架构,成为企业在大数据分析中的首选引擎之一。本文基于一位金融行业从业者在离线网络环境中部署 ClickHouse 的真实实践过程&a…...

多域名 SSL 证书能保护多少个域名?

一、基础保护数量范围 多域名 SSL 证书,顾名思义,可保护多个不同域名。通常情况下,不同证书颁发机构(CA)设定的基础保护数量有所差异。一般的多域名 SSL 证书能保护2 至 5 个域名,这些域名可以是完全独立…...

Linux系统学习Day04 阻塞特性,文件状态及文件夹查询

知识点4【文件的阻塞特性】 文件描述符 默认为 阻塞 的 比如:我们读取文件数据的时候,如果文件缓冲区没有数据,就需要等待数据的到来,这就是阻塞 当然写入的时候,如果发现缓冲区是满的,也需要等待刷新缓…...

)

【AI】高效地使用 AI 模型的 Prompt(提示词)

明确任务和目标 在使用 Prompt 之前,要清楚知道自己想要通过 AI 模型完成什么任务,例如生成文本、回答问题、进行翻译或创作故事等。明确的目标有助于构建更有针对性的 Prompt,引导模型生成符合期望的结果。 精准描述问题 提供具体细节&am…...

第二十:mysql——Undo Log、Redo Log和Binlog

二进制日志binlog(归档日志)、 事务日志redo log(重做日志) MySQL实例挂了或者宕机了,重启的时候InnoDB存储引擎会使用rede log日志恢复数据,保证事务的持久性和完整性 和undo log(回滚日志&a…...

LogicFlow-前端流程图开发

LogicFlow-前端流程图开发 一、安装使用 1、安装logicflow 通过npm安装logicflow npm install logicflow/core --save# 插件包(不使用插件时不需要引入) npm install logicflow/extension --save2、创建实例 import LogicFlow from "logicflow/…...

)

第四讲:类与对象(下)

目录 1、再谈构造函数 1.1、构造函数体赋值 1.2、初始化列表 1.3、explicit关键字 2、static成员 3、友元 3.1、友元函数 3.2、友元类 4、内部类 5、匿名对象 6、拷贝对象时的优化(了解) 7、重新理解类与对象 8、日期类的实现 9、练习题 9…...

)

ReAct 框架 | 提示词工程(1)

ReAct 框架 1、什么是 ReAct 框架?2、基于 ReAct 框架的提示词3、结合 LangChain 框架使用4、总结 1、什么是 ReAct 框架? ReAct : Reasoning Acting ,将推理与外部工具调用结合,通过交互式探索解决复杂问题。 优点…...

第一部分——Docker篇 第一章 Docker容器

关于系统的改造探索 开篇:系统改造的调研报告 第一部分——Docker篇 第一章 Docker容器 第二章 Docker安装 第三章 构建自定义镜像 第四章 搭建镜像仓库 第五章 容器编排 第六章 容器监控 文章目录 关于系统的改造探索第一部分——Docker篇 前言一、就是你了——…...

)

ubuntu,react的学习(1)

在此目录下,开启命令行 /home/kt/react 如下操作 tkt4028:~/react$ npm create vitelatest task-manager -- --template react Need to install the following packages: create-vite6.3.1 Ok to proceed? (y) y> npx > cva task-manager --template react…...

AR 赋能儿童娱乐:剧本杀与寻宝小程序搭建秘籍

在科技飞速发展的当下,儿童娱乐领域正经历着一场创新变革。AR(增强现实)技术的融入,为儿童剧本杀与寻宝游戏带来了前所未有的沉浸式体验。通过搭建专属小程序,孩子们能够在虚拟与现实交织的世界中开启奇幻冒险。接下来…...

试题速浏、分类及浅析)

2017年-全国大学生数学建模竞赛(CUMCM)试题速浏、分类及浅析

2017年-全国大学生数学建模竞赛(CUMCM)试题速浏、分类及浅析 全国大学生数学建模竞赛(China Undergraduate Mathematical Contest in Modeling)是国家教委高教司和中国工业与应用数学学会共同主办的面向全国大学生的群众性科技活动,目的在于激励学生学习数学的积极性,提高学…...

密码学基础——分组密码的运行模式

前面的文章中文我们已经知道了分组密码是一种对称密钥密码体制,其工作原理可以概括为将明文消息分割成固定长度的分组,然后对每个分组分别进行加密处理。 下面介绍分组密码的运行模式 1.电码本模式(ECB) 2.密码分组链接模式&…...

zk源码—2.通信协议和客户端原理一

大纲 1.ZooKeeper如何进行序列化 2.深入分析Jute的底层实现原理 3.ZooKeeper的网络通信协议详解 4.客户端的核心组件和初始化过程 5.客户端核心组件HostProvider 6.客户端核心组件ClientCnxn 7.客户端工作原理之会话创建过程 1.ZooKeeper如何进行序列化 (1)什么是序列化…...

)

【NLP】Transformer网络结构(2)

一、Transformer 整体架构 Transformer 由 Encoder 和 Decoder 堆叠组成,每个 Encoder/Decoder 层包含以下核心模块: Encoder 层:Multi-Head Self-Attention → Add & LayerNorm → Feed-Forward → Add & LayerNormDecoder 层&…...

【LeetCode77】组合

题目描述 给定区间 [1, n] 和一个整数 k,需要返回所有可能的 k 个数的组合。 思路 算法选择:回溯算法 回溯算法是一种试探性搜索方法,非常适合用来解决组合问题。基本思想是: 从数字 1 开始,逐步构建组合。当当前组…...

1631. 最小体力消耗路径

文章目录 题意思路代码 题意 题目链接 思路 搜索 代码 class Solution { public:int minimumEffortPath(vector<vector<int>>& heights) {int m heights.size();int n heights[0].size();int x_add[] {0, 0, 1, -1};int y_add[] {1, -1, 0, 0};if (m …...

时间复杂度和空间复杂度

🌟 各位看官好,我是maomi_9526! 🌍 种一棵树最好是十年前,其次是现在! 🚀 今天来学习C语言的相关知识。 👍 如果觉得这篇文章有帮助,欢迎您一键三连,分享给更…...

Python基于OpenCV和SVM实现中文车牌识别系统GUI界面

说明:这是一个系统实战项目,如需项目代码可以直接到文章最后关注获取。 项目背景 随着智能交通系统和智慧城市的发展,车牌识别技术在车辆管理、交通监控、停车场收费等领域发挥着重要作用。传统的车牌识别系统主要针对英文和数字的识别&…...

用AbortController取消事件绑定

视频教程 React - 🤔 Abort Controller 到底是什么神仙玩意?看完这个视频你就明白了!💡_哔哩哔哩_bilibili AbortController的好处之一是事件绑定的函数已无需具名函数,匿名函数也可以被取消事件绑定了 //该代码2秒后点击失效…...

4月7日随笔

晚饭塔斯汀 下了晚自习买了一瓶百香果rio 还有一块五毛钱的老酸奶,这个糖吃的时候是真开心呀 英语课互动感觉越来越少了,我甚至看了十分钟的小排球 解析几何和微积分都听不进去了。就算坐在第三排还是会走神。但是不知道为什么我刷视频和打游戏的时…...

功能)

Android使用声网SDK实现音视频互动(RTC)功能

一、前期准备 1、注册声网账号 声网官网 2、创建项目 拿到AppID,主要证书 二、代码部分 先上一下官方提供的demo地址: Agora-RTC-QuickStart: 此仓库包含 Agora RTC Native SDK 的QuickStart示例项目。 - Gitee.comhttps://gitee.com/agoraio-comm…...

【go】slice的浅拷贝和深拷贝

浅拷贝(Shallow Copy) 浅拷贝是指只复制切片本身的结构(指针、长度和容量),而不复制底层数组的元素。 实现方式 直接赋值: slice1 : []int{1, 2, 3} slice2 : slice1 // 浅拷贝切片操作: slice1 : []int{1, 2, 3} s…...

哑铃图:让数据对比一目了然【Dumbbell Chart】

没错,当我祭出 “哑铃” 阵列,你当如何破解,哈哈哈哈…此时,你可以适当怀疑笔者的精神状态了。但话说回来,如果稍加想象,把上图竖起来,“大致” 就是我要分享的 “哑铃图” 了。😑 …...

Spring Boot 集成 MongoDB 时自动创建的核心 Bean 的详细说明及表格总结

以下是 Spring Boot 集成 MongoDB 时自动创建的核心 Bean 的详细说明及表格总结: 核心 Bean 列表及详细说明 1. MongoClient 类型:com.mongodb.client.MongoClient作用: MongoDB 客户端核心接口,负责与 MongoDB 服务器建立连接、…...

水产养殖水下监控无人机推荐-P200PRO

水产养殖水下监控无人机推荐 | 潜 鲛 P200 PRO:您的“水下管家”,养鱼增产、降本增效的终极利器! ——上海 棕航电子 科技,用技术守护每一方鱼塘 一、水产养殖的痛点:看不见的水下,才是赚钱的关键 …...

)

数据结构与算法-数学-基础数学算法(筛质数,最大公约数,最小公倍数,质因数算法,快速幂,乘法逆元,欧拉函数)

一:筛质数: 1-埃氏筛法 该算法核心是从 2 开始,把每个质数的倍数标记为合数,时间复杂度约为 O(nloglogn)。 #include <iostream> #include <vector>u sing namespace std; const int N 1000010; bool st[N]; …...

elasticSearch-搜索引擎

搜索引擎的优势 有了数据库分页查询,为什么还需要搜索引擎? 搜索引擎速度上很快数据库分页查询,随着数据库数据量增大,页数靠后,会导致搜索速度变慢,但是搜索引擎不会搜索引擎支持分词查询,地…...

MQTT-Dashboard-数据集成

sink [sɪŋk] 下沉;沉没;沉降;...

uni-app项目运行在浏览器、微信开发者工具、mumu模拟器

一、安装HBuilder X 1、下载HBuilder X 官网网址:https://dcloud.io/hbuilderx.html 根据电脑系统下载对应的版本(我的电脑是Windows 10) 2.安装HBuilder X 直接将HBuilderX.4.61.2025040322-alpha.zip解压到自己想要存放的文件夹中 双击…...

从零开始微调Embedding模型:基于BERT的实战教程

文章目录 背景微调实战装包介绍 项目文件介绍微调硬件配置要求 debug 重要代码分析【选看】资源分享参考资料 背景 在理解与学会了Naive RAG的框架流程后,就很自然地关注到embedding模型,与问题相关的文本召回,也有很多论文在做这方面的创新…...

——个人理解篇5(梯度下降中遇到的问题))

机器学习(神经网络基础篇)——个人理解篇5(梯度下降中遇到的问题)

在神经网络训练中,计算参数的梯度是关键步骤。numerical_gradient 方法旨在通过数值微分(中心差分法)计算损失函数对网络参数的梯度。然而,该方法的实现存在一个关键问题,导致梯度计算错误。 1、错误代码示例…...

)

带label的3D饼图(threejs)

3D饼图 使用three.js实现,选择threejs的原因:label需要实际的显示在具体的饼对应的模块上 “three”: “^0.127.0”, <template><div><div ref"chartContainer" class"chart-container"></div><div clas…...

ragflow开启https访问:使用自签证书还是有不安全警告,如何解决

背景:在ragflow里的使用了自签证书来启动ragflow,在浏览器里访问还是不安全警告,如何解决 在方案2中,证书不会在访问网站时自动下载,需要你手动获取并安装证书文件。以下是具体操作步骤: 详细步骤:手动获取并安装自签名证书 第一步:获取证书文件 找到证书文件 证书文件位…...

条件变量核心要素

条件变量内部实现原理 原子性解锁阻塞机制: // pthread_cond_wait内部伪代码大致如下: int pthread_cond_wait(cond_t *cond, mutex_t *mutex) {atomic {unlock(mutex); // 原子操作中先释放互斥锁block_thread(); // 立即将线程加入等待队列…...