时序约束高级进阶使用详解四:Set_False_Path

目录

一、背景

二、Set_False_Path

2.1 Set_false_path常用场景

2.2 Set_false_path的优势

2.3 Set_false_path设置项

2.4 细节区分

三、工程示例

3.1 工程代码

3.2 时序约束如下

3.3 时序报告

3.4 常规场景

3.4.1 设计代码

3.4.2 约束场景

3.4.3 约束对象总结

四、参考资料

一、背景

在进行时序分析时,工具默认对所有的时序路径进行分析,在实际的设计中,存在一些路径不属于逻辑功能的,或者不需要进行时序分析的路径,使用set_false_path对该路径进行约束,时序分析时工具将会直接忽略路径不进行分析。

二、Set_False_Path

2.1 Set_false_path常用场景

可以设置为false path的场景包括

a) 跨时钟域中添加的进行两次同步的逻辑单元

b) 只在FPGA通电启动时的配置寄存器

c) 复位或测试的逻辑模块

d) 异步的分布式RAM中读时钟和写时钟之间的路径

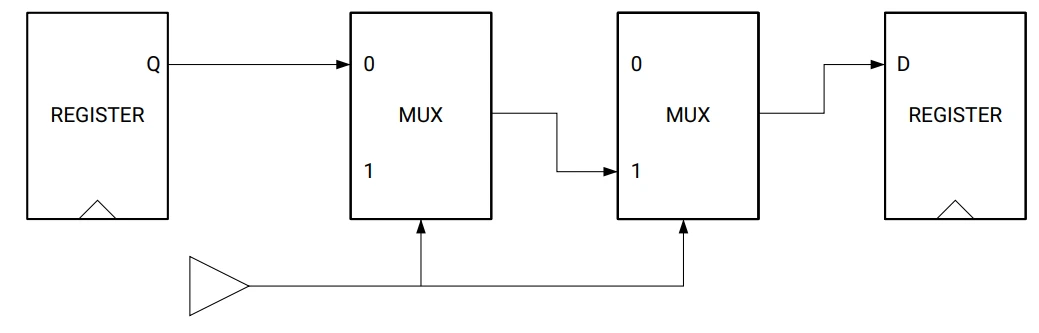

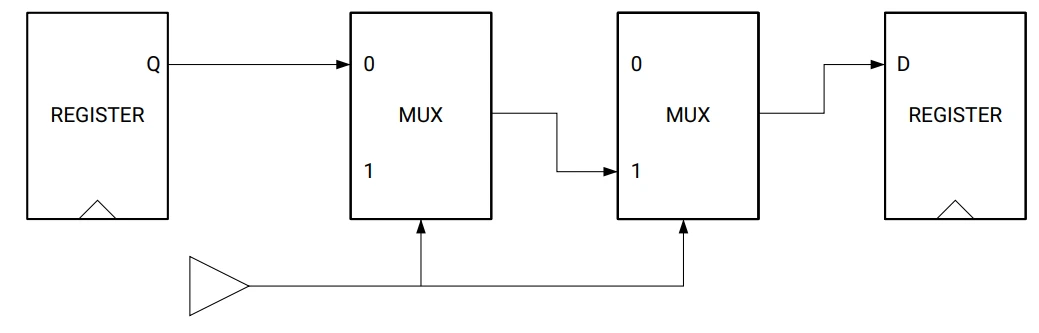

非功能路径示例如下,在两个触发器中级联了两个选择器,选择器的选项信号相同,因此,两个MUX不会同时有效,Q到D的时序路径时不存在。

2.2 Set_false_path的优势

a)减少运行时间:将一些路径设置为false path后,时序分析工具无需耗费时间对该路径进行分析,也不需要对非功能模块路径进行优化,可以节省时间

b)提高QOR(quality of results):将路径设置为false path可以极大地提高QOR,综合,布局后的质量,优化设计也会极大地受工具尝试解决的时序问题影响。

因为如果非功能模块的路径存在时序违例时,工具可能尝试去修复这些违例,这不仅可能会导致设计(如逻辑复制)而优化复杂,也可能因为非功能模块有更大的违例而忽略了实际功能模块的违例问题。只有正确的设置约束才能获取最好的结果。

2.3 Set_false_path设置项

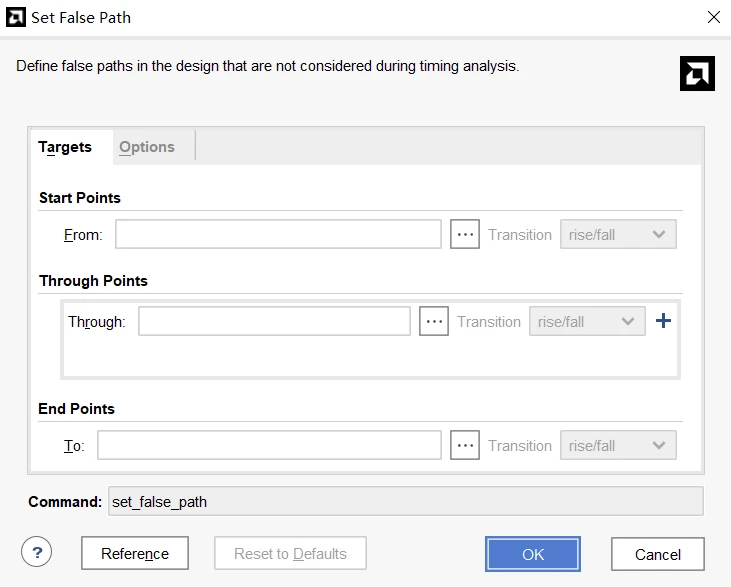

set_false_path设置包含Targets和Options两个子界面,Targets中主要是From,Through,To三个对象的设置

Start Point/From:设置false path的起点,可以为Cell pins,clocks,cells,I/O ports,也可指定应用到设置对象的上升沿或下降沿,默认为上升沿和下降沿都有效;

rise_from:约束在路径起点的上升沿有效

fall_from:约束在路径起点的下降沿有效

Through Points:设置false path经过的中间路径,可以为Nets,cells,cell pins,也可指定应用到设置对象的上升沿或下降沿,默认为上升沿和下降沿都有效;

rise_through:约束在路径经过单元的上升沿有效

fall_through:约束在路径经过单元的下降沿有效

End Points/To:设置false path的终点,可以为Cell pins,clocks,cells,I/O ports,也可指定应用到设置对象的上升沿或下降沿,默认为上升沿和下降沿都有效;

rise_to:约束在路径终点的上升沿有效

fall_to:约束在路径终点的下降沿有效

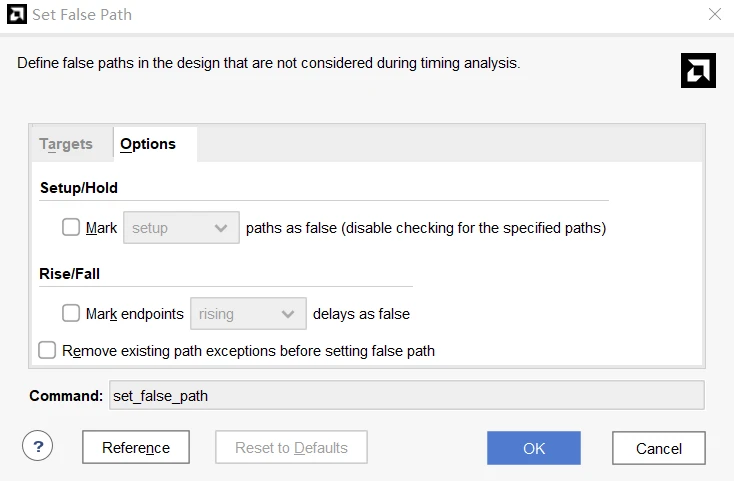

Options中可以对约束路径做一些限定

Setup:设置约束仅对路径的Setup不进行分析

Hold:设置约束仅对路径的hold不进行分析

rise:设置约束对路径的上升沿都不进行分析

fall:设置约束对路径的下降沿都不进行分析

reset_path:在设置false_path前移除路径上的其他时序例外

2.4 细节区分

a)多个-through时,顺序不同结果不同,下面两条约束不是等价的,第一条表示先通过cell1/pin1,再通过cell2/pin2的路径,第二条约束则相反

set_false_path -through cell1/pin1 -through cell2/pin2

set_false_path -through cell2/pin2 -through cell1/pin1b)get_cells连接多个单元时,表示从复位端口reset到多个cells(ff1_reg,ff2_reg,ff3_reg)中的路径都将设为false path

set_false_path -from [get_ports reset] -to [get_cells {ff1_reg ff2_reg ff3_reg}]c)不对两个异步时钟clk1,clk2间的路径进行分析,只会将从clk1到clk2间的路径设置为false path

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]d)如果要对clk1到clk2,clk2到clk1的路径都设置为false path,则需要两条约束命令

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

set_false_path -from [get_clocks clk2] -to [get_clocks clk1]e)当需要对多个异步时钟间都不进行时序分析时,对异步时钟两两间设置false path则太繁琐,此时可使用set_clock_groups代替

set_clock_groups -name clk_group -asynchronous -group [get_clocks clk1] -group [get_clocks clk2] -group [get_clocks clk3]f)在两个寄存器间的非正常逻辑功能路径中,设置false path可以只使用两个through,而不用指定start point和end point,以下图设计

命令中MUX1/a0和MUX2/a1位置不能换,交换后则表示先经过MUX2/a1再经过MUX1/a0

set_false_path -through [get_pins MUX1/a0] -through [get_pins MUX2/a1]f)对于异步双端口分布式RAM,写操作和RAM的时钟是同步的,读操作可以不同步,因此,在写时钟和读时钟间设置false path符合设计需求,rd_clk为读时钟,wr_clk为写时钟,设置从写寄存器到读寄存器的false path,实现方式如下

set_false_path -from [get_cells <write_registers>] -to [get_cells <read_registers>]三、工程示例

3.1 工程代码

以几种常见场景的示例进行说明set_false_path的使用

module false_path(clkA,clkB,data_in,data_out,clk,async_rst,async_rst_reg,

config_en,mode,config_reg,scan_en,scan_in,scan_out,scan_data_out,a,b,result);

input clkA,clkB,data_in;

output reg data_out;

reg data_reg;

reg data_meta;

input clk,async_rst;

output reg async_rst_reg;

input config_en,mode;

output reg config_reg;

input scan_en,scan_in;

output scan_out, scan_data_out;

reg scan_reg; // 扫描链寄存器

input wire [3:0] a, b;

output reg [7:0] result;

reg [7:0] temp;

reg [1:0] cycle_count;// 用于两级同步的寄存器,clkA和clkB间的时序不需要分析

always @(posedge clkA) data_reg <= data_in; // 第一级同步

// 两级同步器(防止亚稳态)

always @(posedge clkB)

begindata_meta <= data_reg; // 第一级同步data_out <= data_meta; // 第二级同步

end//异步复位信号路径,不需要分析async_rst和clk的时序

always @(posedge clk or negedge async_rst)

beginif (!async_rst) async_rst_reg <= 1'b0; // 异步复位else async_rst_reg <= data_in;

end//上电配置信,上电后config_en固定不变,因为mode为配置信号,固定不变,故不需要分析mode到config_reg的时序always @(posedge clk) beginif (config_en) config_reg <= (mode == 1'b0) ? data_in : ~data_in;else config_reg <= 1'b0;

end//测试模块中,在scan_en有效时,scan_in到scan_reg的路径不需要分析

always @(posedge clk) beginif (scan_en) scan_reg <= scan_in; // 测试模式下,数据来自 scan_inelse scan_reg <= data_in; // 正常模式下,数据来自 data_in

end

assign scan_out = scan_reg;

assign scan_data_out = scan_reg;//多周期路径,计数值cycle_count到temp的路径不需要分析

always @(posedge clk)

beginif (cycle_count == 2'b00) temp <= a * b; // 第1周期:计算乘法else if (cycle_count == 2'b01) temp <= temp + 1; // 第2周期:加1else result <= temp; // 第3周期:输出结果 cycle_count <= cycle_count + 1;

endendmodule3.2 时序约束如下

#时钟约束

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

create_clock -period 10.000 -name clkA -waveform {0.000 5.000} [get_ports clkA]

create_clock -period 10.000 -name clkB -waveform {0.000 5.000} [get_ports clkB]

#端口约束

set_input_delay -clock [get_clocks clk] 0.123 [get_ports {{a[0]} {a[1]} {a[2]} {a[3]} async_rst {b[0]} {b[1]} {b[2]} {b[3]} config_en data_in mode scan_en scan_in}]

set_output_delay -clock [get_clocks clk] 0.123 [get_ports -regexp -filter { NAME =~ ".*" && DIRECTION == "OUT" }]

#时序不分析约束

set_false_path -from [get_clocks clkA] -to [get_clocks clkB]

set_false_path -from [get_ports async_rst] -to [all_registers]

set_false_path -from [get_ports scan_in] -to [get_cells scan_reg_reg]

#set_false_path -from [get_ports {{a[0]} {a[1]} {a[2]} {a[3]}}] -to [get_cells {{result_reg[0]} {result_reg[1]} {result_reg[2]} {result_reg[3]} {result_reg[4]} {result_reg[5]} {result_reg[6]} {result_reg[7]}}]

set_false_path -from [get_ports mode]

set_false_path -from [get_cells {{cycle_count_reg[0]} {cycle_count_reg[1]}}] -to [get_cells {{temp_reg[0]} {temp_reg[1]} {temp_reg[2]} {temp_reg[3]} {temp_reg[3]_i_2} {temp_reg[4]} {temp_reg[5]} {temp_reg[6]} {temp_reg[7]} {temp_reg[7]_i_3}}]

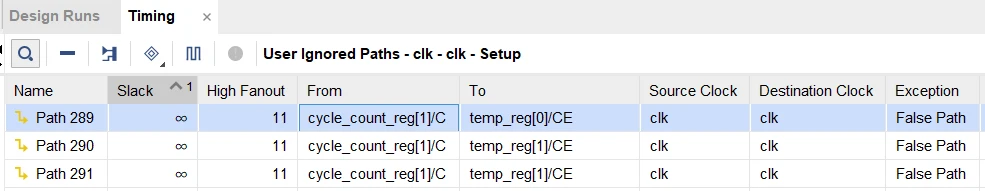

3.3 时序报告

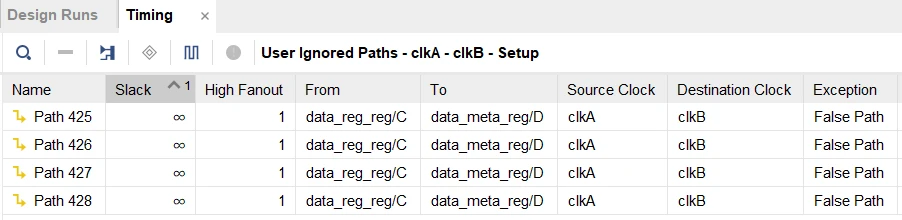

用于两级同步的寄存器,clkA和clkB间的时序不需要分析

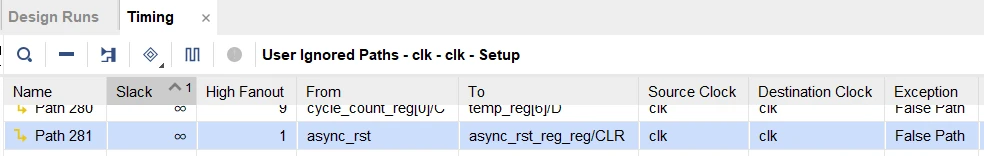

异步复位信号路径,不需要分析async_rst和clk的时序,但复位信号的释放需要分析

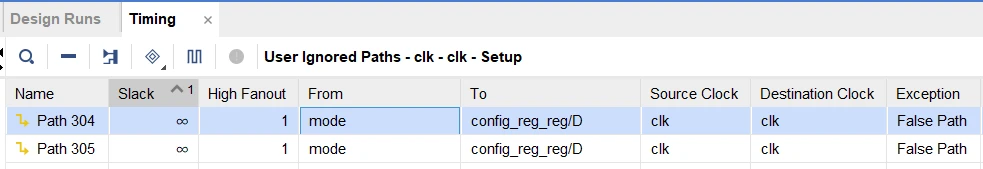

上电配置信号,上电后config_en固定不变,因为mode为配置信号,固定不变,故不需要分析mode到config_reg的时序

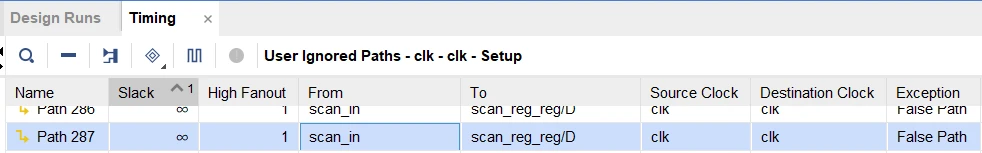

测试模块中,在scan_en有效时,scan_in到scan_reg的路径不需要分析

多周期路径,计数值cycle_count到temp的路径不需要分析

3.4 常规场景

3.4.1 设计代码

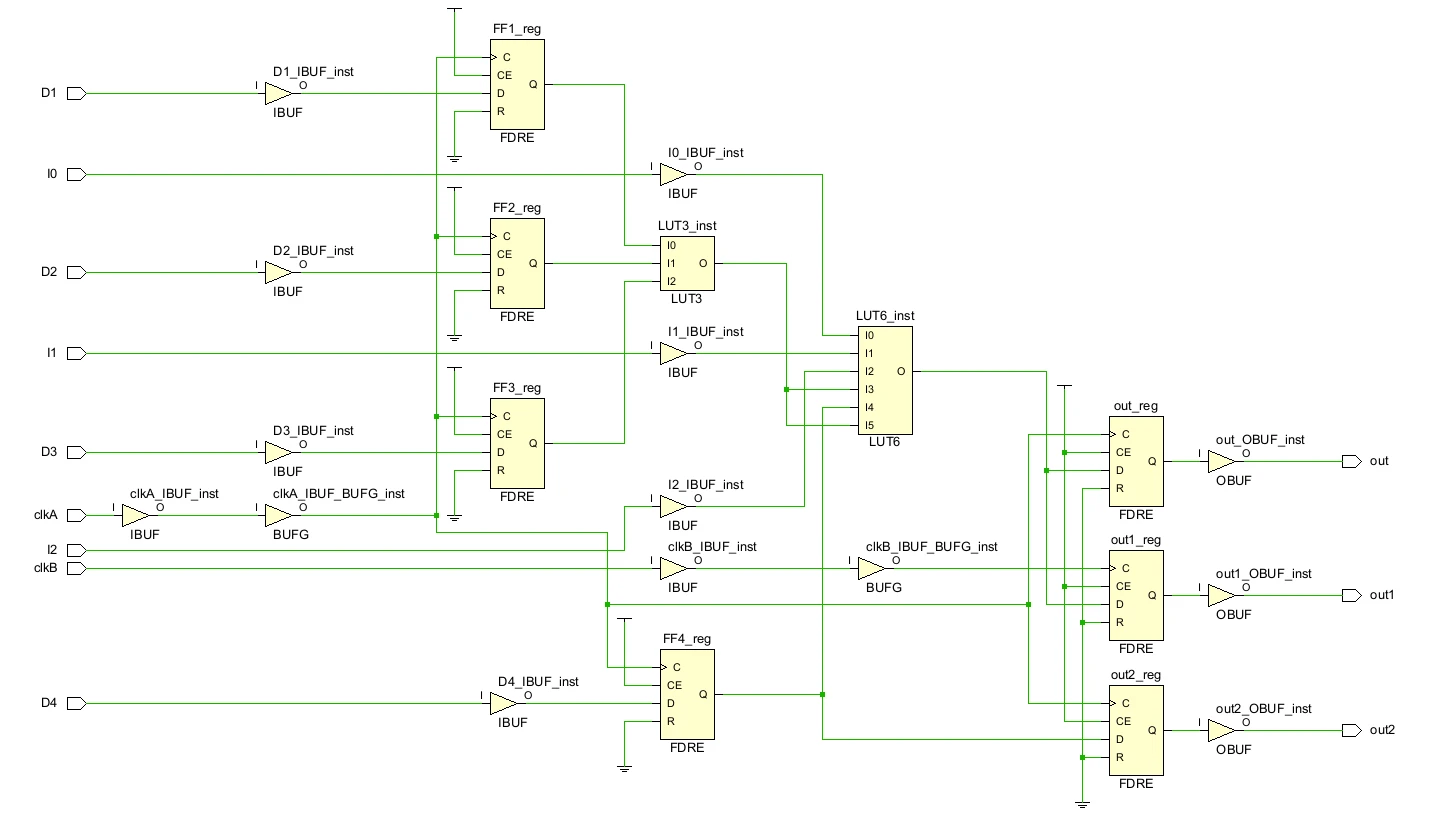

下面将针对约束对象细节进行说明,设计如下

module SetFalsePath(D1,D2,D3,D4,I0,I1,I2,clkA,clkB,out,out1,out2);

input D1,D2,D3,D4,I0,I1,I2,clkA,clkB;

output reg out,out1,out2;

reg FF1,FF2,FF3,FF4;

wire n_lut3,n_lut6;

always @(posedge clkA) FF1 <= D1;

always @(posedge clkA) FF2 <= D2;

always @(posedge clkA) FF3 <= D3;

always @(posedge clkA) FF4 <= D4; LUT3 #(.INIT(8'hF1) // Specify LUT Contents) LUT3_inst (.O(n_lut3), // LUT general output.I0(FF1), // LUT input.I1(FF2), // LUT input.I2(FF3) // LUT input);

LUT6 #(.INIT(64'h0001001010000100) // Specify LUT Contents) LUT6_inst (.O(n_lut6), // LUT general output.I0(I0), // LUT input.I1(I1), // LUT input.I2(I2), // LUT input.I3(n_lut3), // LUT input.I4(FF4), // LUT input.I5(n_lut3) // LUT input);always @(posedge clkA) out <= n_lut6;

always @(posedge clkB) out1 <= n_lut6;

always @(posedge clkA) out2 <= FF4;

endmoduleschematic如下图,三个触发器FF1,FF2,FF3输出连接到一个LUT3_inst,然后与触发器FF4共同输入到LUT_inst。

基础约束主要是主时钟以及输入输出端口的约束

create_clock -period 10.000 -name clkA -waveform {0.000 5.000} [get_ports clkA]

create_clock -period 10.000 -name clkB -waveform {0.000 5.000} [get_ports clkB]

set_input_delay -clock [get_clocks clkA] 0.123 [get_ports {D1 D2 D3 D4 I0 I1 I2}]

set_output_delay -clock [get_clocks clkB] 0.123 [get_ports -regexp -filter { NAME =~ ".*" && DIRECTION == "OUT" }]3.4.2 约束场景

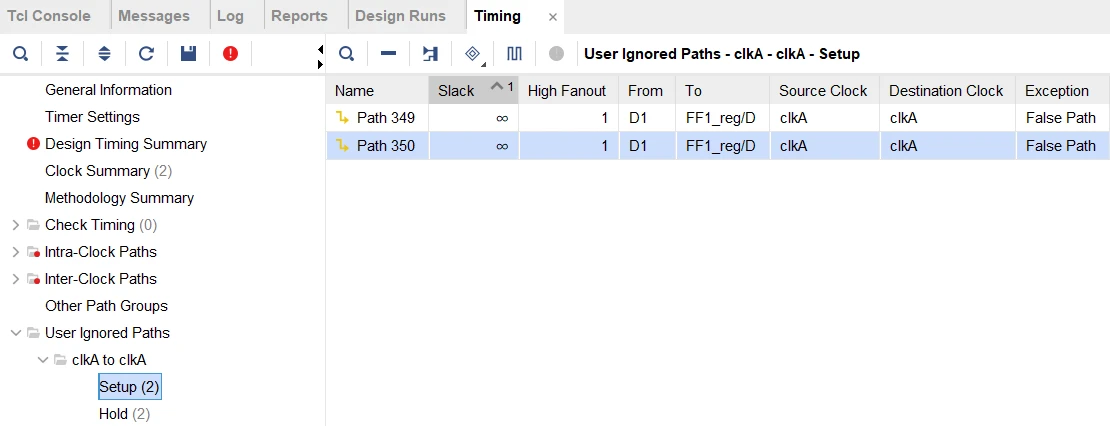

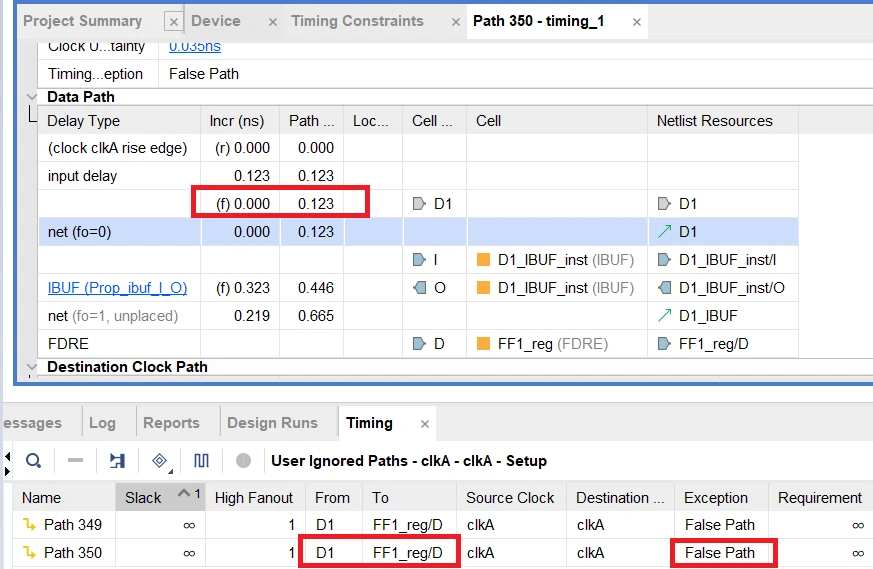

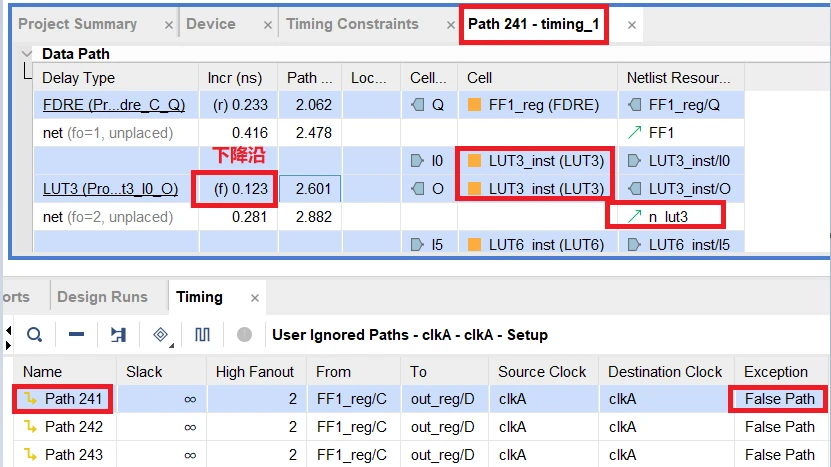

a)约束from对象类型为get_cells和get_ports下降沿false path

set_false_path -fall_from [get_cells FF1_reg]

set_false_path -fall_from [get_ports D1]因为FF1_reg的clk输入都为上升沿,所以没有对应生效的false_path

对于D1的输出net为下降沿f是约束生效

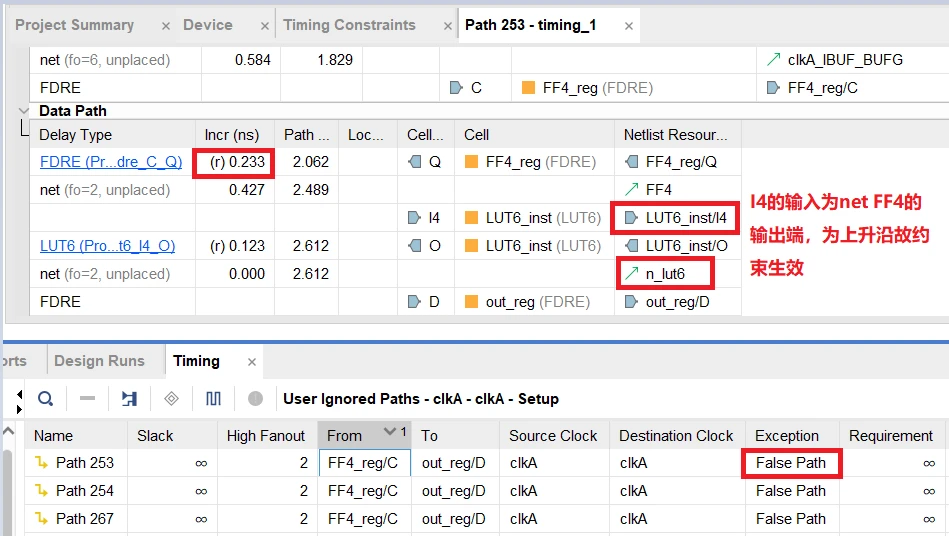

b) 约束through对象的类型Cells和Nets为false path

set_false_path -fall_through [get_cells LUT3_inst]

set_false_path -rise_through [get_pins LUT6_inst/I4]LUT3_inst的输出n_lut3为下降沿,约束生效

LUT6_inst/I4的约束效果

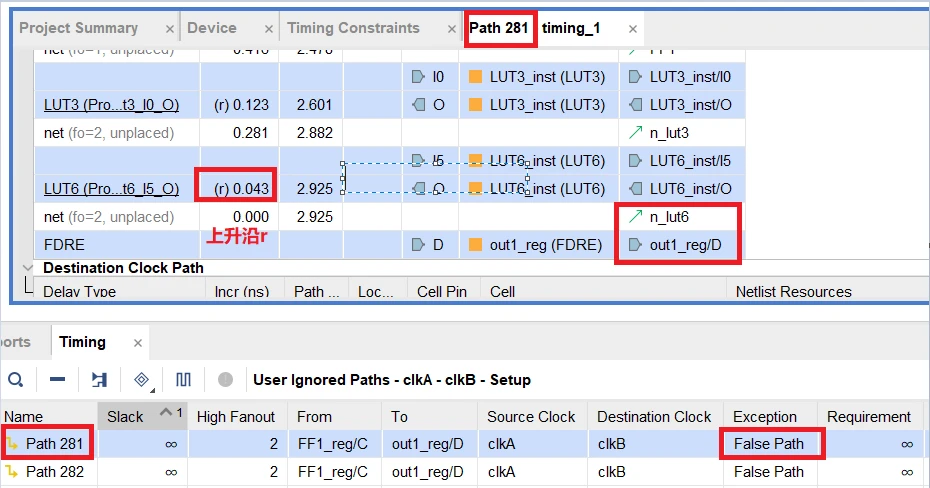

c)约束To对象的类型Cells和I/O port为false path

set_false_path -reset_path -rise_to [get_cells out1_reg]

set_false_path -fall_to [get_ports out2]rise_to为out1_reg,out1_reg的D端口输入为n_lut6,对应为上升沿,约束生效

out2端口的输入信号为下降沿f,约束生效

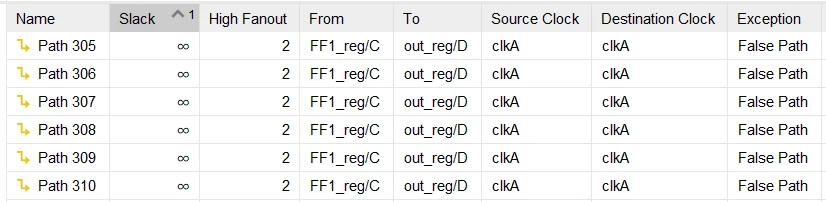

d)约束包含多个对象,部分对象不是有效的from/through/to

以from包含多个对象为例,其中只有FF1_reg为有效的start point

set_false_path -from [get_cells {FF1_reg LUT3_inst LUT6_inst}]有效的起点约束生效,无效的起点直接忽略

f)所有路径设置false path,对所有起点的时钟进行约束

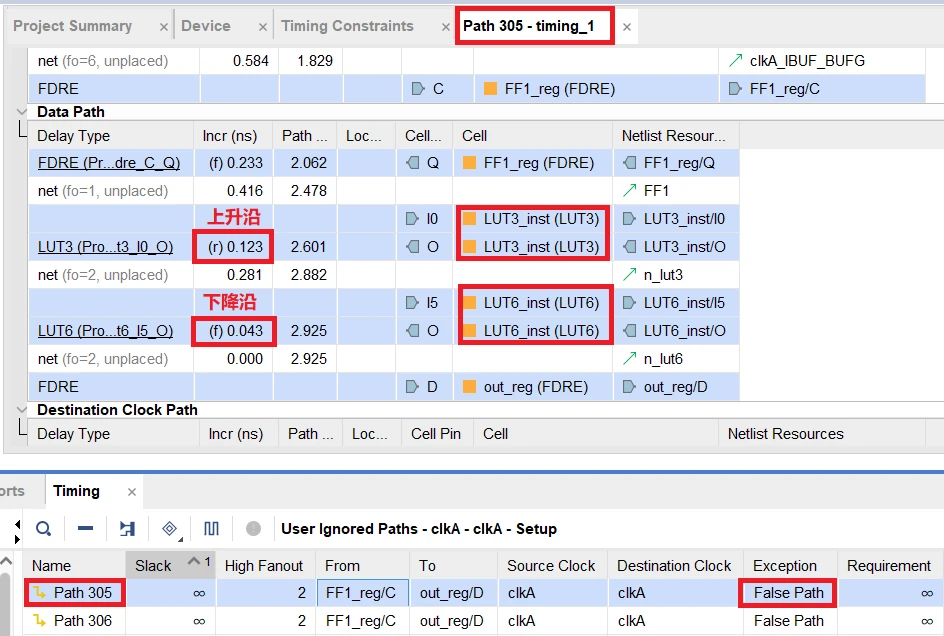

set_false_path -from [all_clocks]g)指定多个through,在设置through时,可以按照时序路径经过先后顺序指定路径,如约束先上升沿经过LUT3_inst,再以下降沿经过LUT6_inst的路径

set_false_path -rise_through [get_cells LUT3_inst] -fall_through [get_cells LUT6_inst]对应的路径约束生效

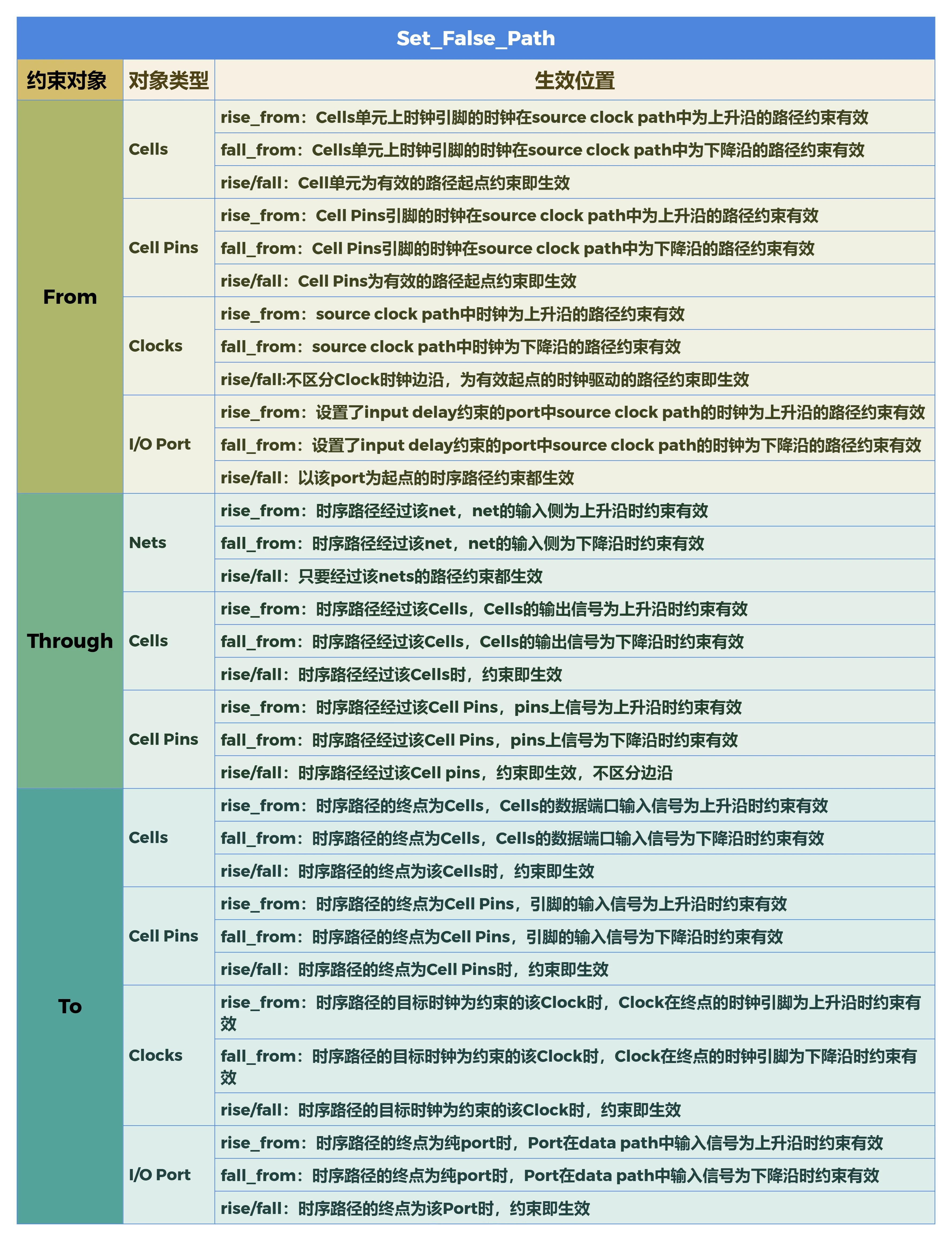

3.4.3 约束对象总结

Set_False_path各约束对象与边沿生效的关系如下图

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

相关文章:

时序约束高级进阶使用详解四:Set_False_Path

目录 一、背景 二、Set_False_Path 2.1 Set_false_path常用场景 2.2 Set_false_path的优势 2.3 Set_false_path设置项 2.4 细节区分 三、工程示例 3.1 工程代码 3.2 时序约束如下 3.3 时序报告 3.4 常规场景 3.4.1 设计代码 3.4.2 约束场景 3.4.3 约束对象总结…...

20250428 - 20250511)

每日定投40刀BTC(16)20250428 - 20250511

定投 坚持 《恒道》 长河九曲本微流,岱岳摩云起累丘。 铁杵十年销作刃,寒窗五鼓淬成钩。已谙蜀栈盘空险,更蓄湘竹带泪遒。 莫问枯荣何日证,星霜满鬓亦从头。...

C# 高效处理海量数据:解决嵌套并行的性能陷阱

C# 高效处理海量数据:解决嵌套并行的性能陷阱 问题场景 假设我们需要在 10万条ID 和 1万个目录路径 中,快速找到所有满足以下条件的路径: 路径本身包含ID字符串该路径的子目录中也包含同名ID 初始代码采用Parallel.ForEach嵌套Task.Run&am…...

】线程安全问题)

【Java EE初阶 --- 多线程(初阶)】线程安全问题

乐观学习,乐观生活,才能不断前进啊!!! 我的主页:optimistic_chen 我的专栏:c语言 ,Java 欢迎大家访问~ 创作不易,大佬们点赞鼓励下吧~ 文章目录 线程不安全的原因根本原因…...

从InfluxDB到StarRocks:Grab实现Spark监控平台10倍性能提升

Grab 是东南亚领先的超级应用,业务涵盖外卖配送、出行服务和数字金融,覆盖东南亚八个国家的 800 多个城市,每天为数百万用户提供一站式服务,包括点餐、购物、寄送包裹、打车、在线支付等。 为了优化 Spark 监控性能,Gr…...

《Redis应用实例》学习笔记,第一章:缓存文本数据

前言 最近在学习《Redis应用实例》,这本书并没有讲任何底层,而是聚焦实战用法,梳理了 32 种 Redis 的常见用法。我的笔记在 Github 上,用 Jupyter 记录,会有更好的阅读体验,作者的源码在这里:h…...

Redis 缓存

缓存介绍 Redis 最主要三个用途: 1)存储数据(内存数据库) 2)消息队列 3)缓存 对于硬件的访问速度,通常有以下情况: CPU 寄存器 > 内存 > 硬盘 > 网络 缓存的核心…...

Apache Flink 与 Flink CDC:概念、联系、区别及版本演进解析

Apache Flink 与 Flink CDC:概念、联系、区别及版本演进解析 在实时数据处理和流式计算领域,Apache Flink 已成为行业标杆。而 Flink CDC(Change Data Capture) 作为其生态中的重要组件,为数据库的实时变更捕获提供了强大的能力。 本文将从以下几个方面进行深入讲解: 什…...

:常见缓存 概念、问题、现象 及 预防问题)

缓存(4):常见缓存 概念、问题、现象 及 预防问题

常见缓存概念 缓存特征: 命中率、最大元素、清空策略 命中率:命中率返回正确结果数/请求缓存次数 它是衡量缓存有效性的重要指标。命中率越高,表明缓存的使用率越高。 最大元素(最大空间):缓存中可以存放的最大元素的…...

)

实战项目6(09)

目录 任务场景一 【r1配置】 【r2配置】 【r3配置】 任务场景二 【r1配置】 【r2配置】 【r3配置】 任务场景三 【r1配置】 【r2配置】 【r3配置】 任务场景一 按照下图完成网络拓扑搭建和配置 任务要求:在…...

MySQL 数据库故障排查指南

MySQL 数据库故障排查指南 本指南旨在帮助您识别和解决常见的 MySQL 数据库故障。我们将从问题识别开始,逐步深入到具体的故障类型和排查步骤。 1. 问题识别与信息收集 在开始排查之前,首先需要清晰地了解问题的现象和范围。 故障现象: 数…...

MacOS Python3安装

python一般在Mac上会自带,但是大多都是python2。 python2和python3并不存在上下版本兼容的情况,所以python2和python3可以同时安装在一台设备上,并且python3的一些语法和python2并不互通。 所以在Mac电脑上即使有自带python,想要使…...

锁相放大技术:从噪声中提取微弱信号的利器

锁相放大技术:从噪声中提取微弱信号的利器 一、什么是锁相放大? 锁相放大(Lock-in Amplification)是一种用于检测微弱信号的技术,它能够从强噪声背景中提取出我们感兴趣的特定信号。想象一下在嘈杂的派对上听清某个人…...

机器学习总结

1.BN【batch normalization】 https://zhuanlan.zhihu.com/p/93643523 减少 2.L1L2正则化 l1:稀疏 l2:权重减小 3.泛化误差 训练误差计算了训练集的误差,而泛化误差是计算全集的误差。 4.dropout 训练过程中神经元p的概率失活 一文彻底搞懂深度学习&#x…...

基于神经网络的无源雷达测向系统仿真实现

基于神经网络的无源雷达测向系统仿真实现 项目概述 本项目实现了基于卷积神经网络(CNN)的无源雷达方向到达角(DOA)估计系统。通过深度学习方法,系统能够从接收到的雷达信号中准确估计出信号源的方向,适用于单目标和多目标场景。相比传统的DOA估计算法&…...

《用MATLAB玩转游戏开发》Flappy Bird:小鸟飞行大战MATLAB趣味实现

《用MATLAB玩转游戏开发:从零开始打造你的数字乐园》基础篇(2D图形交互)-Flappy Bird:小鸟飞行大战MATLAB趣味实现 文章目录 《用MATLAB玩转游戏开发:从零开始打造你的数字乐园》基础篇(2D图形交互…...

【C/C++】跟我一起学_C++同步机制效率对比与优化策略

文章目录 C同步机制效率对比与优化策略1 效率对比2 核心同步机制详解与适用场景3 性能优化建议4 场景对比表5 总结 C同步机制效率对比与优化策略 多线程编程中,同步机制的选择直接影响程序性能与资源利用率。 主流同步方式: 互斥锁原子操作读写锁条件变量无锁数据…...

linux 三剑客命令学习

grep Grep 是一个命令行工具,用于在文本文件中搜索打印匹配指定模式的行。它的名称来自于 “Global Regular Expression Print”(全局正则表达式打印),它最初是由 Unix 系统上的一种工具实现的。Grep 工具在 Linux 和其他类 Unix…...

【js基础笔记] - 包含es6 类的使用

文章目录 js基础js 预解析js变量提升 DOM相关知识节点选择器获取属性节点创建节点插入节点替换节点克隆节点获取节点属性获取元素尺寸获取元素偏移量标准的dom事件流阻止事件传播阻止默认行为事件委托 正则表达式js复杂类型元字符 - 基本元字符元字符 - 边界符元字符 - 限定符元…...

》PDF下载)

《Linux命令行大全(第2版)》PDF下载

内容简介 本书对Linux命令行进行详细的介绍,全书内容包括4个部分,第一部分由Shell的介绍开启命令行基础知识的学习之旅;第二部分讲述配置文件的编辑,如何通过命令行控制计算机;第三部分探讨常见的任务与必备工具&…...

)

补补表面粗糙度的相关知识(一)

表面粗糙度,或简称粗糙度,是指表面不光滑的特性。这个在机械加工行业内可以说是绝绝的必备知识之一,但往往也是最容易被忽略的,因为往往天天接触的反而不怎么关心,或者没有真正的去认真学习掌握。对于像我一样…...

Python实用工具:pdf转doc

该工具只能使用在英文目录下,且无法转换出图片,以及文本特殊格式。 下载依赖项 pip install PyPDF2 升级依赖项 pip install PyPDF2 --upgrade 查看库版本 python -c "import PyPDF2; print(PyPDF2.__version__)" 下载第二个依赖项 pip i…...

基于Dify实现对Excel的数据分析

在dify部署完成后,大家就可以基于此进行各种应用场景建设,目前dify支持聊天助手(包括对话工作流)、工作流、agent等模式的场景建设,我们在日常工作中经常会遇到各种各样的数据清洗、格式转换处理、数据统计成图等数据分…...

Win全兼容!五五 Excel Word 转 PDF 工具解决多场景转换难题

各位办公小能手们!今天给你们介绍一款超牛的工具——五五Excel Word批量转PDF工具V5.5版。这玩意儿专注搞批量格式转换,能把Excel(.xls/.xlsx)和Word(.doc/.docx)文档唰唰地变成PDF格式。 先说说它的核心功…...

java加强 -Collection集合

集合是一种容器,类似于数组,但集合的大小可变,开发中也非常常用。Collection代表单列集合,每个元素(数据)只包含1个值。Collection集合分为两类,List集合与set集合。 特点 List系列集合&#…...

BGP实验练习1

需求: 要求五台路由器的环回地址均可以相互访问 需求分析: 1.图中存在五个路由器 AR1、AR2、AR3、AR4、AR5,分属不同自治系统(AS),AR1 在 AS 100,AR2 - AR4 在 AS 200,AR5 在 AS …...

Nginx location静态文件映射配置

遇到问题? 以下这个Nginx的配置,愿意为访问https://abc.com会指向一个动态网站,访问https://abc.com/tongsongzj时会访问静态网站,但是配置之后(注意看后面那个location /tongsongzj/静态文件映射的配置)&…...

四、Hive DDL表定义、数据类型、SerDe 与分隔符核心

在理解了 Hive 数据库的基本操作后,本篇笔记将深入到数据存储的核心单元——表 (Table) 的定义和管理。掌握如何创建表、选择合适的数据类型、以及配置数据的读写方式 (特别是 SerDe 和分隔符),是高效使用 Hive 的关键。 一、创建表 (CREATE TABLE)&…...

每日脚本 5.11 - 进制转换和ascii字符

前置知识 python中各个进制的开头 二进制 : 0b 八进制 : 0o 十六进制 : 0x 进制转换函数 : bin() 转为2进制 oct() 转换为八进制的函数 hex() 转换为16进制的函数 ascii码和字符之间的转换 : chr(97) 码转为字符 …...

cookie和session的区别

一、基本概念 1. Cookie 定义:Cookie 是服务器发送到用户浏览器并保存在本地的一小块数据(通常小于4KB),浏览器会在后续请求中自动携带该数据。作用:用于跟踪用户状态(如登录状态)、记…...

Kotlin Multiplatform--03:项目实战

Kotlin Multiplatform--03:项目实战 引言配置iOS开发环境配置项目环境运行程序 引言 本章将会带领读者进行项目实战,了解如何从零开始编译一个能同时在Android和iOS运行的App。开发环境一般来说需要使用Macbook,笔者没试过Windows是否能开发。…...

图形学、人机交互、VR/AR领域文献速读【持续更新中...】

(1)笔者在时间有限的情况下,想要多积累一些自身课题之外的新文献、新知识,所以开了这一篇文章。 (2)想通过将文献喂给大模型,并向大模型提问的方式来快速理解文献的重要信息(如基础i…...

opencascade.js stp vite 调试笔记

Hello, World! | OpenCascade.js cnpm install opencascade.js cnpm install vite-plugin-wasm --save-dev 当你不知道文件写哪的时候trae还是有点用的 ‘’‘ import { defineConfig } from vite; import wasm from vite-plugin-wasm; import rollupWasm from rollup/plugi…...

openharmony系统移植之gpu mesa3d适配

openharmony系统移植之gpu mesa3d适配 文章目录 openharmony系统移植之gpu mesa3d适配1. 环境说明2. gpu内核panfrost驱动2.1 使能panfrost驱动2.2 panfrost dts配置 3. buildroot下测试gpu驱动3.1 buildroot配置编译 4. ohos下mesa3d适配4.1 ohos下mesa3d编译调试4.1.2 编译4.…...

Java开发经验——阿里巴巴编码规范经验总结2

摘要 这篇文章是关于Java开发中阿里巴巴编码规范的经验总结。它强调了避免使用Apache BeanUtils进行属性复制,因为它效率低下且类型转换不安全。推荐使用Spring BeanUtils、Hutool BeanUtil、MapStruct或手动赋值等替代方案。文章还指出不应在视图模板中加入复杂逻…...

Linux中常见开发工具简单介绍

目录 apt/yum 介绍 常用命令 install remove list vim 介绍 常用模式 命令模式 插入模式 批量操作 底行模式 模式替换图 vim的配置文件 gcc/g 介绍 处理过程 预处理 编译 汇编 链接 库 静态库 动态库(共享库) make/Makefile …...

深入理解深度Q网络DQN:基于python从零实现

DQN是什么玩意儿? 深度Q网络(DQN)是深度强化学习领域里一个超厉害的算法。它把Q学习和深度神经网络巧妙地结合在了一起,专门用来搞定那些状态空间维度特别高、特别复杂的难题。它展示了用函数近似来学习价值函数的超能力…...

使用lldb看看Rust的HashMap

目录 前言 正文 读取桶的状态 获取键值对 键值对的指针地址 此时,读取数据 读取索引4的键值对 多添加几个键值对 使用i32作为键,&str作为值 使用i32作为键,String作为值 前言 前面使用ldb看了看不同的类型,这篇再使用…...

Vue3简易版购物车的实现。

文章目录 一、话不多说,直接上代码? 一、话不多说,直接上代码? <template><div><input type"text" placeholder"请输入内容" v-model"keywords"><button click"addGood…...

比亚迪全栈自研生态的底层逻辑

比亚迪全栈自研生态的底层逻辑:汽车工程师必须理解的闭环技术革命 引言:当技术壁垒成为护城河 2023年比亚迪销量突破302万辆的震撼数据背后,隐藏着一个更值得工程师深思的事实:其全栈自研体系覆盖了新能源汽车83%的核心零部件。这…...

)

[Java实战]Spring Boot 快速配置 HTTPS 并实现 HTTP 自动跳转(八)

[Java实战]Spring Boot 快速配置 HTTPS 并实现 HTTP 自动跳转(八) 引言 在当今网络安全威胁日益严峻的背景下,为 Web 应用启用 HTTPS 已成为基本要求。Spring Boot 提供了简单高效的方式集成 HTTPS 支持,无论是开发环境测试还是生产环境部署࿰…...

5.1.1 WPF中Command使用介绍

WPF 的命令系统是一种强大的输入处理机制,它比传统的事件处理更加灵活和可重用,特别适合 MVVM (Model, View, ViewModel)模式开发。 一、命令系统核心概念 1.命令系统基本元素: 命令(Command): 即ICommand类,使用最多的是RoutedCommand,也可以自己继承ICommand使用自定…...

桥梁模式)

设计模式简述(十九)桥梁模式

桥梁模式 描述基本组件使用 描述 桥梁模式是一种相对简单的模式,通常以组合替代继承的方式实现。 从设计原则来讲,可以说是单一职责的一种体现。 将原本在一个类中的功能,按更细的粒度拆分到不同的类中,然后各自独立发展。 基本…...

常用设计模式

一、什么是设计模式 设计模式(Design Pattern)是一套被反复使用、多数人知晓的、经过分类编目的代码设计经验总结,旨在解决面向对象设计中反复出现的问题,提升代码的可重用性、可理解性和可靠性。以下从多个维度详细讲解ÿ…...

20242817-李臻-课下作业:Qt和Sqlite

实验内容 阅读附件内容,编译运行附件中第一章,第三章的例子。 实验过程 第一章 t1实践 #include <QApplication> #include <QWidget> #include <QPushButton> #include <QVBoxLayout>int main(int argc, char *argv[]) {QA…...

嵌入式机器学习平台Edge Impulse图像分类 – 快速入门

陈拓 2025/05/08-2025/05/11 1. 简介 官方网址 https://edgeimpulse.com/ 适用于任何边缘设备的人工智能: Gateways - 网关 Sensors & Cameras - 传感器和摄像头 Docker Containers - Docker容器 MCUs, NPUs, CPUs, GPUs 构建数据集、训练模型并优化库以…...

JavaWeb, Spring, Spring Boot

出现时间 JavaWeb - Spring - Spring Boot 一、JavaWeb 的发展历程 Servlet 和 JSP: Servlet:1997 年首次发布,用于处理 HTTP 请求和响应。 JSP:1999 年首次发布,用于动态生成 HTML 页面。 特点:提供了基…...

upload-labs靶场通关详解:第五关

一、分析源代码 $is_upload false; $msg null; if (isset($_POST[submit])) {if (file_exists(UPLOAD_PATH)) {$deny_ext array(".php",".php5",".php4",".php3",".php2",".html",".htm",".ph…...

【问题】Watt加速github访问速度:好用[特殊字符]

前言 GitHub 是全球知名的代码托管平台,主要用于软件开发,提供 Git 仓库托管、协作工具等功能,经常要用到,但是国内用户常因网络问题难以稳定访问 。 Watt Toolkit(原名 Steam)是由江苏蒸汽凡星科技有限公…...

GitHub打开缓慢甚至失败的解决办法

在C:\Windows\System32\drivers\etc的hosts中增加如下内容: 20.205.243.166 github.com 199.59.149.236 github.global.ssl.fastly.net185.199.109.153 http://assets-cdn.github.com 185.199.108.153 http://assets-cdn.github.com 185.199.110.153 http://asset…...