ZYNQB笔记(十六):AXI DMA 环路测试

版本:Vivado2020.2(Vitis)

任务:使用 PL 端的 AXI DMA IP 核实现对 DDR3 中数据的读取与写入,实现数据环回,具体流程为:

PS 端产生测试数据并写入到 DDR3 中,然后 PL 端的 AXI DMA IP 核从 DDR3 中读取数据,将读取到的数据存储到 AXI Stream Data FIFO 中(模拟AXI Stream 外设)。然后再将 AXI Stream Data FIFO 中的数据写回到 DDR3 中。判断从 DDR3 中读取的数据和写入的数据是否一致。

目录

一、介绍

(1)DMA

(2)AXI DMA IP核

二、硬件设计

(1)整体系统框图

(2)AXI DAM IP 核配置

(3)ZYNQ配置

(4)其他配置

三、软件设计

(1)AXI DMA 编程顺序

(2)完整代码

四、效果

一、介绍

(1)DMA

DMA(Direct Memory Access,直接存储器访问)是一种 硬件加速的数据传输技术,允许外设或存储单元之间 直接交换数据,无需CPU逐字节参与搬运,从而解放CPU算力。

当使用DMA时,CPU向DMA控制器发出一个存储传输请求,当DMA控制器接收到请求就会将数据从源地址搬运到目的地址。在数据搬运过程中不占用CPU资源,CPU可以执行其它操作,当传输完成时DMA以中断的方式通知CPU。

ZYNQ 提供了两种 DMA ,一种是PS中的DMA控制器(DMAC) ,通过GP口与PL端连接;另一种是PL中的 AXI DMA IP核(软核)。由于 PS 端的 DMAC 必须通过驻留在内存中的 DMA 指令编程,这些程序往往由 CPU 运行,因此需要 部分的 CPU 参与,所以在使用 PS 端的 DMAC 搬运数据时,不能完全释放 CPU 的资源。因此本实验选择 PL 端的 AXI DMA,在 PL 中添加 AXI DMA IP 核,并利用 AXI_HP 接口完成高速的数据传输。

(2)AXI DMA IP核

AXI DMA (Direct Memory Access,AXI 直接内存访问) 是 ZYNQ SoC 中用于高性能数据传输的IP核,通过AXI总线实现 PS 与 PL 之间的直接数据搬运,无需CPU介入。通过双通道传输实现高效数据搬运:

AXI DMA 接口类型(简单 DMA):

| 接口类型 | 协议 | 方向 | 主要用途 | 典型连接对象 |

|---|---|---|---|---|

| 控制接口 | AXI4-Lite | CPU → DMA | 配置DMA控制寄存器(启动传输、设置地址、长度、中断使能等) | 处理器(如ARM Cortex、MicroBlaze) |

| 内存接口 | AXI4 Memory-Mapped | DMA ↔ DDR | 用于大数据量传输,有两个方向: - MM2S:从内存读取数据 - S2MM:向内存写入数据 | DDR3/DDR4、片上RAM(BRAM) |

| 外设接口 | AXI4-Stream | DMA ↔ 外设 | 低延迟流式数据传输 - Master:发送数据到外设(MM2S方向) | FPGA逻辑(如FIFO、ADC/DAC、以太网MAC)、高速串行接口(PCIe) |

| 中断接口 | 中断信号 IRQ | DMA → CPU | 通知CPU传输完成或错误事件 | 处理器(如ARM Cortex、MicroBlaze) |

在AXI DMA 中,MM2S(Memory-Mapped to Stream)和S2MM(Stream to Memory-Mapped)是两个核心数据传输方向,分别用于从内存到外设和从外设到内存的数据搬运。

| MM2S | S2MM | |

|---|---|---|

| 数据方向 | 内存 → 外设(Stream) | 外设(Stream) → 内存 |

| 接口协议 | AXI4-MemoryMap → AXI4-Stream | AXI4-Stream → AXI4-MemoryMap |

| 典型场景 | 发送数据(如网络包、视频输出) | 接收数据(如传感器采集、网络收包) |

| 中断触发 | 传输完成或错误时触发 mm2s_introut | 传输完成或错误时触发 s2mm_introu |

| 控制寄存器 | 需配置源地址、传输长度等 | 需配置目的地址、传输长度等 |

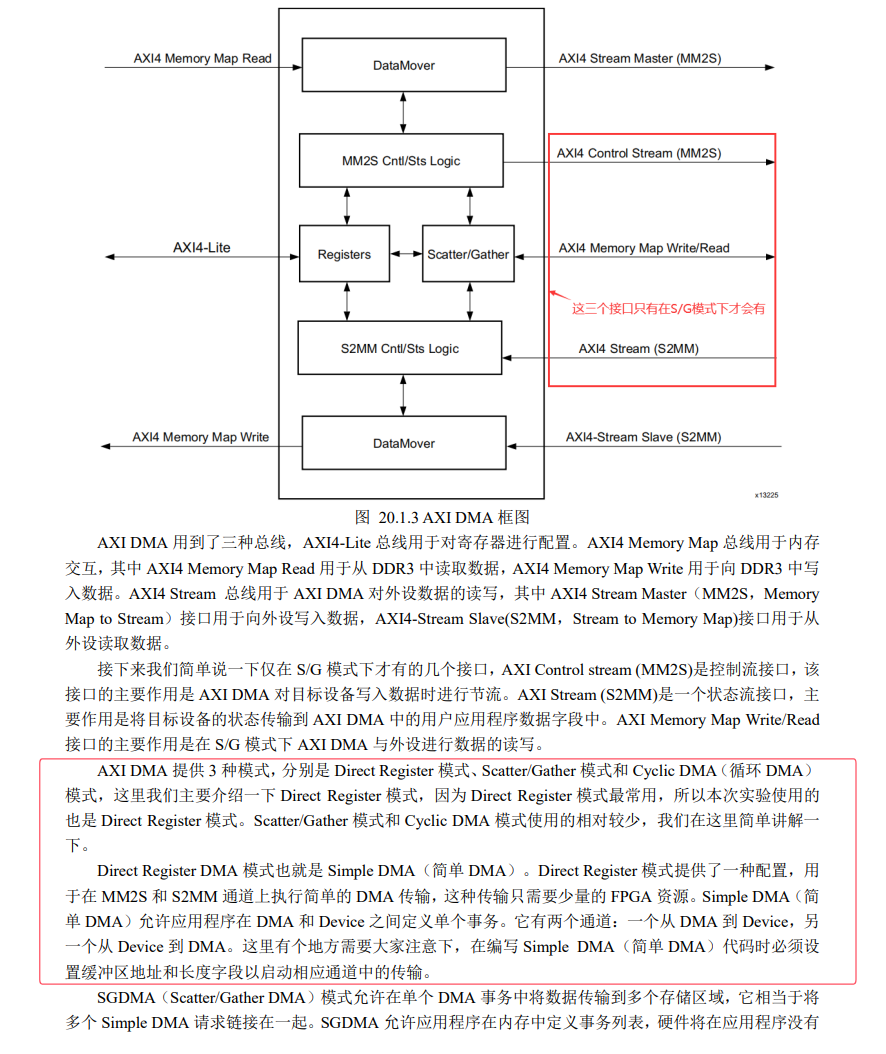

AXI DMA IP 核可在 AXI4 和 AXI4-Stream IP 接口之间提供高带宽直接内存访问。其可选的分散收集模式(SG)还可以从基于处理器的系统中卸载 CPU 的数据移动任务。初始化、状态和管理寄存器可通过 AXI4-Lite 从接口访问,下面 AXI DMA 的介绍为正点原子的资料切片:

二、硬件设计

(1)整体系统框图

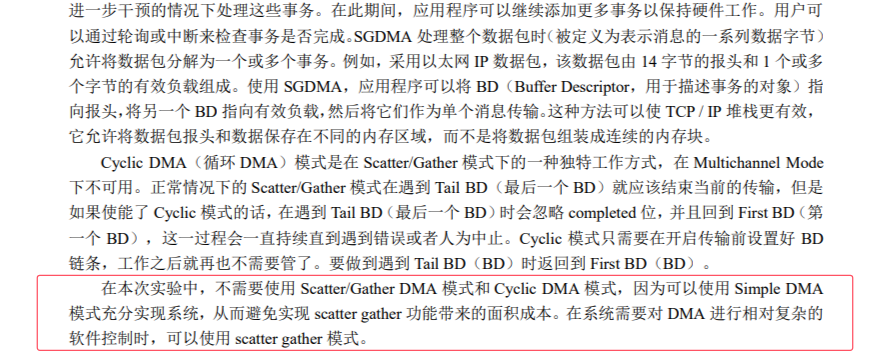

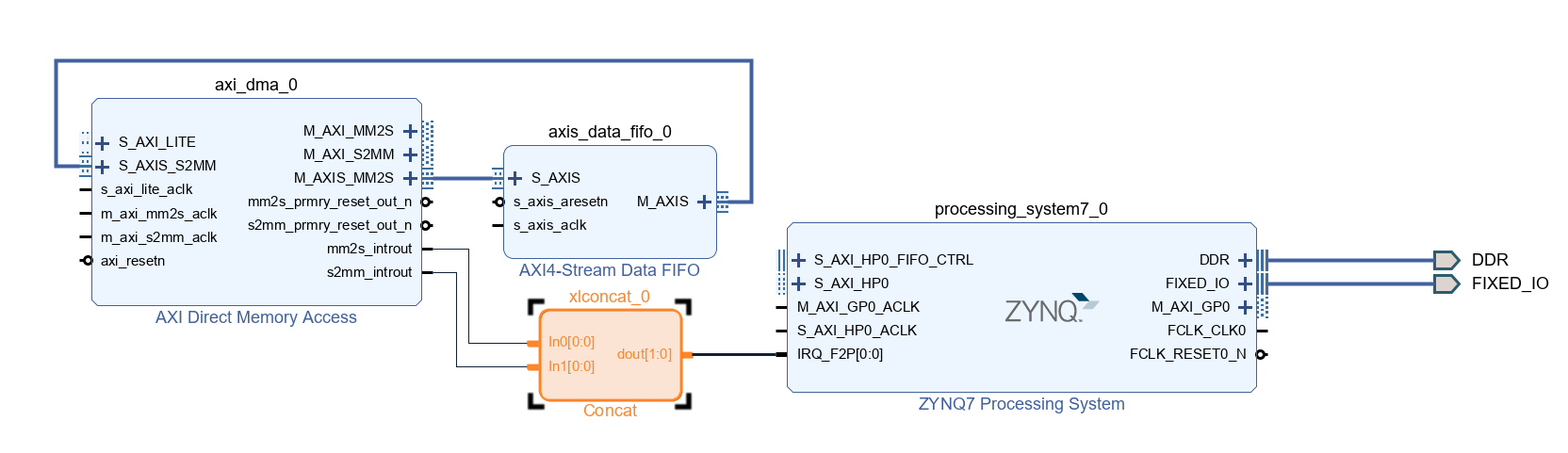

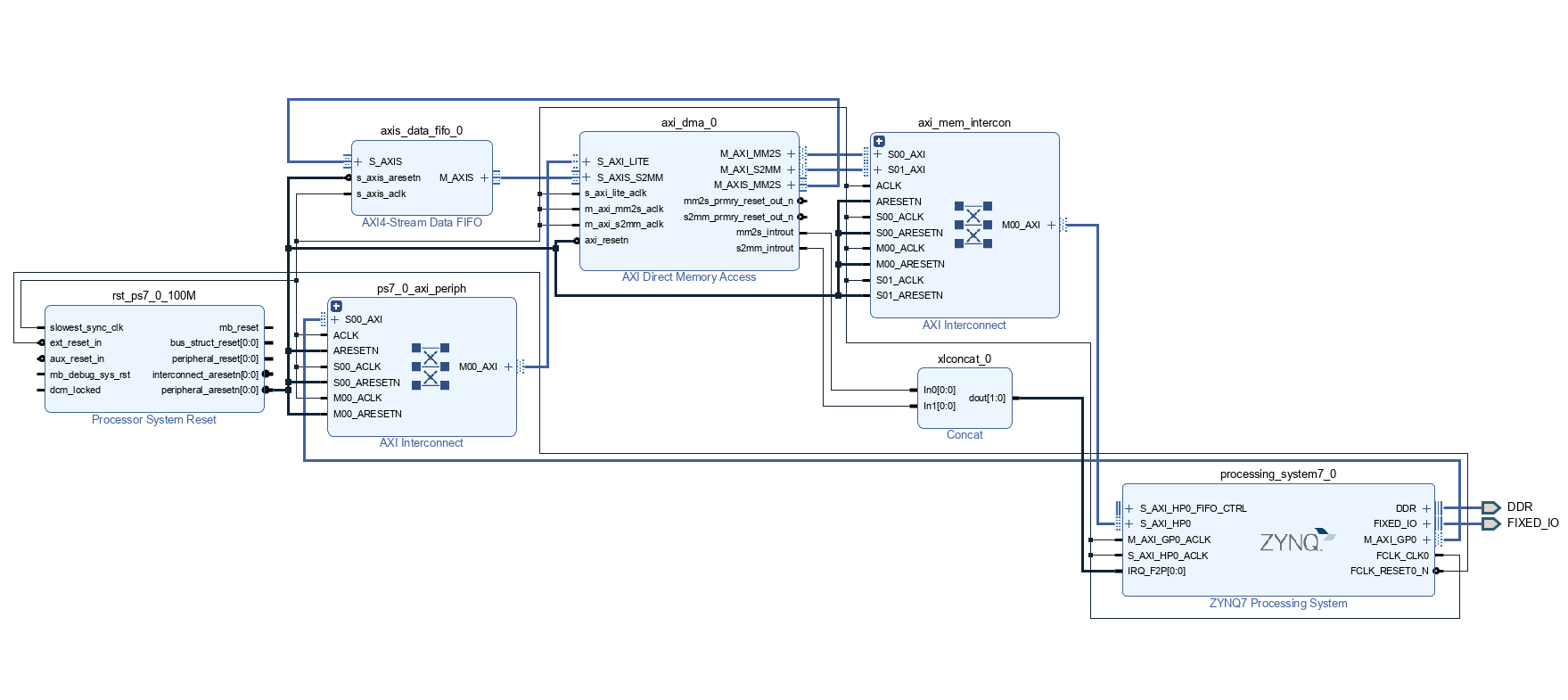

本次实验将 AXI Stream Data FIFO IP 核类比成带 AXI Stream 接口的外设,通过 AXI DMA IP 核实现 DDR3 和外设之间的数据搬运。

前面介绍部分了解到 AXI DMA 有三种类型的接口,用于对 AXI DMA 配置的 AXI-Lite 接口,用于和 DDR3 内存做大量数据读写的存储器映射接口(AXI4 Memory Map Read / Write)以及和外设做数据传输的 AXI4-Stream 流接口(AXI4 Stream Master / Slave)。

AXI DMA 的 AXI4-Lite 接口主要用于 PS 对 AXI DMA 的寄存器进行配置,而 AXI DMA 的存储器映射接口用于读写 DDR3 内存中的数据,这两个接口都涉及到 PL 和 PS 端的数据交互。PL 和 PS 交互的接口可 以使用 HP 或者 GP 接口,HP 可以比 GP 接口提供更高的带宽,由于 PS 对 AXI DMA 的配置数据量较少, 所以可以选择使用 GP 接口;而 AXI DMA 的存储器映射接口用于读写 DDR3 内存中的数据,数据量会比较 大,为了提高 AXI DMA 数据搬运的效率,这里选择使用 HP 接口。无论是选择使用 HP 或者 GP 接口,都需要通过 AXI Interconnect 模块进行转换,因此本次实验需要两个 AXI Interconnect 模块。AXI DMA 的 Stream 流接口直接和带 Stream 流接口的外设连接即可,如本章使用的 AXI Stream Data FIFO。

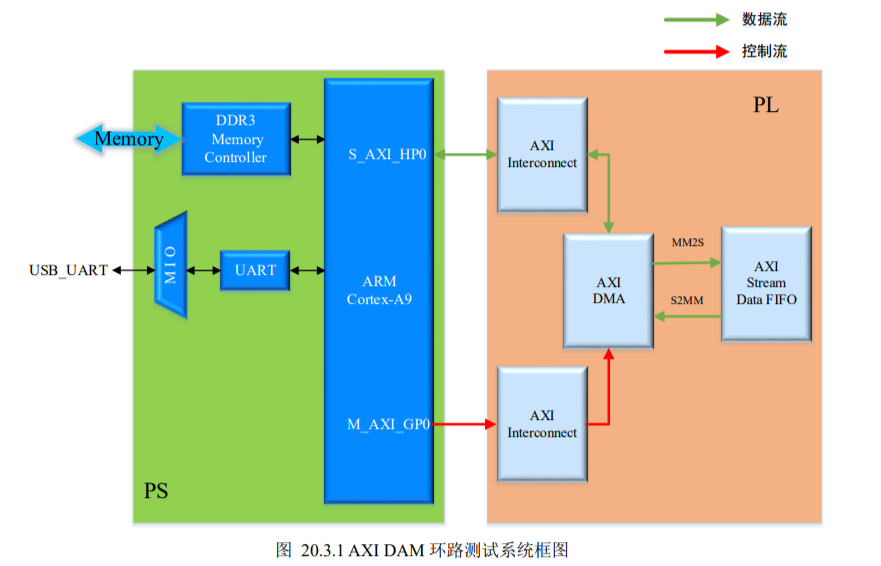

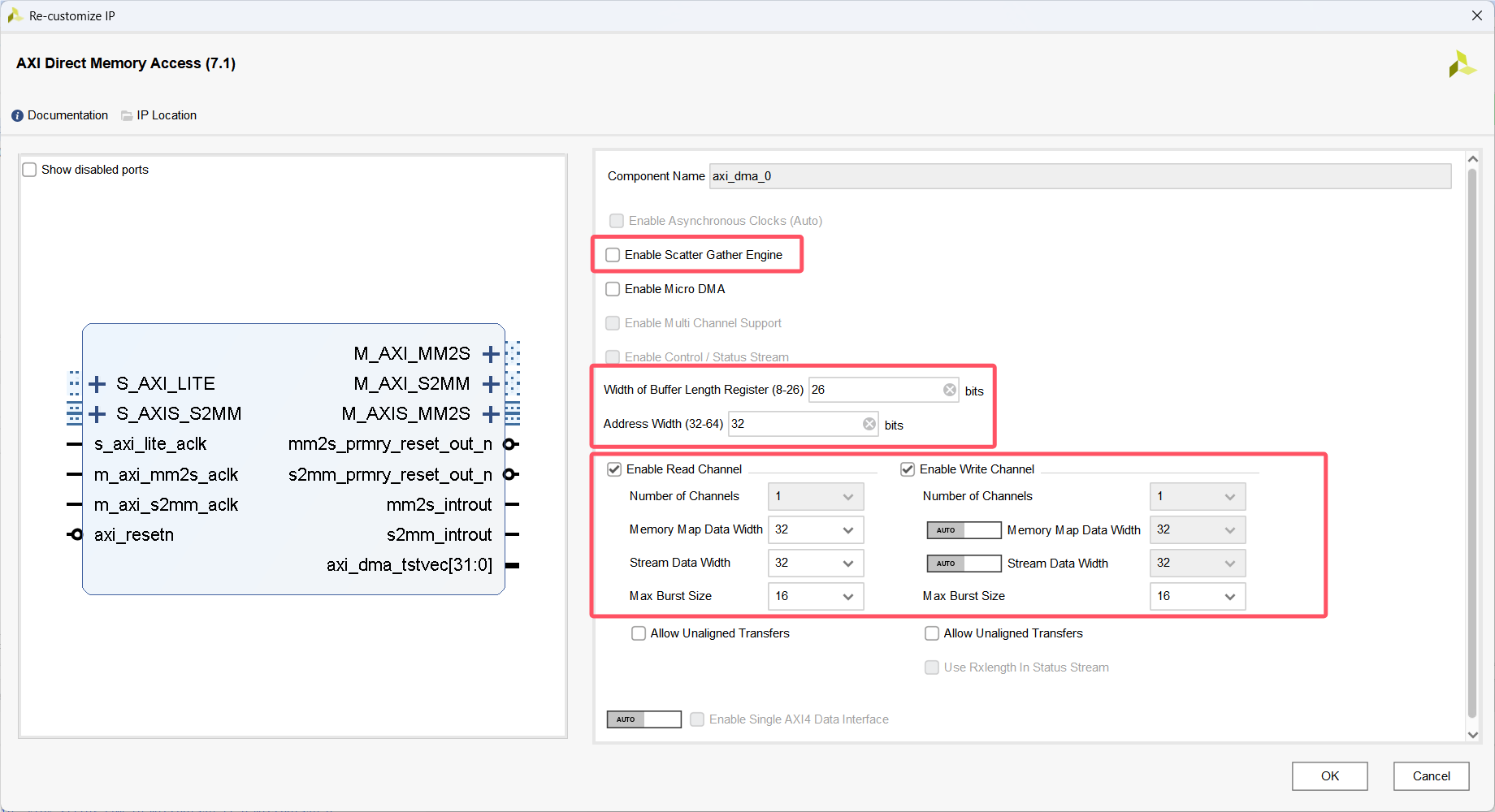

(2)AXI DAM IP 核配置

具体配置如图所示, 注意 DMA 设置为直接寄存器模式 Direct Register Mode(Simple DAM),所以不启用SG模式。本例既读又写,就需要同时启用读(MM2S)、写(S2MM)通道。

| 配置参数 | 说明 | |

|---|---|---|

| Enable Asynchronous Clocks | 允许 MM2S/S2MM/SG/Lite 接口时钟异步运行 | 选项为无法设置,会根据 BD设计中该 IP核的时钟连线自动设置(比如 MM2S 和 S2MM 时钟为异步时就自动允许时钟异步运行) |

| Enable Scatter Gather Engine | 启用 SG模式 | 如果不启用,则 DMA 为直接寄存器模式 Direct Register Mode(Simple DAM) |

| Enable Micro DMA | 优化为精简 DMA | 使能后 IP核硬件资源占用更少,适用于少量数据的 DAM 传输 |

| Width of Buffer Length Register | 缓冲区长度寄存器 宽度 | 该值确定 DMA 传输的最大数据包大小,计算公式:最大字节数=2^LengthWidth-1。 (width = 26 允许传输 67,108,863 字节) |

| Address Width | AXI4 M MAP接口地址位宽 | 指 AXI DMA的 AXI4 Memory Map(MM)接口的地址总线位宽,决定了 DMA控制器可以访问的内存地址范围。 在 ZYNQ 中通常配置为 32位(7000系列)或 64位(UltraScale+)。 |

| Enable read / write channel | 启用 DMA 读/写通道 | 按需设置,本例既读又写,就需要同时启用 |

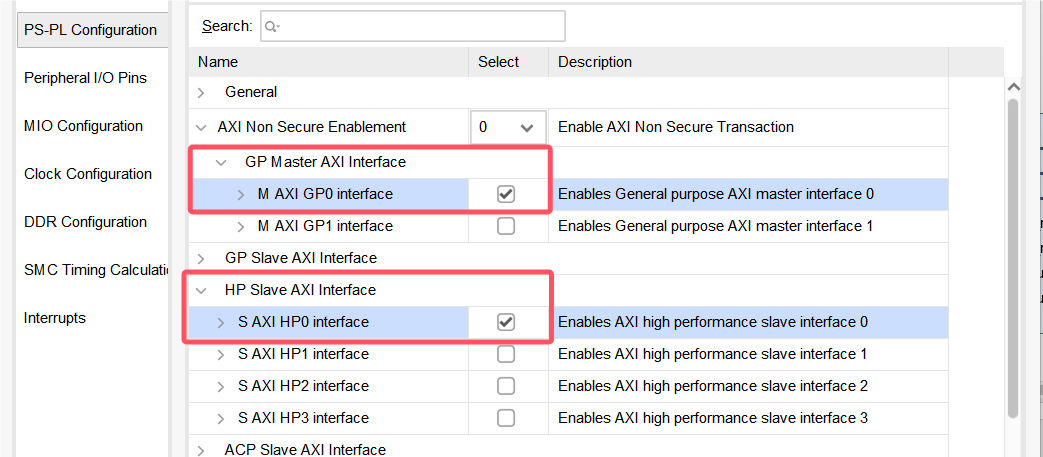

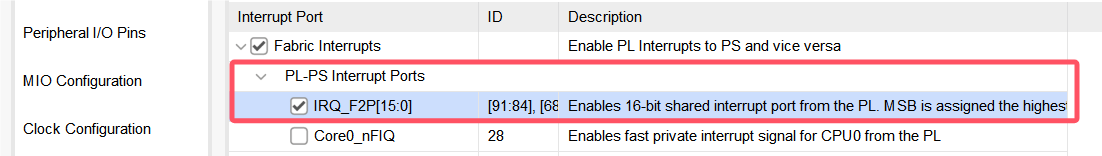

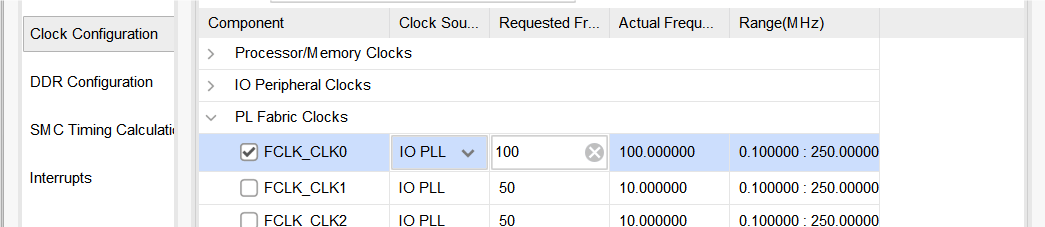

(3)ZYNQ配置

由(1)可知: PS 通过 GP 接口控制 DMA,而 DAM 使用 HP 接口与 PS 进行数据交互,所以配置 ZYNQ 时需要使用一个 GP(Master接口)和一个 HP接口。

此外还使用到了 PL到PS中断、PL时钟、复位、UART。

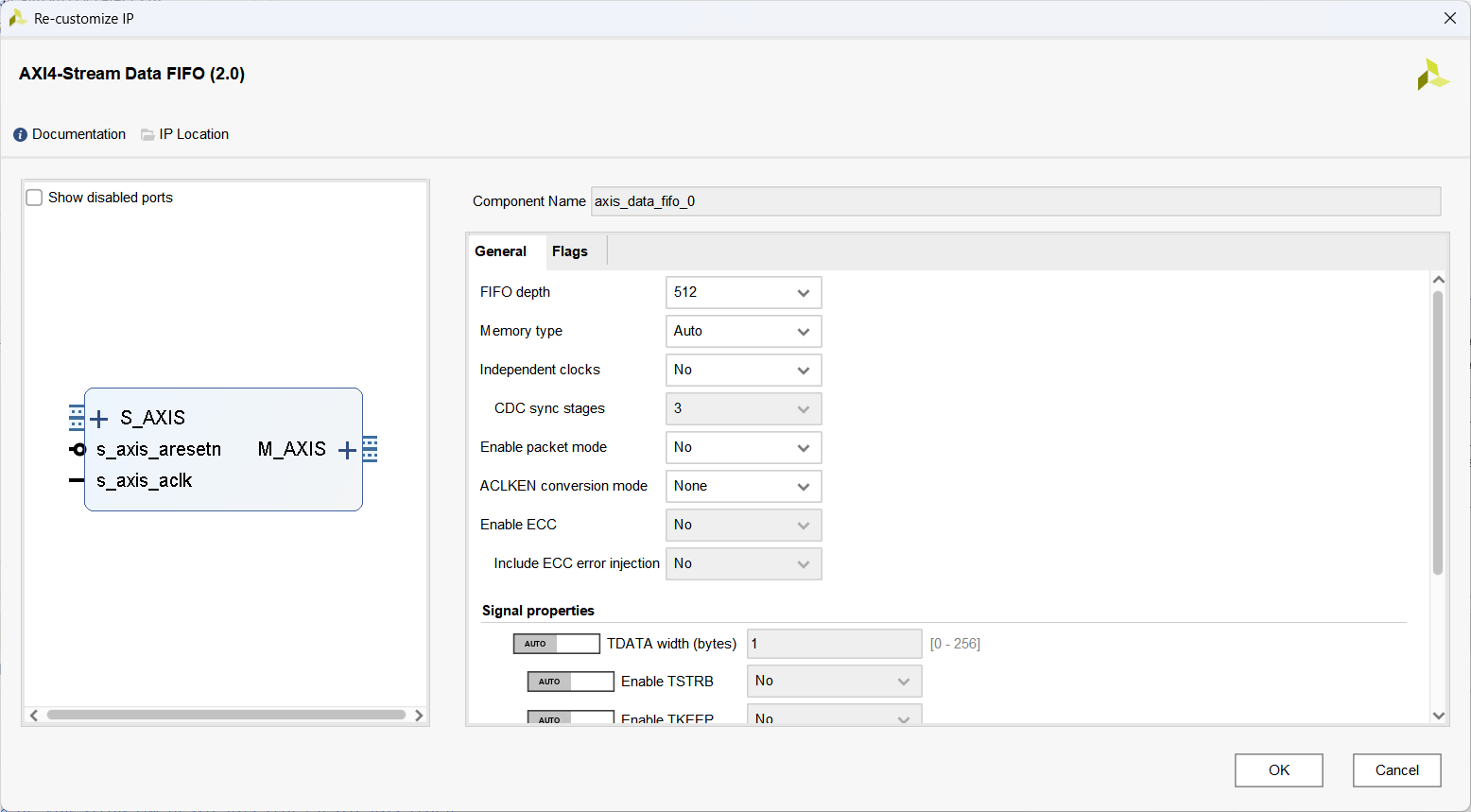

(4)其他配置

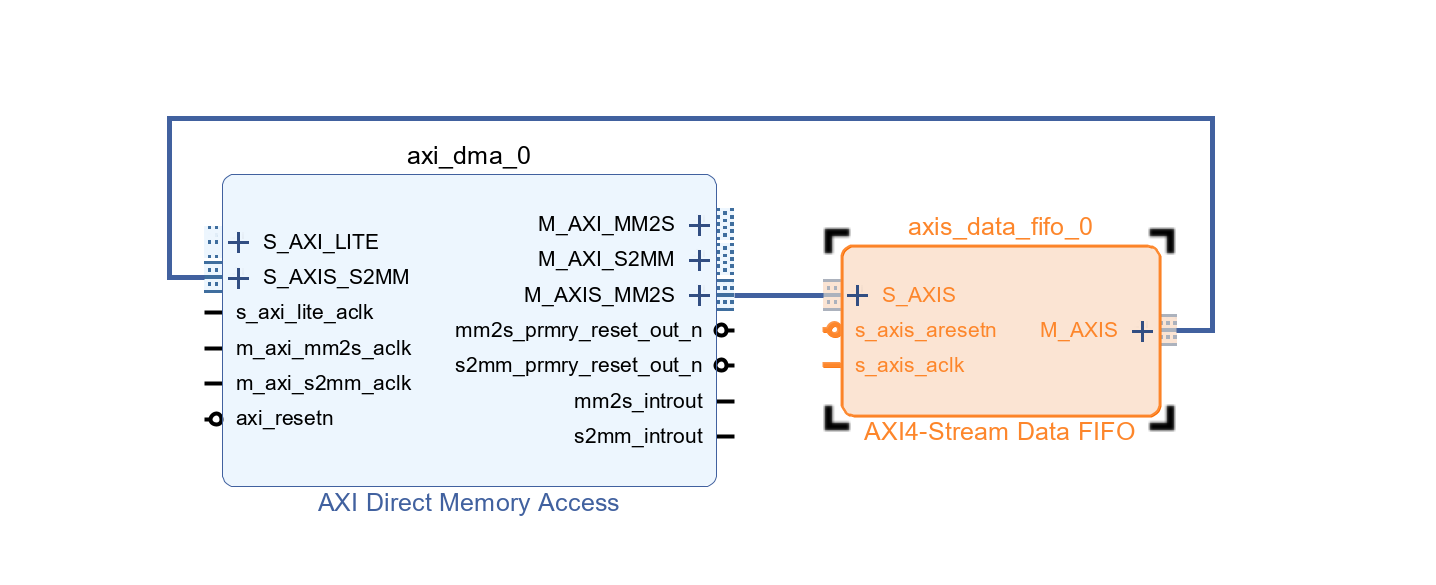

AXI Sream Data FIFO 用于模拟一个带流接口的外设,配置如图所示,直接保持默认即可,FIFO的深度为512,数据宽度是自动设置的。需要将AXI DMA的外设接口(Stream流接口)与 AXI Sream Data FIFO 的Stream流接口连接:

DMA MM2S 方向的流接口,连接 FIFO 流接口(从),用于DMA向FIFO写数据。

DMA S2MM 方向的流接口,连接 FIFO 流接口(主),用于FIFO向DMA传数据。

此外因为 AXI DMA 用到了MM2S和S2MM两个通道,有两个中断输出,而 ZYNQ 的中断输入只有一个多位宽的中断输入端口,需要用到一个 Concat IP核(Concatenation,拼接,是Xilinx FPGA中提供的一个基础IP核,用于将多个输入信号按位拼接成一个更宽的输出信号,仅实现信号的物理连接)将 mm2s_introut、s2mm_introu 两个1位的中断输出信号按位拼接为一个两位的中断输出信号,给到 ZYNQ 中断输入端口。

最后整体 bd 设计部分如图所示:设计检查、Generate Output Products、 Create HDL Wrapper、管脚约束、Gnerate Bitstream、Export Hardware(包含比特流文件)、启动Vitis

三、软件设计

(1)AXI DMA 编程顺序

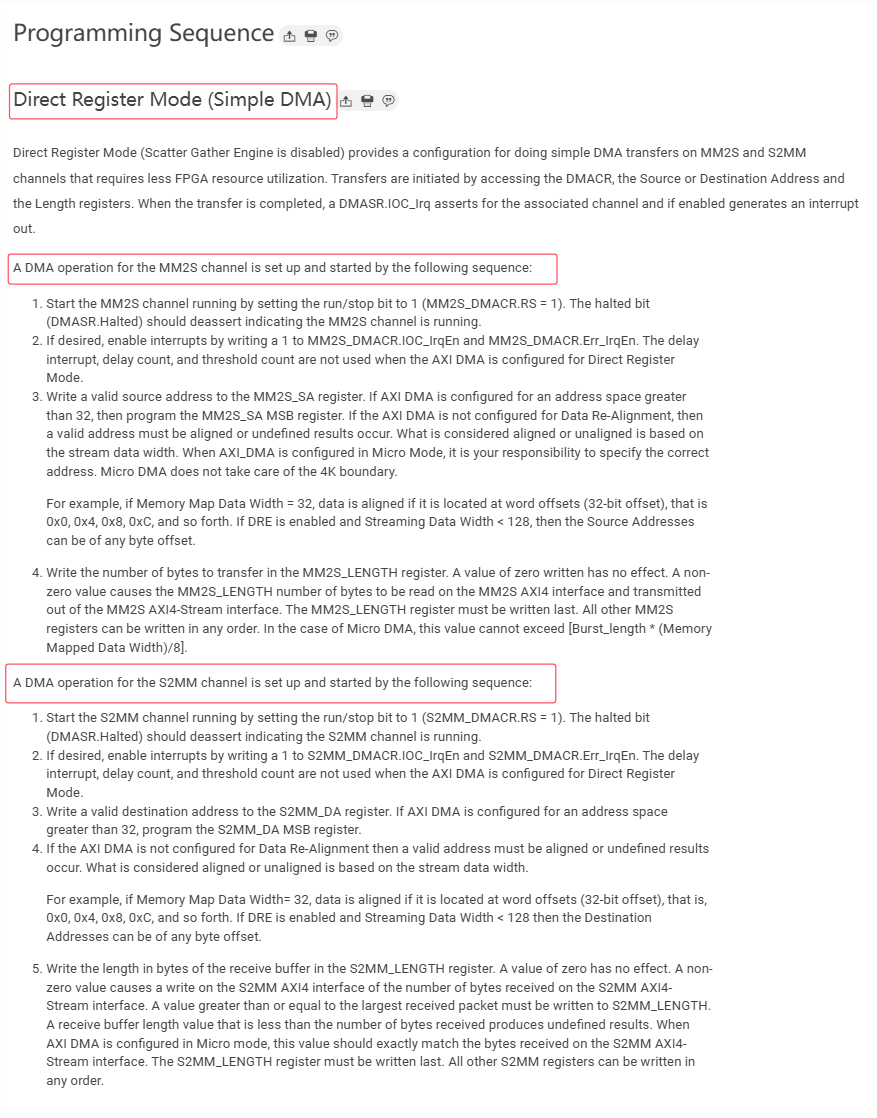

下面是AXI DMA 使用手册中,以直接寄存器模式(简单模式)下 DMA 具体的使用方法,包含该模式的编程顺序介绍、MM2S、S2MM 通道的启动顺序:

总结一下:

AXI DMA编程顺序:

Direct RegisterMode(简单DMA)此模式提供了在MM2s和s2MM通道上进行简单DMA传输的配置,只需较少的FPGA资源通过访问DMACR、源地址或者目的地址和长度寄存器发起DMA传输。当传输完成后,如果使能了产生中断输出,那么DMASR寄存器相关联的通道位会有效。

MM2S 通道启动步骤:

| 步骤 | 操作步骤描述 | 注意事项 |

|---|---|---|

| 1 | 使能 MM2S通道 | - 通过 MM2S_DMACR 寄存器的 RS (Run/Stop) 位使能。- 确保通道处于停止状态( RS=0)后再配置其他寄存器。 |

| 2 | 根据需求,使能中断寄存器 | - 中断使能位在 MM2S_DMACR 寄存器中(如 IOC_IrqEn 用于传输完成中断)。- 若需PS端响应中断,需配置GIC或处理器中断控制器。 |

| 3 | 写一个有效的源地址到 MM2S_SA 寄存器 | - 地址需按数据位宽对齐(如32位数据需4字节对齐)。 - 若未使能 DRE(Data Realignment Engine),需严格对齐,否则可能读取错误数据。 |

| 4 | 写传输的字节数到 MM2S_LENGTH 寄存器 | - 写入非0值(0无效),且必须 最后配置此寄存器。 - 写入后DMA立即开始传输。 - 其他寄存器(如地址、控制)需在此前配置完成。 |

S2MM 通道启动步骤:

| 步骤 | 操作步骤描述 | 注意事项 |

|---|---|---|

| 1 | 使能 S2MM通道 | - 通过 S2MM_DMACR 寄存器的 RS (Run/Stop) 位使能。- 确保通道处于停止状态( RS=0)后再配置其他寄存器。 |

| 2 | 根据需求,使能中断寄存器 | - 中断使能位在 S2MM_DMACR 寄存器中(如 IOC_IrqEn 用于传输完成中断)。- 若需PS端响应中断,需配置GIC或处理器中断控制器。 |

| 3 | 写一个有效的目的地址到 S2MM_DA 寄存器 | - 地址需按数据位宽对齐(如32位数据需4字节对齐)。 - 若未使能 DRE(Data Realignment Engine),需严格对齐,否则可能写入错误地址。 |

| 4 | 写传输的字节数到 S2MM_LENGTH 寄存器 | - 写入非零值(0无效),且必须 最后配置此寄存器。 - 写入后DMA立即开始传输。 - 其他寄存器(如地址、控制)需在此前配置完成。 |

(2)完整代码

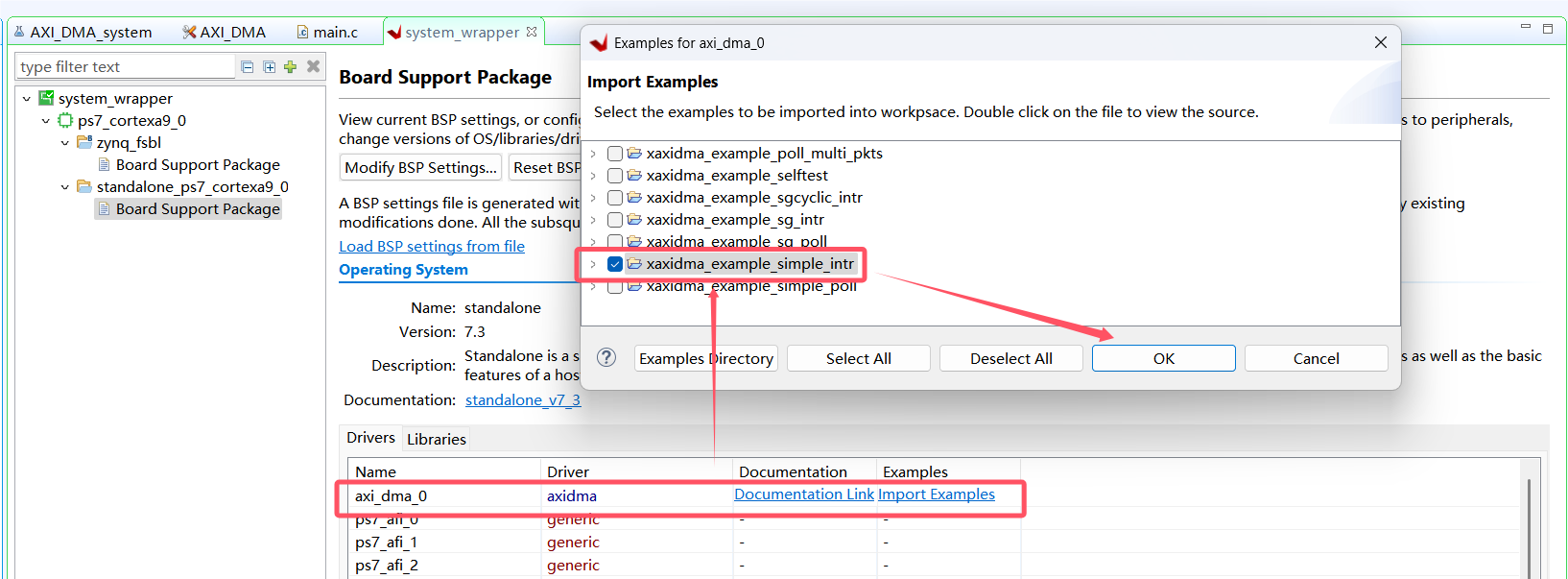

导入Xilinx的 axi_dma 的工程模板,选着简单DMA模式中断的示例,以简单DMA模式使用AXI DMA 的代码是基于这个模板实现的,方便参考与照搬套用。

#include "xil_printf.h"

#include "xparameters.h"

#include "xaxidma.h"

#include "xscugic.h"//======================宏定义=====================////DDR中的地址宏定义

#define DDR_BASE_ADDR XPAR_PS7_DDR_0_S_AXI_BASEADDR //DDR的基地址(在xparameters.h或lscript.ld查看)

#define MEM_BASE_ADDR (DDR_BASE_ADDR + 0x01000000) //DDR中存储数据的基地址(确保在堆栈已使用DDR范围之后,lscript.ld查看)

#define TX_BUFFER_BASE (MEM_BASE_ADDR + 0x00100000) //存储发送数据的基地址

#define RX_BUFFER_BASE (MEM_BASE_ADDR + 0x00300000) //存储接收数据的基地址#define RESET_TIMEOUT_COUNTER 10000 //复位时间计数

#define MAX_PKT_LEN 0x100 //发送包长度(测试数据个数,256)#define INTC_DEVICE_ID XPAR_SCUGIC_SINGLE_DEVICE_ID //中断控制器(GIC)ID

#define AXI_DMA_ID XPAR_AXIDMA_0_DEVICE_ID //AXI DMA器件ID

#define TX_INTR_ID XPAR_FABRIC_AXIDMA_0_MM2S_INTROUT_VEC_ID//DMA发送通道中断号(mm2s_introut)

#define RX_INTR_ID XPAR_FABRIC_AXIDMA_0_S2MM_INTROUT_VEC_ID//DMA通道通道中断号(s2mm_introut)//===================函数变量声明===================//XScuGic Intc; //中断控制器驱动实例

XAxiDma AxiDma; //AXI DMA驱动实例volatile int RxDone; //接收完成标志

volatile int TxDone; //发送完成标志

volatile int Error; //传输出错标志

u8 *TxBufferPtr = (u8 *)TX_BUFFER_BASE; //定义指针并指向发送缓冲区

u8 *RxBufferPtr = (u8 *)RX_BUFFER_BASE; //定义指针并指向接收缓冲区void Trans_Test(); //数据传输测试

void Test_Check(); //传输测试检查

void AXI_DMA_Init(); //AXI DMA初始化

void Tx_IntrHandler(void *Callback); //中断函数(mm2s_introut)

void Rx_IntrHandler(void *Callback); //中断函数(s2mm_introut)

void Set_Intr_Sys(XScuGic *GicInstPtr,XAxiDma * AxiDmaPtr, u16 TxIntrId, u16 RxIntrId); //建立中断系统//=====================主函数======================//

int main()

{xil_printf("AXI_DMA Loop Test \r\n");//AXI_DMA初始化AXI_DMA_Init();//建立中断系统Set_Intr_Sys(&Intc, &AxiDma, TX_INTR_ID, RX_INTR_ID);//进行数据传输测试Trans_Test();return 0;

}//==================传输数据测试==================//

void Trans_Test()

{TxDone = 0;RxDone = 0;Error = 0;//初始化发送缓冲区数据(每次递增1)u8 value = 0x0;for (int i=0; i<MAX_PKT_LEN; i++){TxBufferPtr[i] = value; //写入数据(TxBufferPtr[i] 指针偏移计算:等价于 *(TxBufferPtr+i),按 1字节步长计算地址)value = (value + 1) & 0xFF; //取低8位(1字节)}//刷新 Data Cache(将指定内存区域数据从 CPU数据缓存 Data Cache刷入主存 DDR,确保 DMA或外设访问的是最新数据)Xil_DCacheFlushRange((UINTPTR)TxBufferPtr, MAX_PKT_LEN);Xil_DCacheFlushRange((UINTPTR)RxBufferPtr, MAX_PKT_LEN);//简单模式下DMA数据传输(DMA指针, 起始地址, 数据长度, 传输方向)//DMA将数据从DDR搬运到外设XAxiDma_SimpleTransfer(&AxiDma, (UINTPTR) TxBufferPtr, MAX_PKT_LEN, XAXIDMA_DMA_TO_DEVICE);//等待 DMA 搬运完从 DDR3 到 AXI Stream Data FIFO 的数据while(!TxDone && !Error) //等待至发送结束(或传输出错)if(Error){xil_printf("Tx Error!!\r\n");return;}//DMA将数据从外设搬运到DDRXAxiDma_SimpleTransfer(&AxiDma, (UINTPTR) RxBufferPtr, MAX_PKT_LEN, XAXIDMA_DEVICE_TO_DMA);//等待 DMA 搬运完从 AXI Stream Data FIFO 到 DDR3 的数据while(!RxDone && !Error)//等待至接收结束(或传输出错)if(Error){xil_printf("Rx Error!!\r\n");return;}//测试数据检查Test_Check();

}//==================传输测试检查==================//

void Test_Check()

{int check_error = 0;int Tx,Rx;//比较两个缓冲区数据(全部相同时测试成功)for (int i=0; i<MAX_PKT_LEN; i++){Tx = TxBufferPtr[i];Rx = RxBufferPtr[i];xil_printf("Tx: %x Rx: %x \r\n", Tx, Rx);if(Tx != Rx)check_error = 1;}if(check_error)xil_printf("AXI_DMA Test Failed!!");elsexil_printf("AXI_DMA Test Passed!!");

}//==================AXI DMA初始化==================//

void AXI_DMA_Init()

{//根据DMA器件ID查找配置信息,初始化DMAXAxiDma_Config *Config;Config = XAxiDma_LookupConfig(AXI_DMA_ID);int state = XAxiDma_CfgInitialize(&AxiDma, Config);if(state != XST_SUCCESS) {xil_printf("Failed to Initial AXI_DMA\r\n");}//(可选)检查DMA配置模式if(!XAxiDma_HasSg(&AxiDma)){ xil_printf("AXI_DMA configured as Simple mode\r\n"); }

}//===========中断处理函数(s2mm_introut)===========//

void Tx_IntrHandler(void *Callback)

{u32 IrqStatus;int TimeOut;XAxiDma *AxiDmaInst = (XAxiDma *)Callback;//获取中断状态IrqStatus = XAxiDma_IntrGetIrq(AxiDmaInst, XAXIDMA_DMA_TO_DEVICE);//确定中断类型XAxiDma_IntrAckIrq(AxiDmaInst, IrqStatus, XAXIDMA_DMA_TO_DEVICE);//中断为传输出错if ((IrqStatus & XAXIDMA_IRQ_ERROR_MASK)) {//传输出错标志位置1Error = 1;//持续范围直到DMA复位结束XAxiDma_Reset(AxiDmaInst);TimeOut = RESET_TIMEOUT_COUNTER;while (TimeOut) {if(XAxiDma_ResetIsDone(AxiDmaInst)) {break;}TimeOut -= 1;}}//中断为传输完成if ((IrqStatus & XAXIDMA_IRQ_IOC_MASK))TxDone = 1;//接收完成标志位置1

}//===========中断处理函数(mm2s_introut)===========//

void Rx_IntrHandler(void *Callback)

{u32 IrqStatus;int TimeOut;XAxiDma *AxiDmaInst = (XAxiDma *)Callback;//获取中断状态IrqStatus = XAxiDma_IntrGetIrq(AxiDmaInst, XAXIDMA_DEVICE_TO_DMA);//确定中断类型XAxiDma_IntrAckIrq(AxiDmaInst, IrqStatus, XAXIDMA_DEVICE_TO_DMA);//中断为传输出错if ((IrqStatus & XAXIDMA_IRQ_ERROR_MASK)) {//传输出错标志位置1Error = 1;//持续范围直到DMA复位结束XAxiDma_Reset(AxiDmaInst);TimeOut = RESET_TIMEOUT_COUNTER;while (TimeOut) {if(XAxiDma_ResetIsDone(AxiDmaInst)) {break;}TimeOut -= 1;}}//中断为传输完成if ((IrqStatus & XAXIDMA_IRQ_IOC_MASK))RxDone = 1;//接收完成标志位置1

}//===================建立中断系统==================//

/* 建立 AXI DMA中断系统,* @param GicInstPtr 是指向 XScuGic 驱动实例的指针* @param AxiDmaPtr 是指向 AXI DMA 实例的指针* @param TxIntrId 是 DMA:mm2s_introut中断ID* @param RxIntrId 是 DMA:s2mm_introut中断ID*/

void Set_Intr_Sys(XScuGic *GicInstPtr,XAxiDma * AxiDmaPtr, u16 TxIntrId, u16 RxIntrId)

{//根据中断控制器ID,查找GIC配置信息XScuGic_Config * IntcConfig;IntcConfig = XScuGic_LookupConfig(INTC_DEVICE_ID);//初始化中断控制器驱动XScuGic_CfgInitialize(GicInstPtr, IntcConfig, IntcConfig->CpuBaseAddress);//设置并打开中断异常处理功能Xil_ExceptionInit();Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,(Xil_ExceptionHandler)XScuGic_InterruptHandler,GicInstPtr);//为DMA:mm2s_introut、s2mm_introut中断设置中断处理函数XScuGic_Connect(GicInstPtr, TxIntrId,(Xil_ExceptionHandler)Tx_IntrHandler, AxiDmaPtr);XScuGic_Connect(GicInstPtr, RxIntrId,(Xil_ExceptionHandler)Rx_IntrHandler, AxiDmaPtr);//设置中断优先级、触发类型(优先级从最高0开始步长8最大为248,0xA0=160优先级中等;触发类型:上升沿)XScuGic_SetPriorityTriggerType(GicInstPtr, TxIntrId, 0xA0, 0x3);XScuGic_SetPriorityTriggerType(GicInstPtr, RxIntrId, 0xA0, 0x3);//使能处理器中断Xil_ExceptionEnable();//使能来自于AXI DMA器件的两个中断XScuGic_Enable(GicInstPtr, TxIntrId);XScuGic_Enable(GicInstPtr, RxIntrId);//使能DMA mm2s_introut、s2mm_introut 所有中断(传输完成、出错...)XAxiDma_IntrEnable(AxiDmaPtr, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DMA_TO_DEVICE);XAxiDma_IntrEnable(AxiDmaPtr, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DEVICE_TO_DMA);

}四、效果

下载后,可以看到打印出了“AXI_DMA configured as Simple mode”,说明AXI DMA是以简单DMA的模型运行的。后面立刻开始打印数据,可以看到发送和接收的数据是一样的,最后也答应出了“AXI_DMA Test Passed!!”,说明测试通过。

放在最后:

当然除了用 AXI Sream Data FIFO 模拟一个带 Stream 流接口的外设之外,要实现 DMA 数据回环,也可以直接将 AXI DMA 的 的 S2MM 方向的Stream流接口直接接到MM2S 方向的Stream流接口。当 DMA 接收完自己发出的 Stream 流数据后,s2mm_introut 会产生一个接收完成的中断,此时PS端就可以将数据写回DDR了。

相关文章:

:AXI DMA 环路测试)

ZYNQB笔记(十六):AXI DMA 环路测试

版本:Vivado2020.2(Vitis) 任务:使用 PL 端的 AXI DMA IP 核实现对 DDR3 中数据的读取与写入,实现数据环回,具体流程为: PS 端产生测试数据并写入到 DDR3 中,然后 PL 端的 AXI DMA I…...

Java学习手册:Spring 数据访问

一、Spring JDBC JdbcTemplate :Spring JDBC 提供了 JdbcTemplate 类,它简化了数据库操作,提供了丰富的 API 来执行数据库访问任务。JdbcTemplate 可以自动处理数据库连接的获取、释放,SQL 语句的执行,结果集的处理等…...

)

第二章 日志分析-apache日志分析(玄机系列)

简介 账号密码 root apacherizhi ssh rootIP 1、提交当天访问次数最多的IP,即黑客IP: 2、黑客使用的浏览器指纹是什么,提交指纹的md5: 3、查看包含index.php页面被访问的次数,提交次数: 4、查看黑客IP访问了…...

类比分析AI Agent 技术

引言:AI Agent 的本质与范式转变 在人工智能领域,AI Agent(智能体)代表了一种从传统软件系统到自主性实体的深刻范式转变。不同于仅仅执行预设指令或算法的程序,现代 AI Agent 被设计为能够: 感知 (Perce…...

【业务领域】PCIE协议理解

PCIE协议理解 提示:这里可以添加系列文章的所有文章的目录,目录需要自己手动添加 PCIE学习理解。 文章目录 PCIE协议理解[TOC](文章目录) 前言零、PCIE掌握点?一、PCIE是什么?二、PCIE协议总结物理层切速 链路层事务层6.2 TLP的路…...

组合模式)

设计模式简述(十四)组合模式

组合模式 描述基本使用所有节点方法一致使用 叶子无实现子节点使用 添加向上查询使用(没变化) 描述 组合模式用于描述部分与整体的关系,将个体对象与组合对象的行为统一,便于维护整个数据集。 基本使用 所有节点方法一致 定义…...

【Tool】vscode

vscode问题集锦 1 全局搜索失效 ctrl shift f 快捷键失效: 原因:可能与输入法快捷键冲突,重定义输入法快捷键即可 其他 看心情和经历补充~...

文件操作--文件包含漏洞

本文主要内容 脚本 ASP、PHP、JSP、ASPX、Python、Javaweb --# 各种包含函数 检测 白盒 代码审计 黑盒 漏扫工具、公开漏洞、手工看参数值及功能点 类型 本地包含 有限制、无限制 远程包含 无限制、有限制…...

(文末有下载方式))

数字智慧方案6156丨智慧医联体信息化解决方案(50页PPT)(文末有下载方式)

资料解读:智慧医联体信息化解决方案 详细资料请看本解读文章的最后内容。 在医疗改革不断深化的大背景下,医联体信息化建设成为推动医疗服务高质量发展的关键力量。《智慧医联体信息化解决方案》这份资料,全面且深入地阐述了医联体信息化建…...

华为eNSP:多区域集成IS-IS

一、什么是多区域集成IS-IS? 多区域集成IS-IS是一种基于中间系统到中间系统(IS-IS)协议优化的网络架构设计,通过多区域协同、路径优化和扩展性增强实现高效路由管理,其核心特征如下: 1、分布式架构与多区…...

:检索增强生成原理与LLM对比分析)

RAG技术完全指南(一):检索增强生成原理与LLM对比分析

RAG技术完全指南(一):检索增强生成原理与LLM对比分析 文章目录 RAG技术完全指南(一):检索增强生成原理与LLM对比分析1. RAG 简介2. 核心思想3. 工作流程3.1 数据预处理(索引构建)3.2…...

Ubuntu搭建LNMP(Linux + Nginx + MySQL + PHP)环境)

(持续更新)Ubuntu搭建LNMP(Linux + Nginx + MySQL + PHP)环境

LNMP(Linux Nginx MySQL PHP)环境是在Linux操作系统上构建的一个高性能Web服务器环境。M也可以指代其他数据库,P也可以指代Python 1. 准备Linux系统 确保你已经在一台服务器或虚拟机上安装了Linux操作系统。推荐使用Ubuntu、CentOS或Debi…...

)

机器人手臂控制器:EMC电磁兼容解决(一)

一、机器人手臂控制器行业标准剖析 GB/T 39004—2020《工业机器人电磁兼容设计规范》 GB/T 37283-2019 服务机器人 电磁兼容 通用标准 抗扰度要求和限值 GB/T 39785-2021 服务机器人 机械安全评估与测试方法 GB/T 40014-2021 双臂工业机器人 性能及其试验方法 GB/T 40013-…...

Qt进阶开发:QSS常用的语法介绍和使用

文章目录 一、什么是QSS?二、QSS的基本语法三、QSS 的使用方式3.1 在代码中设置 QSS3.2 加载外部 QSS 文件四、QSS中选择器的介绍和使用4.1 Type Selector(类型选择器)4.2 ID Selector(ID 选择器)4.2.1 仅使用 ID(常见写法)4.2. 2 类型 + ID(更精确匹配)4.3 Class Sel…...

qemu学习笔记:QOM

2.4 QOM介绍 说明:小白学习qemu的一些学习笔记。主要是学习《QEMU&KVM源码解析与应用》这本书。 参考: 《QEMU&KVM源码解析与应用》作者:李强 Qemu - 百问网嵌入式Linux wiki QOM 定义:QEMU Object Model,是 Q…...

)

Spring AI开发跃迁指南(第二章:急速上手3——Advisor核心原理、源码讲解及使用实例)

1.Advisor简介 Spring AI 中的 Advisor 是一种核心机制,用于拦截和增强 AI 应用程序中的请求与响应流。其设计灵感来源于 Spring AOP(面向切面编程)中的切面(Aspect)概念,但专门针对 AI 交互场景进行了优化…...

51c嵌入式~单片机~合集9

我自己的原文哦~ https://blog.51cto.com/whaosoft/13884964 一、单片机中hex、bin文件的区别 单片机程序编译之后,除了生成hex文件之外还生成了bin文件,实际它们都是单片机的下载文件,下文介绍它们的区别。 Hex Hex文件包含地址信息。…...

linux学习——数据库API创建

一.API操作 1.int sqlite3_open(char *filename,sqlite3 **db) 功能:打开sqlite数据库 参数: filename:数据库文件路径 db:指向sqlite句柄的指针 (splite3* db;) 返回值…...

_csdn)

21.2Linux中的LCD驱动实验(驱动)_csdn

1、修改设备树 1.1、LCD 屏幕使用的 IO 配置 编译: make uImage LOADADDR0XC2000040 -j8 //编译内核复制给内核的镜像路径:1.2、LDTC 接口节点修改 1.3、输出接口的编写 2、在 panel-simple.c 文件里面添加屏幕参数 显示波浪线是因为alientek_desc 保存参…...

如何设计一个支持多语言的Dubbo服务?)

Dubbo(89)如何设计一个支持多语言的Dubbo服务?

设计一个支持多语言的Dubbo服务需要考虑以下几个方面: 服务接口设计:确保服务接口的定义可以被不同语言实现。序列化协议:选择一个支持多语言的序列化协议,例如Protobuf、Thrift、gRPC等。服务注册与发现:确保服务注册…...

油气地震资料数据中“照明”的含义

油气地震资料数据中“照明”的含义 在地震勘探中,“照明”(Illumination)是一个比喻性术语,用于描述地下地质构造被地震波能量覆盖的程度。其核心含义包括: 能量覆盖:指地震波(如人工激发的地…...

[FPGA Video IP] Frame Buffer Read and Write

Xilinx Video Frame Buffer Read and Write IP (PG278) 详细介绍 概述 Xilinx LogiCORE™ IP Video Frame Buffer Read(帧缓冲读取)和 Video Frame Buffer Write(帧缓冲写入)核(PG278)是一对专为视频处理…...

(文末有下载方式))

新能源行业供应链规划及集成计划报告(95页PPT)(文末有下载方式)

资料解读:《数字化供应链规划及集成计划现状评估报告》 详细资料请看本解读文章的最后内容。 该报告围绕新能源行业 XX 企业供应链展开,全面评估其现状,剖析存在的问题,并提出改进方向和关键举措,旨在提升供应链竞争力…...

curl详解

curl 是一个常用的命令行工具,用于发送 HTTP 请求,支持包括 GET、POST、PUT、DELETE 等在内的多种 HTTP 方法。它非常适合用来测试 API、下载文件、与后端服务进行交互等。接下来,我会详细讲解 curl 的基本用法以及常见的应用场景。 &#x…...

博客打卡-人类基因序列功能问题动态规划

题目如下: 众所周知,人类基因可以被认为是由4个核苷酸组成的序列,它们简单的由四个字母A、C、G和T表示。生物学家一直对识别人类基因和确定其功能感兴趣,因为这些可以用于诊断人类疾病和设计新药物。 生物学家确定新基因序列功能…...

Runnable组件动态添加默认调用参数

01. bind 函数用途与使用技巧 在使用 LangChain 开发时,某些场景我们希望在一个 Runnable 队列中调用另一个 Runnable 并传递常量参数,这些参数既非前序 Runnable 的输出,也不是用户输入,而是组件自身的部分参数。此时可以使用 R…...

系统架构设计师:设计模式概述

面向对象技术为软件技术带来新的发展。人们运用面向对象的思想分析系统、为系统建模并设计系统,最后使用面向对象的程序语言来实现系统。 但是面向对象的设计并不是一件很简单的事情,尤其是要设计出架构良好的软件系统更不容易。 为了提高系统的复用性…...

)

天山流域流量数据集(1991-2019)

时间分辨率日空间分辨率/共享方式开放获取数据大小131.67 MB数据时间范围 1901-01-01 — 2019-12-31 元数据更新时间2025-03-24 数据集摘要 由于天山地区数据稀缺和水文条件复杂,中亚水塔的自然径流数据集在各种全球径流数据集(如GMIS、GRDC)…...

Linux 环境下 Mysql 5.7 数据定期备份

目录 一、创建数据备份脚本二、查看备份日志三、数据库数据恢复 备份策略: 系统环境 openEuler 22.03 (LTS-SP4) 单机备份 每天凌晨2点,指定数据库表全量备份,只保留近7次备份数据 每次的脚本执行,将会记录执行结果到日志…...

)

多模态大语言模型arxiv论文略读(五十二)

M3D: Advancing 3D Medical Image Analysis with Multi-Modal Large Language Models ➡️ 论文标题:M3D: Advancing 3D Medical Image Analysis with Multi-Modal Large Language Models ➡️ 论文作者:Fan Bai, Yuxin Du, Tiejun Huang, Max Q. -H. M…...

REST API、FastAPI与Flask API的对比分析

以下是关于REST API、FastAPI与Flask API的对比分析,涵盖架构设计、性能表现、开发效率等核心维度: 一、核心定位与架构差异 REST API 本质:一种基于HTTP协议的架构风格,强调资源化操作(通过URI定位资源)、…...

【论文阅读26】贝叶斯-滑坡预测-不确定性

📖 这篇论文主要说了什么? 📌 背景: 滑坡预测里,预测失稳时间(Slope Failure Time, SFT) 很关键,但它受两方面不确定性影响: 观测不确定性(监测数据本身的…...

【笔记】深度学习模型训练的 GPU 内存优化之旅④:内存交换与重计算的联合优化篇

开设此专题,目的一是梳理文献,目的二是分享知识。因为笔者读研期间的研究方向是单卡上的显存优化,所以最初思考的专题名称是“显存突围:深度学习模型训练的 GPU 内存优化之旅”,英文缩写是 “MLSys_GPU_Memory_Opt”。…...

边缘计算革命:大模型轻量化部署全栈实战指南

当ResNet-152模型能在树莓派4B上实现每秒27帧实时推理时,边缘智能时代真正到来。本文解析从模型压缩到硬件加速的完整技术栈,实测Transformer类模型在移动端的部署时延可压缩至16ms,揭示ARM芯片实现INT4量化的工程秘诀与十种典型场景优化方案…...

LangChain4j +DeepSeek大模型应用开发——7 项目实战 创建硅谷小鹿

这部分我们实现硅谷小鹿的基本聊天功能,包含聊天记忆、聊天记忆持久化、提示词 1. 创建硅谷小鹿 创建XiaoLuAgent package com.ai.langchain4j.assistant;import dev.langchain4j.service.*; import dev.langchain4j.service.spring.AiService;import static dev…...

python自动化测试

Python自动化测试指南 Python是自动化测试领域的首选语言之一,凭借其简洁的语法、丰富的库和强大的生态系统,能够高效地实现各种测试需求。本文将详细介绍Python在自动化测试中的应用,涵盖Web测试、API测试、单元测试、GUI测试等多个方面。 1. 自动化测试基础 测试金字塔…...

49、【OS】【Nuttx】【OSTest】参数解析:测试项

背景 接之前 blog 48、【OS】【Nuttx】【OSTest】内存监控:分配释放推演 解析完内存监控,继续看下一个测试项 getopt_test 测试项 getopt_test 如下 getopt,getopt_long,getopt_long_only getopt() 用来解析命令行短选项&am…...

String StringBuilder StringBuffer

文章目录 StringStringBuilderStringBuffer StringStringBuilderStringBuffer可变性不可变可变可变线程安全安全(天然不可变)不安全安全(同步方法)性能低(频繁操作生成新对象)高中(同步开销&…...

[FPGA 官方 IP] Binary Counter

Xilinx Binary Counter IP (PG121) 详细介绍 概述 Xilinx Binary Counter IP(二进制计数器 IP)是 AMD Xilinx 提供的 LogiCORE™ IP 核,用于在 FPGA 中实现高性能、面积高效的二进制计数器。该 IP 核支持上行计数器、下行计数器以及上/下计…...

【大模型实战篇】华为信创环境采用vllm部署QwQ-32B模型

1. 背景 本文分享在华为昇腾机器上部署QwQ-32B模型的实践。 首先华为自己是提供了一套在信创机器(NPU)上部署模型的方案【1】,但是部署之后,测试发现会有输出截断的现象。QwQ-32B本身是支持128k的最大上下文长度,定位…...

优雅关闭服务:深入理解 SIGINT / SIGTERM 信号处理机制

目录 为什么需要优雅关闭? 什么是 SIGINT 和 SIGTERM? 如何实现优雅关闭(以 C 为例) 示例代码(gRPC 服务 Boost 信号监听): 优雅关闭时的清理内容通常包括: 与 SIGKILL 的区别…...

2025五一杯数学建模竞赛选题建议+初步分析

完整内容请看文章最下面的推广群 2025五一杯数学建模竞赛选题建议初步分析 提示:C君认为的难度和开放度评级如下: 难度:B题 > A题 > C题,开放度:B题 > C题 > A题。综合来看:A题目标明确,数据…...

自动剪辑批量混剪视频过原创软件工具视频帧级处理技术实践批量截图解析

一、引言:视频素材精细化处理的技术需求 在视频内容生产与分析场景中,高效的帧级处理是素材解构的核心环节。本文结合实战经验,解析基于智能帧截取算法、参数化配置系统、多线程并行处理的批量帧处理技术方案,构建可复用的工程化…...

HC-SR04超声波模块测距实战含源码)

GD32F407单片机开发入门(二十五)HC-SR04超声波模块测距实战含源码

文章目录 一.概要二.HC-SR04主要参数1.模块引脚定义2.模块电气参数3.模块通讯时序4.模块原理图 三.GD32单片机超声波模块测距实验四.工程源代码下载五.小结 一.概要 HC-SR04超声波模块常用于机器人避障、物体测距、液位检测、公共安防、停车场检测等场所。HC-SR04超声波模块主…...

C++11新特性_Lambda 表达式

Lambda 表达式是 C11 引入的一项重要特性,它允许你在代码中创建匿名函数对象。Lambda 表达式为编写简洁、灵活的代码提供了便利,尤其适用于函数式编程和需要传递简短回调函数的场景。下面从基本语法、捕获列表、使用场景等方面详细介绍 Lambda 表达式。 …...

vue中$set原理

Vue 中的 $set 方法(Vue.set)主要用于 向响应式对象中添加一个新的属性,并确保这个新属性是响应式的,能够触发视图更新。 📌 背景问题:为什么需要 $set? 在 Vue 2 中,直接给对象新增…...

【C++重载操作符与转换】输入和输出操作符

目录 一、输入输出操作符概述 二、输入输出操作符重载的原理 2.1 为什么需要重载? 2.2 重载的限制 2.3 重载的方式 三、输入输出操作符重载的实现 3.1 输出操作符 << 的重载 3.2 输入操作符 >> 的重载 四、输入输出操作符重载的注意事项 4.1 …...

Vue 生命周期全解析:理解组件从创建到销毁的全过程

Vue 生命周期全解析:理解组件从创建到销毁的全过程 Vue.js 是一个流行的前端框架,它通过“组件化开发”提升了代码组织效率。要真正掌握 Vue,生命周期(Lifecycle) 是一个必须深入理解的核心概念。生命周期不仅决定了组…...

MySQL零基础入门:Ubuntu环境安装与操作精解

知识点1【数据库】 数据的存储方式,我们之前学的,从变量,数组,链表,最后到文件,文件之上,便是数据库,而我们要介绍的MySQL就是数据库的关系数据库中的其中一种。 1、数据库 本质&…...

【计算机视觉】语义分割:Mask2Former:统一分割框架的技术突破与实战指南

深度解析Mask2Former:统一分割框架的技术突破与实战指南 技术架构与创新设计核心设计理念关键技术组件 环境配置与安装指南硬件要求安装步骤预训练模型下载 实战全流程解析1. 数据准备2. 配置文件定制3. 训练流程4. 推理与可视化 核心技术深度解析1. 掩膜注意力机制…...