[FPGA]设计一个DDS信号发生器

一、DDS

DDS(Data Distribution Service) 是一种面向实时分布式系统的通信中间件标准,专为高性能、高可靠性、低延迟的数据传输场景设计。它由对象管理组织(OMG) 制定并维护,广泛应用于物联网(IoT)、工业自动化、航空航天、自动驾驶、医疗设备等领域。

(一).核心特点

-

发布-订阅模型(Pub/Sub)

数据生产者(发布者)和消费者(订阅者)通过主题(Topic)进行通信,实现松耦合的分布式架构,无需直接依赖对方地址或接口。 -

服务质量(QoS, Quality of Service)

DDS 提供丰富的 QoS 策略(如可靠性、持久性、时效性、优先级等),允许开发者根据场景需求(如实时性、容错性)灵活配置数据传输行为。 -

实时性与低延迟

针对关键任务场景(如自动驾驶、机器人控制),DDS 支持微秒级延迟和确定性响应,确保数据高效传输。 -

去中心化架构

无单点故障,节点间直接通信(P2P),适合高可靠、高扩展性的分布式系统。 -

跨平台与标准化

支持多种操作系统(Linux、Windows、嵌入式 RTOS)和编程语言(C/C++、Java、Python等),遵循 DDSI-RTPS 协议保障互操作性。

(二).典型应用场景

-

工业物联网(IIoT):工厂设备实时监控与协同控制。

-

自动驾驶:车辆传感器、决策系统间高速数据共享。

-

航空航天:飞行器子系统(导航、通信)的可靠数据交换。

-

医疗设备:手术机器人、监护仪等实时数据同步。

-

智能交通:交通信号、车辆与云端系统的动态协调。

(三).技术优势

-

可靠性:通过 QoS 确保关键数据不丢失(如“可靠传输”模式)。

-

灵活性:动态发现节点,支持系统动态扩展。

-

安全性:支持数据加密、身份认证等安全机制(DDS Security 标准)。

-

高效性:零拷贝传输、多播通信优化网络带宽。

(四).主流实现

-

OpenDDS(开源)

-

RTI Connext DDS(商业级,广泛应用在关键领域)

-

Eclipse Cyclone DDS(开源,被 ROS 2 采用)

二、FPGA存储器

FPGA存储器 是FPGA(现场可编程门阵列)中用于数据存储的关键资源,通常分为内部存储器和外部存储器接口两类。FPGA的灵活性和可编程性使其在存储管理方面具有独特的优势,广泛应用于高速缓存、数据缓冲、状态机存储等场景。以下是关于FPGA存储器的详细介绍:

(一)FPGA内部存储器

FPGA芯片内部集成了多种专用存储资源,支持高速、低延迟的片上数据存储。主要类型包括:

1. 分布式RAM(Distributed RAM)

-

结构:由FPGA逻辑单元(LUT,查找表)配置而成,利用逻辑资源实现小容量存储。

-

特点:

-

容量小(通常几十到几百比特),但分布灵活,适合分散存储。

-

支持单端口或简单双端口读写。

-

读写延迟低(1~2个时钟周期)。

-

-

典型应用:状态机、小型查找表(LUT)、系数存储(如滤波器参数)。

2. Block RAM(BRAM)

-

结构:FPGA内部专用的块存储器,每个BRAM容量较大(如Xilinx UltraScale+的36Kb/块)。

-

特点:

-

大容量、高密度存储,可级联实现更大容量。

-

支持多种配置模式(单端口、双端口、真双端口)。

-

支持同步读写,带宽高(例如72位宽)。

-

独立于逻辑资源,不占用LUT。

-

-

典型应用:数据缓存(如图像帧缓冲)、FIFO、大规模查找表。

3. UltraRAM(URAM)

-

结构:某些高端FPGA(如Xilinx UltraScale+)中的超大容量存储块。

-

特点:

-

单块容量可达288Kb,适合超大规模数据存储。

-

低功耗、高带宽,支持复杂存储需求。

-

-

典型应用:深度学习加速器权重存储、大规模数据库缓存。

4. 寄存器(Register)

-

结构:FPGA逻辑单元中的触发器(Flip-Flop),用于存储1位数据。

-

特点:

-

超低延迟(单周期访问),但资源有限。

-

适合存储控制信号、计数器、状态位。

-

-

典型应用:流水线寄存器、状态机状态存储。

(二)FPGA外部存储器接口

当片上存储资源不足时,FPGA可通过高速接口连接外部存储器,常见类型包括:

1. DDR SDRAM(如DDR4、LPDDR4)

-

特点:

-

大容量(GB级)、高带宽(数十GB/s)。

-

需通过FPGA的硬核存储器控制器或软核IP实现接口。

-

-

应用:视频帧缓存、大数据处理。

2. SRAM

-

特点:

-

高速、低延迟,但容量较小(MB级)。

-

接口简单,无需复杂控制器。

-

-

应用:高速数据采集、实时信号处理。

3. Flash存储器

-

特点:

-

非易失性存储,适合配置存储或启动代码。

-

读写速度较慢,但容量大。

-

-

应用:FPGA配置文件的存储、系统启动引导。

4. QSPI Flash

-

特点:

-

低引脚数、低成本,用于小容量非易失存储。

-

通常用于存储FPGA的比特流(Bitstream)。

-

-

应用:嵌入式系统启动配置。

三、FPGA存储器的设计要点

-

资源分配优化:

-

根据需求选择分布式RAM、BRAM或URAM,平衡速度和资源占用。

-

例如,小容量频繁访问的数据用分布式RAM,大块数据用BRAM。

-

-

时序约束:

-

外部存储器接口需严格满足时序(如DDR的建立/保持时间)。

-

使用FPGA工具的时序分析工具(如Vivado的Timing Report)进行验证。

-

-

带宽与延迟权衡:

-

片上存储器(BRAM)延迟低但容量小,外部存储器容量大但延迟高。

-

可通过缓存(Cache)或预取(Prefetch)策略优化性能。

-

-

存储器安全:

-

对敏感数据(如加密密钥)启用ECC(纠错码)或物理保护机制。

-

(一)、ROM波形存储器的设计步骤

ROM波形存储器 是一种利用只读存储器(ROM) 预存周期性或非周期性波形数据(如正弦波、方波、三角波等)的硬件设计,广泛应用于数字信号合成、通信调制解调、音频生成等领域。

1、调用IP

(1)创建文件

我们单独创建一个ROM文件来熟悉ROM调用IP,我们在Quartus中创建一个新项目命名为ROM。

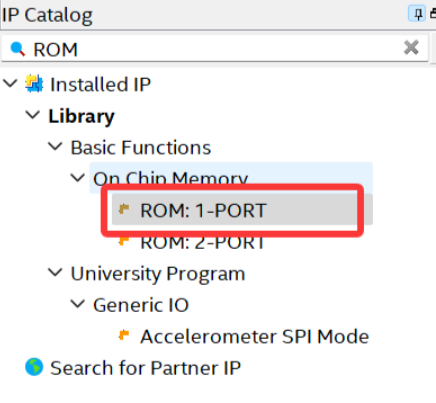

(2)调用IP

在左侧的IP Catalog搜索栏搜索“ROM”,然后选择“ROM:1-PORT”。

接下来在最开始我们创建的文件夹中添加一个名为IP的文件夹,随后我们将把IP文件保存在其中。

(3)配置IP

第一部分是IP核的输出数据位宽以及IP核的存储容量

第二部分是存储单元类型,默认即可

第三部分是选择时钟模式,单时钟或者双时钟,我们这里选择的是单时钟。

随后点击next。

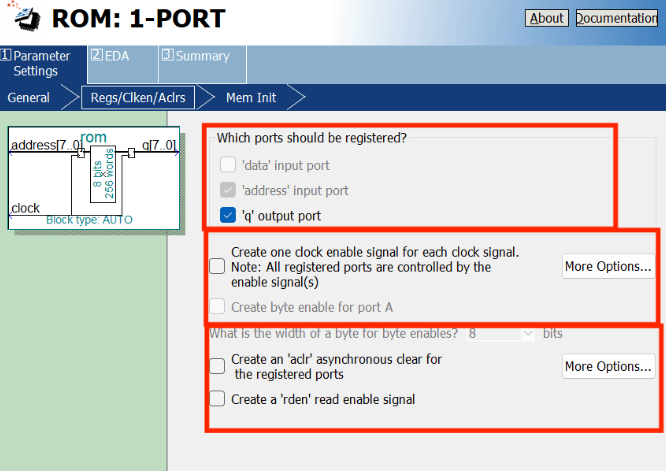

接着

选择输出端口Q是否寄存。

时钟使能信号,通常默认不勾选。

选择是否创建已补复位信号“acir”和读使能信号“rden”。这里两项都不勾选。

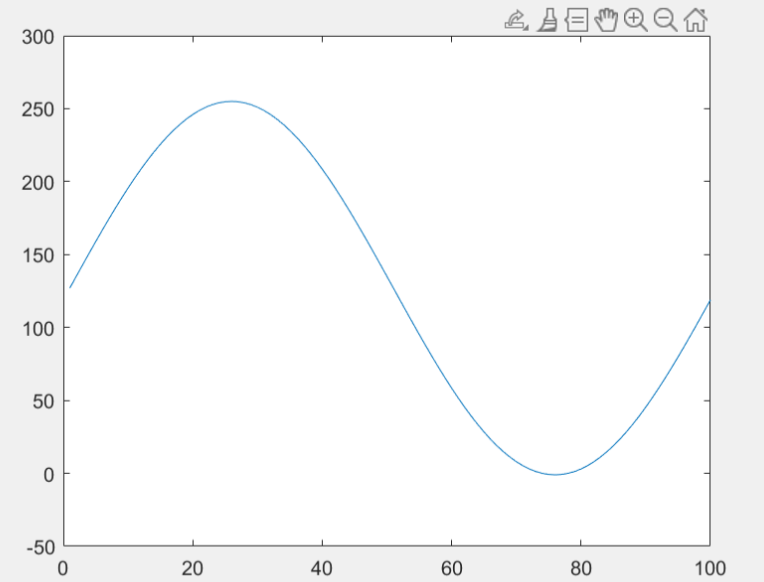

这一步是将生成的MIF文件添加进去。本次采用matlab生成一个FPGA所需要的正弦波MIF文件,sin_wave_8x256.mif会生成在你的资源管理器中,把他添加到你的FPGA工程文件下

MIF文件代码如下,

clc, clear, close all

F1=1; %信号频率

Fs=10^2; %采样频率

P1=0; %信号初始相位

N=10^2; %采样点数

t=[0:1/Fs:(N-1)/Fs]; %采样时刻

ADC=2^7 - 1; %直流分量

A=2^7; %信号幅度

%生成正弦信号

s=A*sin(2*pi*F1*t + pi*P1/180) + ADC;

plot(s); %绘制图形

%创建 coe 文件

fild = fopen('sin_wave_100x8.coe','wt');

%写入 coe 文件头

%固定写法,表示写入的数据是 10 进制表示

fprintf(fild, '%s\n','memory_initialization_radix=10;');

%固定写法,下面开始写入数据

fprintf(fild, '%s\n\n','memory_initialization_vector =');

for i = 1:Ns2(i) = round(s(i)); %对小数四舍五入以取整if s2(i) <0 %负 1 强制置零s2(i) = 0endfprintf(fild, '%d',s2(i)); %数据写入if i==Nfprintf(fild, '%s\n',';'); %最后一个数据用;elsefprintf(fild,',\n'); % 其他数据用,end

end

fclose(fild); % 写完了,关闭文件复卷机: 04-09 16:48:55

% 方波信号波形采集参考代码(square_wave.m):F1 = 1; %信号频率

Fs = 10^2; %采样频率

P1 = 0; %信号初始相位

N = 10^2; %采样点数

t = [0:1/Fs:(N-1)/Fs]; %采样时刻

ADC = 2^7 - 1; %直流分量

A = 2^7; %信号幅度%生成方波信号

s = A*square(2*pi*F1*t + pi*P1/180) + ADC;

plot(s); %绘制图形%创建 coe 文件

fild = fopen('squ_wave_100x8.coe','wt');

%写入 coe 文件头

%固定写法,表示写入的数据是 10 进制表示

fprintf(fild, '%s\n','memory_initialization_radix=10;');

%固定写法,下面开始写入数据

fprintf(fild, '%s\n\n','memory_initialization_vector =');

for i = 1:Ns2(i) = round(s(i)); %对小数四舍五入以取整if s2(i) <0 %负 1 强制置零s2(i) = 0endfprintf(fild, '%d',s2(i)); %数据写入if i==Nfprintf(fild, '%s\n',';'); %最后一个数据用分号elsefprintf(fild,',\n'); % 其他数据用 ,end

end

fclose(fild); % 写完了,关闭文件MATLAB生成的正弦信号波形图如下,

2、代码

(1)单端口ROM

顶层模块rom

module rom

(input wire sys_clk ,input wire sys_rst_n,output wire [7:0] rom_data

);wire [7:0] rom_addr;rom_ctrl rom_ctrl_inst

(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.rom_addr (rom_addr)

);rom_sin rom_sin_inst (.address ( rom_addr ),.clock ( sys_clk ),.q ( rom_data ));endmodulerom_Ctrl模块代码:

module rom_ctrl

(input wire sys_clk ,input wire sys_rst_n ,output reg [7:0] rom_addr

);always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)rom_addr <= 8'd0;elserom_addr <= rom_addr + 1'b1;

endmodule测试代码,

`timescale 1ns/1ns

module tb_rom();reg sys_clk;

reg sys_rst_n;wire rom_data;initialbeginsys_clk = 1'b0;sys_rst_n <= 1'b0;#30sys_rst_n <= 1'b1;endalways #10 sys_clk = ~sys_clk;

rom rom_inst

(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.rom_data (rom_data)

);

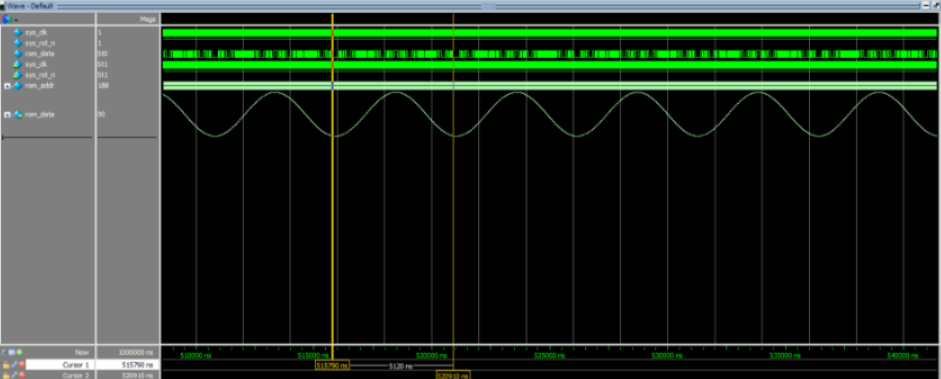

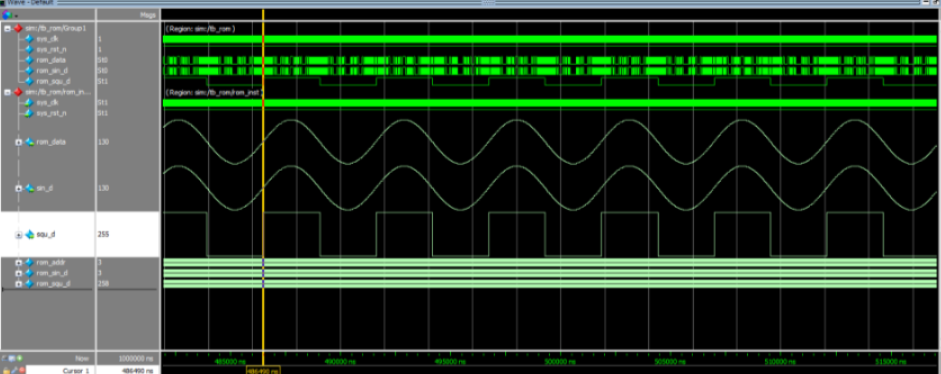

endmodule结果如下

双端口ROM

在原来的基础,采用双端口ROM输出两路信号

MIF文件代码

clc; %清除命令行命令

clear all; %清除工作区变量,释放内存空间

F1=1; %信号频率

Fs=2^8; %采样频率

P1=0; %信号初始相位

N=2^8; %采样点数

t=[0:1/Fs:(N-1)/Fs]; %采样时刻

ADC=2^7 - 1; %直流分量

A=2^7; %信号幅度

s1=A*sin(2*pi*F1*t + pi*P1/180) + ADC; %正弦波信号

s2=A*square(2*pi*F1*t + pi*P1/180) + ADC; %方波信号

%创建mif文件

fild = fopen('wave_512x8.mif','wt');

%写入mif文件头

fprintf(fild, '%s\n','WIDTH=8;'); %位宽

fprintf(fild, '%s\n\n','DEPTH=512;'); %深度

fprintf(fild, '%s\n','ADDRESS_RADIX=UNS;'); %地址格式

fprintf(fild, '%s\n\n','DATA_RADIX=UNS;'); %数据格式

fprintf(fild, '%s\t','CONTENT'); %地址

fprintf(fild, '%s\n','BEGIN'); %开始

for j = 1:2for i = 1:Nif j == 1 %打印正弦信号数据s0(i) = round(s1(i)); %对小数四舍五入以取整fprintf(fild, '\t%g\t',i-1); %地址编码endif j == 2 %打印方波信号数据s0(i) = round(s2(i)); %对小数四舍五入以取整fprintf(fild, '\t%g\t',i-1+N); %地址编码endif s0(i) <0 %负1强制置零s0(i) = 0endfprintf(fild, '%s\t',':'); %冒号fprintf(fild, '%d',s0(i)); %数据写入fprintf(fild, '%s\n',';'); %分号,换行end

end

fprintf(fild, '%s\n','END;'); %结束

fclose(fild);顶层模块rom

module rom

(input wire sys_clk ,input wire sys_rst_n ,output wire [7:0] rom_data ,output wire [7:0] sin_d ,output wire [7:0] squ_d

);wire [7:0] rom_addr;

wire [8:0] rom_sin_d;

wire [8:0] rom_squ_d;rom_ctrl rom_ctrl_inst

(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.rom_addr (rom_addr),.rom_sin_d (rom_sin_d),.rom_squ_d (rom_squ_d)

);rom_double rom_double_inst ( //双端口ROM.address_a ( rom_sin_d ),.address_b ( rom_squ_d ),.clock ( sys_clk ),.q_a ( sin_d ),.q_b ( squ_d ));rom_sin rom_sin_inst (.address ( rom_addr ),.clock ( sys_clk ),.q ( rom_data ));endmodulerom_ctro模块:

module rom_ctrl

(input wire sys_clk ,input wire sys_rst_n ,output reg [7:0] rom_addr ,output reg [8:0] rom_sin_d ,output reg [8:0] rom_squ_d

);localparam SQU_Z = 9'd256;

always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)rom_addr <= 8'd0;else rom_addr <= rom_addr + 1'b1;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)rom_sin_d <= 9'd0;else if(rom_sin_d == 9'd255)rom_sin_d <= 9'd0;elserom_sin_d <= rom_addr + 1'b1;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)rom_squ_d <= SQU_Z;elserom_squ_d <= rom_addr + SQU_Z;endmodule测试代码

`timescale 1ns/1ns

module tb_rom();reg sys_clk;

reg sys_rst_n;wire rom_data;

wire rom_sin_d;

wire rom_squ_d;initialbeginsys_clk = 1'b0;sys_rst_n <= 1'b0;#30sys_rst_n <= 1'b1;endalways #10 sys_clk = ~sys_clk;

rom rom_inst

(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.rom_data (rom_data),.sin_d (rom_sin_d),.squ_d (rom_squ_d)

);

endmodule结果如下:

(二)RAM的设计步骤

1、调用IP

(1)创建文件

我们单独创建一个RAM文件来熟悉RAM调用IP,我们在Quartus中创建一个新项目命名为RAM。

(2)调用IP

在左侧的IP Catalog搜索栏搜索“RAM”,然后选择“RAM:1-PORT”。

接下来在最开始我们创建的文件夹中添加一个名为IP的文件夹,随后我们将把IP文件保存在其中。

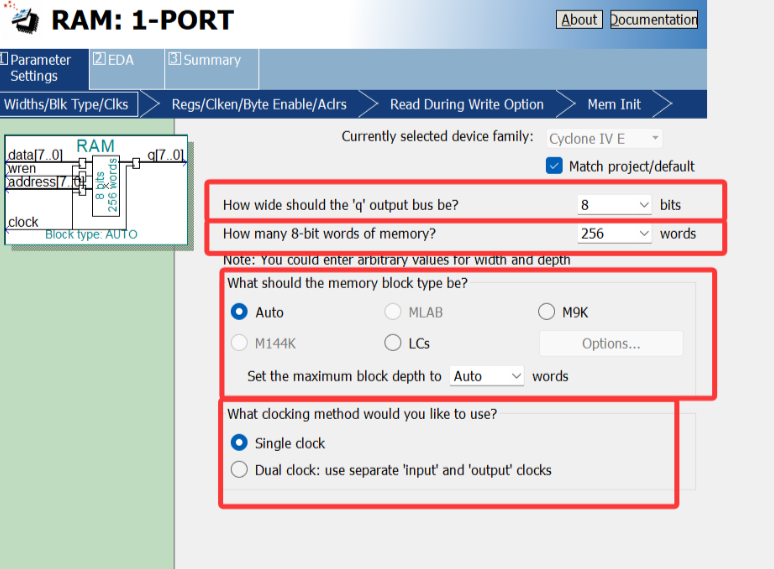

(3)配置IP

第一部分是IP核的输出数据位宽

第二部分是IP核的存储容量

第三部分是存储单元类型,默认即可

第四部分是选择时钟模式,单时钟或者双时钟,我们这里选择的是单时钟。

随后点击next进入下一步配置。

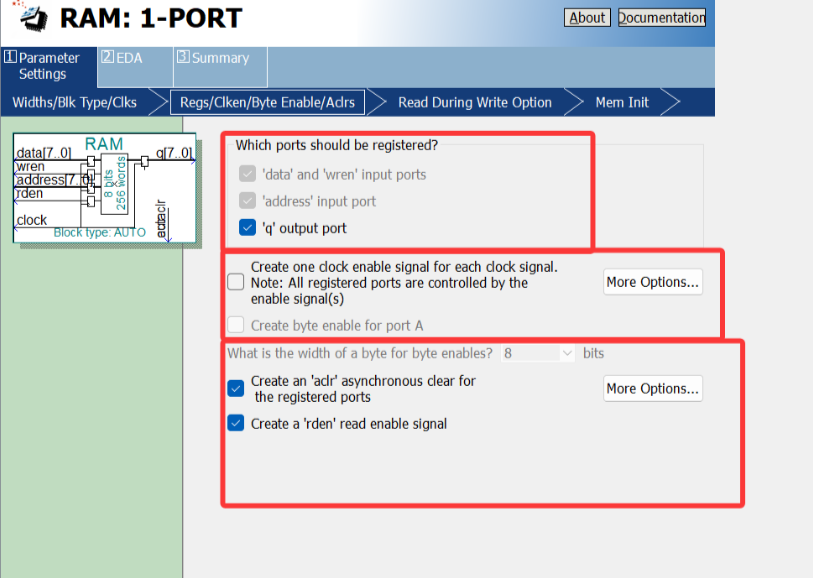

这一步包括以下三个部分

第一部分是选择输出端口Q是否寄存。

第二部分是时钟使能信号,通常默认不勾选。

第三部分是选择是否创建已补复位信号“acir”和读使能信号“rden”。这里两项都勾选。

随后点击next进入下一步配置。

这一步是配置某个地址写入数据的同时读取数据,通常默认“New data”即可,随后点击next进入下一步配置。

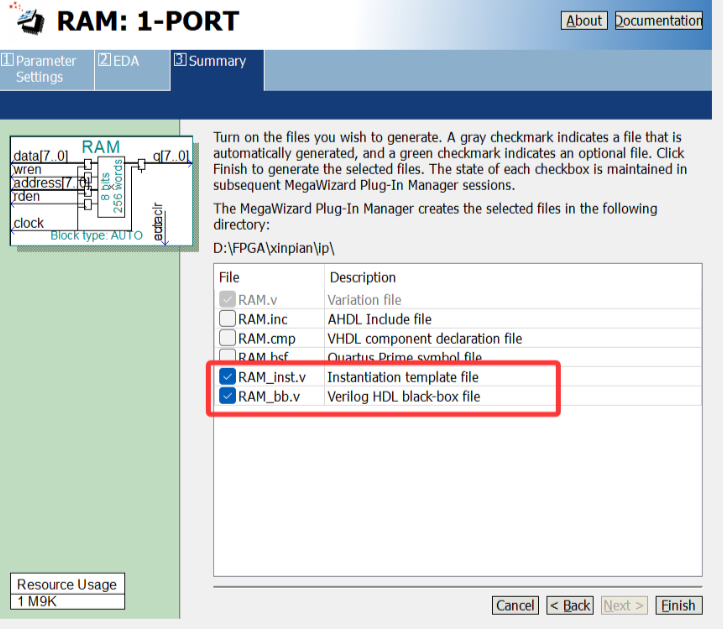

最后一步是将inst文件勾选上点击finish完成配置,随后点击Yes。

.v代码

module ram_ip( input clk ,input rst_n ,input [5:0] address ,input [7:0] data ,input redn ,input wren ,output [7:0] q

);ram ram_inst (.aclr ( ~rst_n ),.address ( address ),.clock ( clk ),.data ( data ),.rden ( rden ),.wren ( wren ),.q ( q ));endmodule测试代码

`timescale 1ns/1nsmodule tb_ram();

reg tb_clk ;

reg tb_rst_n ;

reg [5:0] address ;

reg [7:0] data ;

reg rden ;

reg wren ;

wire [7:0] q ;parameter CYCLE = 20;ram_ip ram_ip_inst( /*input */.clk ( tb_clk ) ,/*input */.rst_n ( tb_rst_n ) ,/*input [5:0] */.address ( address ) ,/*input [7:0] */.data ( data ) ,/*input */.redn ( rden ) ,/*input */.wren ( wren ) ,/*output [7:0] */.q ( q )

);always #(CYCLE/2) tb_clk = ~tb_clk;integer i;

initial begintb_clk = 1'b1;tb_rst_n = 1'b1;#(CYCLE*2);tb_rst_n = 1'b0;address = 0;//复位赋初值data = 0;rden = 0;wren = 0;#(CYCLE*10);tb_rst_n = 1'b1;#(100*CYCLE);for (i=0;i<64 ;i=i+1 ) begin //写入数据address = i;data = i+1;wren = 1'b1;#CYCLE;endwren = 0;#(CYCLE*10);for (i=10;i<32 ;i=i+1 ) begin //读取数据address = i;rden = 1'b1;#CYCLE;endrden = 0;$stop;

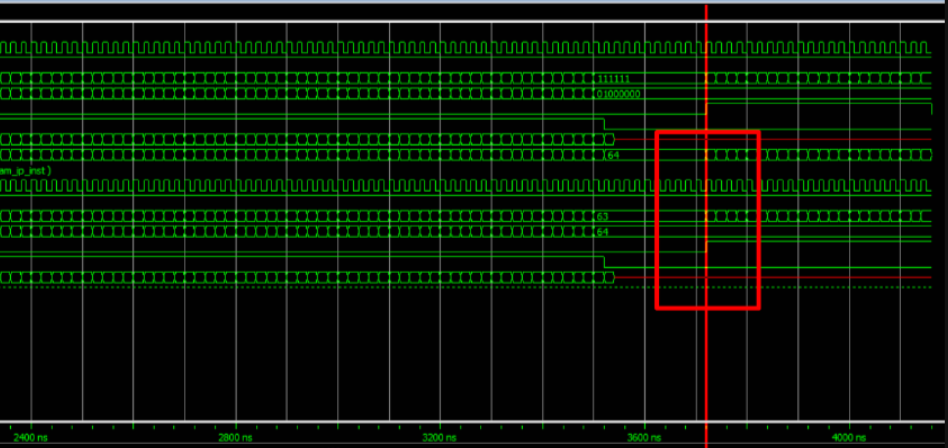

endendmodule结果如下

(三)FIFO先进先出存储器

FIFO(先进先出存储器) 是一种特殊类型的缓冲存储器,其数据存取遵循先进先出(First-In-First-Out)原则,即最先写入的数据会被最先读出。它在数字系统中广泛应用于数据缓冲、时钟域隔离、流量控制等场景,尤其在FPGA设计中是解决多模块间数据速率不匹配问题的核心组件。

FIFO的核心概念

-

基本结构

-

存储单元:通常由寄存器链、Block RAM或分布式RAM实现。

-

写指针(Write Pointer):指示下一个数据写入的位置。

-

读指针(Read Pointer):指示下一个数据读取的位置。

-

状态信号:

-

full(满标志):禁止继续写入。 -

empty(空标志):禁止继续读取。 -

almost_full/almost_empty:阈值预警信号。

-

-

-

工作原理

-

写入操作:数据按顺序存入存储单元,写指针递增。

-

读取操作:数据按存入顺序被取出,读指针递增。

-

指针循环:当指针到达存储空间末尾时,自动回到起始位置(环形缓冲)。

-

FIFO的设计关键参数

-

深度(Depth)

-

决定FIFO的容量,需根据数据生产与消费的最大速率差计算。

-

公式:

最小深度=突发数据量×(写速率−读速率)写速率最小深度=写速率突发数据量×(写速率−读速率)

-

-

宽度(Width)

-

数据位宽(如8位、16位、32位),需与上下游模块匹配。

-

-

满/空判断逻辑

-

计数器法:通过记录数据数量判断状态,资源占用较多。

-

指针比较法:利用读写指针的位置关系判断,资源更高效。

-

创建文件步骤如上RAM,ROM。

.v代码

module fifo_test( input wire wr_clk ,//写时钟input wire rd_clk ,//读时钟input wire rst_n ,input wire [7:0] wr_din ,//写入fifo数据input wire wr_en ,//写使能input wire rd_en ,//读使能output reg [7:0] rd_dout ,//读出的数据output reg rd_out_vld //读有效信号

);//------------<参数说明>--------------------------------------------wire [7:0] wr_data ;

wire [7:0] q ;

wire wr_req ;//写请求

wire rd_req ;//读请求

wire wr_empty ;//写空

wire wr_full ;//写满

wire rd_empty ;//读空

wire rd_full ;//读满

wire [7:0] wr_usedw ;//在写时钟域下,FIFO 中剩余的数据量;

wire [7:0] rd_usedw ;//在读时钟域下,FIFO 中剩余的数据量。fifo fifo_inst (.data ( wr_data ),.rdclk ( rd_clk ),.rdreq ( rd_req ),.wrclk ( wr_clk ),.wrreq ( wr_req ),.q ( q ),.rdempty ( rd_empty ),.rdfull ( rd_full ),.rdusedw ( rd_usedw ),.wrempty ( wr_empty ),.wrfull ( wr_full ),.wrusedw ( wr_usedw ));

assign wr_data = wr_din;

assign wr_req = (wr_full == 1'b0)?wr_en:1'b0;

assign rd_req = (rd_empty == 1'b0)?rd_en:1'b0;always @(posedge rd_clk or negedge rst_n)beginif(!rst_n)beginrd_dout <= 0;endelse beginrd_dout <= q;end

end

always @(posedge rd_clk or negedge rst_n)beginif(!rst_n)beginrd_out_vld <= 1'b0;endelse beginrd_out_vld <= rd_req;end

end

endmodule测试代码:

`timescale 1 ns/1 ns

module tb_fifo();

//时钟和复位reg wr_clk;reg rd_clk;reg rst_n ;

//输入信号reg [7:0] wr_din;reg wr_en ;reg rd_en ;

//输出信号wire rd_out_vld;wire [7:0] rd_dout;parameter WR_CYCLE = 20;//写时钟周期,单位为 ns,

parameter RD_CYCLE = 30;//读时钟周期,单位为 ns,

parameter RST_TIME = 3 ;//复位时间,此时表示复位 3 个时钟周期的时间。

//待测试的模块例化fifo_test fifo_test_inst( /*input wire */.wr_clk ( wr_clk ) ,//写时钟/*input wire */.rd_clk ( rd_clk ) ,//读时钟/*input wire */.rst_n ( rst_n ) ,/*input wire [7:0] */.wr_din ( wr_din ) ,//写入fifo数据/*input wire */.wr_en ( wr_en ) ,//写使能/*input wire */.rd_en ( rd_en ) ,//读使能/*output reg [7:0] */.rd_dout ( rd_dout ) ,//读出的数据/*output reg */.rd_out_vld ( rd_out_vld ) //读有效信号

);integer i = 0;

//生成本地时钟 50Minitial wr_clk = 0;always #(WR_CYCLE/2) wr_clk=~wr_clk;initial rd_clk = 0;always #(RD_CYCLE/2) rd_clk=~rd_clk;

//产生复位信号initial beginrst_n = 1;#2;rst_n = 0;#(WR_CYCLE*RST_TIME);rst_n = 1;end

//输入信号赋值initial begin#1;wr_din = 0;//赋初值wr_en = 0;#(10*WR_CYCLE);for(i=0;i<500;i=i+1)begin//开始赋值wr_din = {$random};wr_en = {$random};#(1*WR_CYCLE);end#(100*WR_CYCLE);endinitial begin#1;rd_en = 0;//赋初值#(12*RD_CYCLE); for(i=0;i<500;i=i+1)begin//开始赋值rd_en = {$random};#(1*RD_CYCLE);end#(100*RD_CYCLE);$stop;end

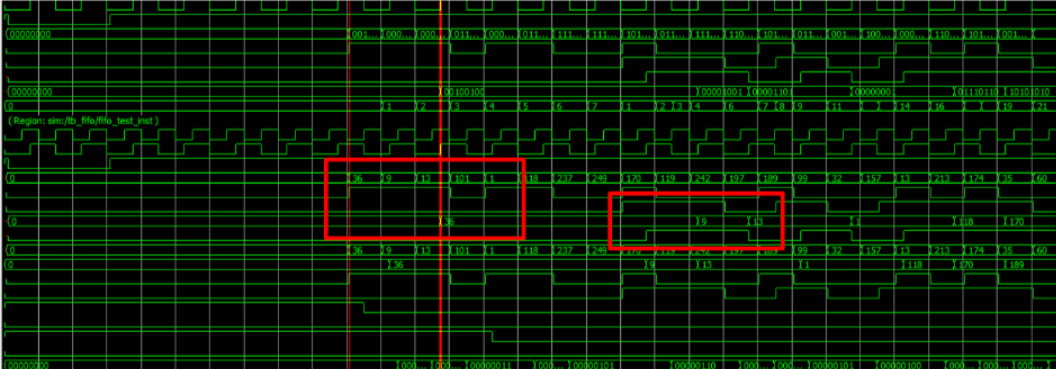

endmodule结果如下

四、总结

在近期的FPGA开发学习中,我重点攻克了RAM、ROM、FIFO等存储类IP核的设计与应用。这段学习历程不仅让我掌握了硬件描述语言与工具链的协同工作逻辑,更让我深刻体会到“硬件思维”与“软件思维”的差异。

参考博客:FPGA入门学习Day1——设计一个DDS信号发生器-CSDN博客

相关文章:

[FPGA]设计一个DDS信号发生器

一、DDS DDS(Data Distribution Service) 是一种面向实时分布式系统的通信中间件标准,专为高性能、高可靠性、低延迟的数据传输场景设计。它由对象管理组织(OMG) 制定并维护,广泛应用于物联网(…...

)

MySQL 线上大表 DDL 如何避免锁表(pt-online-schema-change)

文章目录 1、锁表问题2、pt-online-schema-change 原理3、pt-online-schema-change 实战3.1、准备数据3.2、安装工具3.3、模拟锁表3.4、解决锁表 1、锁表问题 在系统研发过程中,随着业务需求千变万化,避免不了调整线上MySQL DDL数据表的操作,…...

脚本中**通配符用法解析

在文件路径匹配中,** 是一种特殊的通配符(Glob Pattern),主要用于表示递归匹配任意层级的子目录。这种语法常见于以下场景: 1. 典型应用场景 .gitignore 文件: **/__pycache__ 表示匹配项目根目录下所有层…...

5 提示词工程指南-计划与行动

5 提示词工程指南-计划与行动 计划与行动 Cline 有两种模式: Plan 描述目标和需求、提问与回答、讨论、抽象项目的各个方面、确定技术路线、确定计划 计划与确认相当于架构师,不编写代码Act 按计划编写代码 按照计划编码Plan 模式的本质是构建实际编码前的上下文,Act 的本…...

62页华为IPD-MM流程:市场调研理论与实践方案精读【附全文阅读】

本文围绕市场调研展开,介绍其是联系市场和企业的纽带,具有收集陈述事实、解释信息、预测市场变化的作用,在 IPD 产品开发流程各阶段有不同应用。市场调研类型包括定性和定量研究,一般程序涵盖定义问题、拟定计划、抽样设计等多个环节。常用调研方法多样,各有特点和适用项目…...

mac中Grafana监控Linux上的CPU等(Node_exporter 安装使用))

(一)mac中Grafana监控Linux上的CPU等(Node_exporter 安装使用)

机器状态监控(监控服务器CPU,硬盘,网络等状态) Node_exporter安装在被测服务器上,启动服务 各步骤的IP地址要换为被测服务器的IP地址Prometheus.yml的 targets值网页访问的ip部分grafana添加数据源的URL 注意:只需要在被监听的服务器安装 n…...

STM32单片机入门学习——第44节: [13-1] PWR电源控制

写这个文章是用来学习的,记录一下我的学习过程。希望我能一直坚持下去,我只是一个小白,只是想好好学习,我知道这会很难,但我还是想去做! 本文写于:2025.04.20 STM32开发板学习——第44节: [13-1] PWR电源控制 前言开发板说明引用解答和科普一…...

Windows 10 上安装 Spring Boot CLI详细步骤

在 Windows 10 上安装 Spring Boot CLI 可以通过以下几种方式完成。以下是详细的步骤说明: 1. 手动安装(推荐) 步骤 1:下载 Spring Boot CLI 访问 Spring Boot CLI 官方发布页面。下载最新版本的 .zip 文件(例如 sp…...

WEMOS LOLIN32 开发板引脚布局和技术规格

🔗 快速链接ESP32 Development Boards, Sensors, Tools, Projects and More https://megma.ma/wp-content/uploads/2021/08/Wemos-ESP32-Lolin32-Board-BOOK-ENGLISH.pdf WEMOS LOLIN32 Development Board Details, Pinout, Specs WEMOS LOLIN32 Development Board …...

【AI 加持下的 Python 编程实战 2_07】第七章:基于 Copilot 完整演示问题分解能力在实际问题中的落地应用

【全新第二版《Learn AI-assisted Python Programming》封面】 写在前面 问题分解能力在 AI 辅助编程中具有举足轻重的作用。但是怎样分解才算合理有效呢?本章从一个具体的案例切入,完整展示了 GitHub Copilot 在自顶而下设计论的指导下圆满完成既定任务…...

React 路由入门秘籍:BrowserRouter 的江湖之道

前言 各位江湖中人,今日咱们聊一门流传在前端江湖的神秘绝学:<BrowserRouter>。此技出自 React 路由门派,专修客户端路由之道,擅长在 Web 世界中轻功跳转、闪转腾挪,悄无声息间掌控页面切换。 若你是构建现代 Web 应用的侠客,这篇秘籍堪比九阳真经,一经参悟,便…...

软件安装,systemctl命令,软连接

yum是centos里面的(apt是Ubuntu的) yum:RPM软件管理器,用于自动化安装配置Linux软件,并可以自动解决依赖问题 语法:yum 【-y】【install | remove | search | restart 】软件名称 -y:自动确…...

SpringBoot Actuator健康检查:自定义HealthIndicator

文章目录 引言一、Spring Boot Actuator健康检查概述二、自定义HealthIndicator的必要性三、实现自定义HealthIndicator四、高级健康检查配置五、实现自定义健康状态和响应码总结 引言 Spring Boot Actuator是Spring Boot框架中用于监控和管理应用程序的强大功能模块。它提供了…...

单头和多头)

注意力机制(np计算示例)单头和多头

为了更好理解注意力机制里面的qkv矩阵,使用np来演示。 单头注意力 import numpy as np import math# 初始化输入 X X np.array([[[1, 2, 3], [4, 5, 6]]])# 初始化权重矩阵 WQ、WK、WV WQ np.array([[1, 0], [0, 1], [0, 0]])WK np.array([[1, 0], [0, 1], [0,…...

)

生成对抗网络(Generative adversarial network——GAN)

文章目录 1. 前言1.1 判别器和生成器的作用?2.2 个人总结 2. 核心代码示例2.1 训练判别器网络2.2 训练生成器网络 参考文章 1. 前言 生成对抗网络的原文:Generative Adversarial Nets,该论文的精读视频:生成对抗网络GAN开山之作论…...

CSGHub开源版本v1.6.0更新

CSGHub v1.6.0 带来了多项核心功能升级与性能优化,显著增强了对大模型推理、微调、评估等流程的支持,并进一步完善了推理服务与用户交互体验。 插件化推理与训练引擎框架 推理、微调和评估引擎现已全面模块化,支持通过配置文件灵活接入多种引…...

)

Redis日常学习(一)

我的Redis学习笔记:从命令行到性能调优 Redis Redis(Remote Dictionary Server)本质上是一个基于内存的键值存储系统. 安装配置Redis的过程非常简单: # Ubuntu/Debian安装Redis sudo apt-get update sudo apt-get install red…...

Unity3D仿星露谷物语开发37之浇水动画

1、目标 当点击水壶时,实现浇水的动画。同时有一个水从水壶中流出来的特效。 假如某个grid被浇过了,则不能再浇水了。。 如果某个grid没有被dug过,也不能被浇水。 2、优化Settings.cs脚本 增加如下内容: public static float…...

JavaScript 一维数组转不含零的两个数

问题描述: /*** param {number} n* return {number[]}*/ var getNoZeroIntegers function(n) {for(let i 1;i<n;i){if(String(i).indexOf(0) -1&&String(n-i).indexOf(0) -1){return [i,n-i]}}};String类型indexOf()函数如果找不到字串则返回-1&…...

)

抽象工厂模式及其在自动驾驶中的应用举例(c++代码实现)

模式定义 抽象工厂模式(Abstract Factory Pattern)是一种创建型设计模式,用于封装一组具有共同主题的独立对象创建过程。该模式通过提供统一接口创建相关对象家族,而无需指定具体实现类,特别适合需要保证系统组件兼容…...

知乎十四载:从精英问答到AI时代的知识灯塔

一、起源:Quora 的火种与周源的执念 2010 年,互联网浪潮正汹涌澎湃,各种新兴平台如雨后春笋般不断涌现。就在这一年的一个夜晚,周源像往常一样在网上浏览着各类信息,当他打开美国问答网站 Quora 时,瞬间被…...

Linux文件时间戳详解:Access、Modify、Change时间的区别与作用

在 Linux 系统中,文件的这三个时间戳(Access、Modify、Change)分别表示不同的文件状态变更时间,具体含义如下: 1. Access Time (Access) 含义:文件最后一次被访问的时间(读取内容或执行…...

Doris + Iceberg 构建冷热分层数据湖架构:架构设计与实战指南

在海量数据治理与存储演进中,冷热数据分层 已成为降本增效的关键策略。本篇将深入探讨如何结合 Apache Doris 与 Apache Iceberg 构建一套高性能、可扩展的数据湖架构,支持冷热数据自动分层、快速查询与灵活扩展。 一、背景:为什么需要冷热数…...

)

顺序表和链表的区别(C语言)

前言 线性表是最基础的数据结构之一,其中顺序表与链表分别代表两种存储方式: 顺序表(Sequential List):底层用数组实现,要求内存连续,典型代码以 int data[N] 或动态分配的 malloc/realloc 数…...

)

【Redis】Redis中的常见数据类型(一)

文章目录 前言一、Redis前置知识1. 全局命令2、数据结构和内部编码3. 单线程架构 二、String 字符串1. 常见命令2. 计数命令3.其他命令4. 内部编码5. 典型使用场景 三、Hash哈希1. 命令2.内部编码3. 使用场景4. 缓存方式对比 结语 前言 Redis 提供了 5 种数据结构,…...

Vue3 + TypeScript,使用祖先传后代模式重构父传子模式

父传子模式 父组件 SampleInput.vue <script setup lang"ts" name"SampleInput"> import { ref } from "vue"; import type { ApplyBasicInfo, Apply, ApplySample } from "/interface"; import CommonApplySampleTable from …...

MySQL:9.表的内连和外连

9.表的内连和外连 表的连接分为内连和外连 9.1 内连接 内连接实际上就是利用where子句对两种表形成的笛卡儿积进行筛选,之前查询都是内连 接,也是在开发过程中使用的最多的连接查询。 语法: select 字段 from 表1 inner join 表2 on 连接…...

Grafana监控系统之监控Linux的Redis)

(mac)Grafana监控系统之监控Linux的Redis

Grafana安装-CSDN博客 普罗米修斯Prometheus监控安装(mac)-CSDN博客 1.Redis_exporter安装 直接下载 wget https://github.com/oliver006/redis_exporter/releases/download/v1.0.3/redis_exporter-v1.0.3.linux-amd64.tar.gz 解压 tar -xvf redis_…...

)

Multisim使用教程详尽版--(2025最新版)

一、Multisim14前言 1.1、主流电路仿真软件 1. Multisim:NI开发的SPICE标准仿真工具,支持模拟/数字电路混合仿真,内置丰富的元件库和虚拟仪器(示波器、频谱仪等),适合教学和竞赛设计。官网:艾…...

python pdf转图片再OCR

先pdf转图片 import os from pdf2image import convert_from_path# PDF文件路径 pdf_path /Users/xxx/2022.pdf # 输出图片的文件夹 output_folder ./output_images2022 # 输出图片的命名格式 output_name page# 如果输出文件夹不存在,创建它 if not os.path.ex…...

npm link 使用指南

npm link 使用指南 npm link 是一个非常有用的命令,主要用于在开发过程中将本地 npm 包链接到全局 npm 目录,从而可以在其他项目中使用这个本地包,而不需要发布到 npm 仓库。 基本用法 1. 创建全局链接 进入你要链接的本地包的根目录&…...

免费图片软件,可矫正倾斜、调整去底效果

软件介绍 有个超棒的软件要给大家介绍一下哦,它就是——ImgTool,能实现图片漂白去底的功能,而且重点是,它是完全免费使用的呢,功能超强大! 软件特点及使用便捷性 这软件是绿色版本的哟,就像一…...

5G网络切片:精准分配资源,提升网络效率的关键技术

5G网络切片:精准分配资源,提升网络效率的关键技术 随着5G技术的广泛应用,网络切片(Network Slicing)作为其核心创新之一,正在改变传统网络架构。它通过将物理网络划分为多个逻辑网络(切片&…...

seate TCC模式案例

场景描述 用户下单时,需要创建订单并从用户账户中扣除相应的余额。如果订单创建成功但余额划扣失败,则需要回滚订单创建操作。使用 Seata 的 TCC 模式来保证分布式事务的一致性。 1. 项目结构 假设我们有两个微服务: Order Service&#x…...

Transfomer的本质

Transformer是一个基于自注意力机制的深度学习模型,用于处理序列数据,主要结构包括编码器和解码器,每个部分由多头自注意力和前馈网络组成,加上残差连接和层归一化,以及位置编码。它解决了RNN的并行处理问题࿰…...

final修饰变量的注意

在Java中,使用final修饰变量时,需注意以下关键事项: 1. 初始化规则 实例变量: 必须在声明时、构造器或实例初始化块中初始化。所有构造器分支必须保证初始化。 class Example {final int x; // 实例变量final int y;public Exampl…...

前端与传统接口的桥梁:JSONP解决方案

1.JSONP原理 1.1.动态脚本注入 说明:通过创建 <script> 标签绕过浏览器同源策略 1.2.回调约定 说明:服务端返回 函数名(JSON数据) 格式的JS代码 1.3.自动执行 说明:浏览器加载脚本后立即触发前端预定义的回调函数(现代开…...

SQL注入 01

0x01 用户、脚本、数据库之间的关系 首先客户端发出了ID36的请求,脚本引擎收到后将ID36的请求先代入脚本的sql查询语句Select * from A where id 36 , 然后将此代入到数据库中进行查询,查到后将返回查询到的所有记录给脚本引擎,接…...

)

Java之封装(学习笔记)

封装定义(个人理解:) 封装就像电视遥控器的按钮,比如音量键,对于我们使用者来说就是可以直接按下去调控音量,对于代码写作者来说就是封装了调控音量的方法,使得我们只能去调控,不能改…...

:head)

每天学一个 Linux 命令(27):head

可访问网站查看,视觉品味拉满: http://www.616vip.cn/27/index.html head 是 Linux 中用于查看文件开头部分内容的命令,默认显示文件前 10 行,适合快速预览文件结构或日志头部信息。 命令格式 head [选项] [文件]常用选项 选项说明-n <行数>指定显示前 N 行(如…...

之中医知识问答自动生成对话标题bug修改)

山东大学软件学院创新项目实训开发日志(20)之中医知识问答自动生成对话标题bug修改

在原代码中存在一个bug:当前对话的标题不是现有对话的用户的第一段的前几个字,而是历史对话的第一段的前几个字。 这是生成标题的逻辑出了错误: 当改成size()-1即可...

论文阅读:2024 ICML Is DPO Superior to PPO for LLM Alignment? A Comprehensive Study

Is DPO Superior to PPO for LLM Alignment? A Comprehensive Study https://www.doubao.com/chat/3506902534329346 https://arxiv.org/pdf/2404.10719 速览 这篇论文主要探讨了大语言模型对齐中两种主流方法——**DPO(直接偏好优化)和PPO…...

2025年人工智能指数报告:技术突破与社会变革的全景透视

《2025年人工智能指数报告》作为斯坦福大学人工智能实验室与多方合作的年度重磅研究,以超过千页的篇幅全景式展现了人工智能技术在全球范围内的发展轨迹与深远影响。这份报告不仅延续了对AI技术性能、科研进展与产业应用的追踪,更首次深入探讨了AI硬件的…...

【Python笔记 01】变量、标识符

一、 变量 1、变量的作用 计算机存储空间,用于保存数据。 2、定义变量的格式 格式:变量名 值 示例: num1 3 # num1就是一个变量,保存蛋糕的价格 num2 10 #num2也是一个变量,保存雪碧的价格 total num1 num2 …...

WebSocket启用备忘

一:引入依赖: <!--WebSocket专用--><dependency><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-websocket</artifactId></dependency><dependency><groupId>org…...

)

文件管理详解(曼波脑图版)

(✪ω✪)曼波来啦!文件管理的知识曼波这就为你详细讲解哟~ 记得要准备好小本本做笔记哦!(๑˃̵ᴗ˂̵)و 🌟 文件读写操作 🌟 // 最可爱的文件读取写法 (✧∇✧) try (BufferedReader reader new BufferedReader(new FileRead…...

学习笔记十九——Rust多态

🧩 Rust 多态终极通俗指南 📚 目录导航 多态一句话概念静态分派 vs 动态分派——根本差异参数化多态(泛型) 3.1 函数里的泛型 3.2 结构体里的泛型 3.3 方法里的泛型 3.4 枚举里的泛型Ad hoc 多态(特例多态࿰…...

在 Linux 上部署 .NET Core 应用并配置为开机自动启动

在本文中,我们将详细介绍如何在 Linux 系统上部署 .NET Core 应用程序,并配置为开机自动启动。以下是一步一步的详细部署过程,适用于将 .NET Core Web 应用部署到生产环境中。 1. 安装 .NET 运行时和 SDK 首先,确保 Linux 系统上…...

dubbo SPI插件扩展点使用

参考:SPI插件扩展点 Dubbo SPI概述 使用IoC容器帮助管理组件的生命周期、依赖关系注入等是很多开发框架的常用设计,Dubbo中内置了一个轻量版本的IoC容器,用来管理框架内部的插件,实现包括插件实例化、生命周期、依赖关系自动注入…...

P8512 [Ynoi Easy Round 2021] TEST_152 Solution

Description 有一序列 c ( c 1 , c 2 , ⋯ , c m ) c(c_1,c_2,\cdots,c_m) c(c1,c2,⋯,cm) 和 n n n 个三元组 ( l i , r i , v i ) (l_i,r_i,v_i) (li,ri,vi). 回答 q q q 次形如 ( L , R ) (L,R) (L,R) 的询问,具体如下: 将 c c …...