一种大位宽加减法器的时序优化

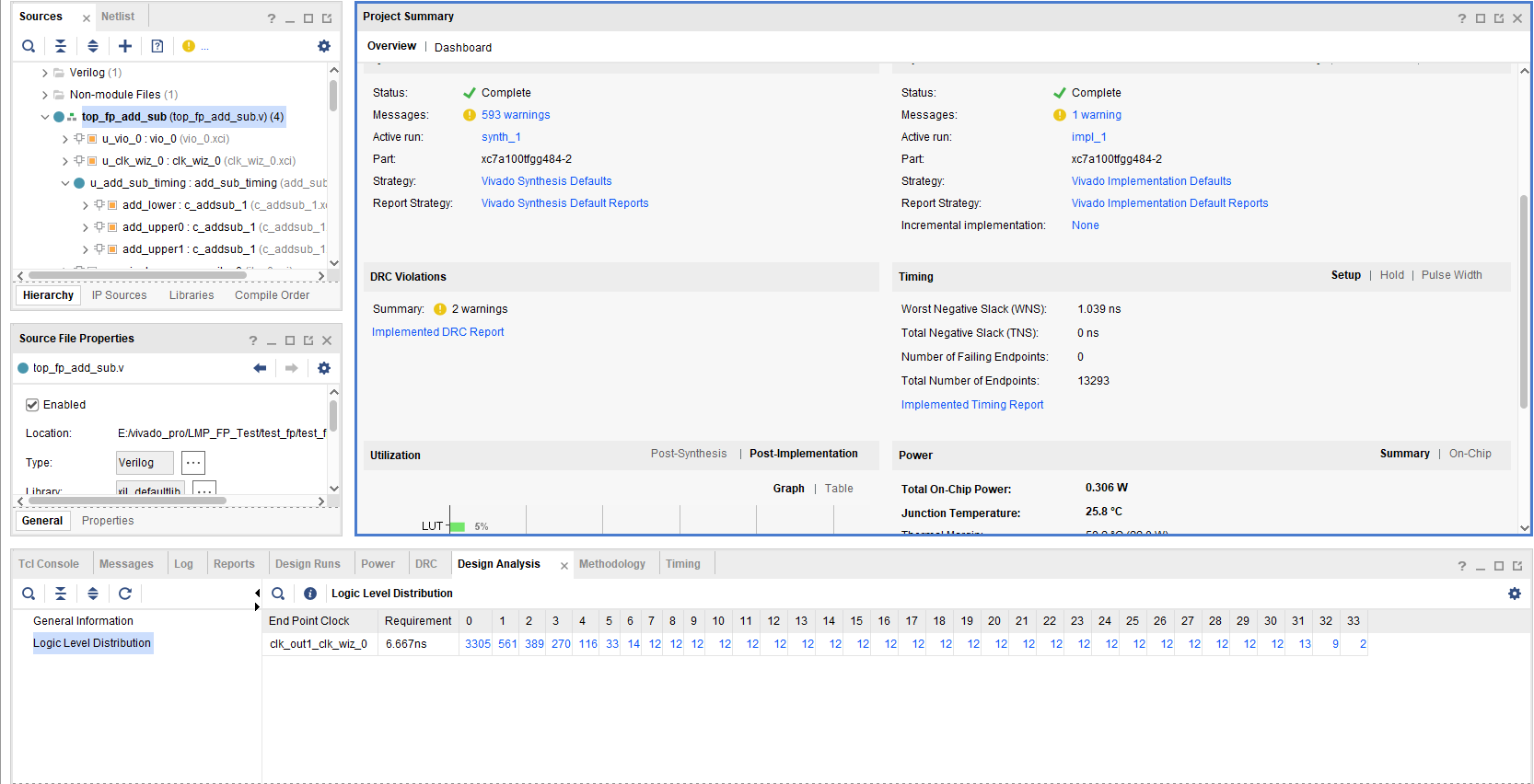

平台:vivado2018.3

芯片:xc7a100tfgg484-2 (active)

在FPGA中实现超高位宽加减法器(如256)时,时序收敛常成为瓶颈。由于进位链(Carry Chain)跨越多级逻辑单元,关键路径延迟会随位宽指数增长,导致时钟频率急剧下降。针对这一问题,现在使用如下方式优化大位宽加减法器的时序。

这里使用进位选择加减法器,通过并行计算和进位预测技术,优化加减法器的路径延时,提高整体的运算速度。

优化的核心机制:模块的拆分与并行处理

这里使用减法为例。

1、将输入位宽拆分进行并行处理。

将输入高位宽数据拆分为两部分,低位宽数据和高位宽数据。

使用并行减法器代替高位宽减法器。使用低位减法器(add_lower)计算低位宽数据的差值。同时计算高位宽的减法结果,根据减法器的结构,提前计算借位为0(add_upper0)和借位为1(add_upper1)的两种计算结果。

2、输出结果

根据低位减法器(add_lower)输出借位cout决定高位结果的选取。假如借位为0,选择add_upper0的无借位结果。如果借位为1,选择add_upper1的带借位结果。将最终结果进行拼合。

代码展示

这里都使用vivado的加法器,添加vio和ila的工程。

不使用进位选择。

c_addsub_0 u_c_addsub_0 (.A (dataa ), // input wire [255 : 0] A.B (datab ), // input wire [255 : 0] B.CLK (clock ), // input wire CLK.ADD (1'b0 ), // input wire ADD.C_IN (1'b1 ), // input wire C_IN.C_OUT ( ), // output wire C_OUT.S (result )// output wire [255 : 0] S

);使用进位选择。

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2025/4/17 9:30:25

// File Name : .v

// Module Name :

// Called By :

// Abstract :

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module add_sub_timing#(

parameter WIDTH = 256)(

input wire [WIDTH-1:0] dataa , //

input wire [WIDTH-1:0] datab , //

output wire [WIDTH-1:0] result , //

input wire clock // );

//----------------------------------------------

// localparam

//----------------------------------------------//----------------------------------------------

// register

//----------------------------------------------//----------------------------------------------

// wire

//----------------------------------------------

wire lower_cout ;

wire [WIDTH/2-1:0] lower_result ;

wire [WIDTH/2-1:0] upper0_result ;

wire [WIDTH/2-1:0] upper1_result ;

wire [WIDTH-1:0] dataa_w ;

wire [WIDTH-1:0] datab_w ;

wire [WIDTH-1:0] result_w ;

//----------------------------------------------

// assign

//----------------------------------------------

assign dataa_w = dataa ;

assign datab_w = datab ;

assign result = result_w ;

assign result_w = {(({WIDTH/2{(~ lower_cout)}} & upper0_result) | ({WIDTH/2{lower_cout}} & upper1_result)),lower_result};

//------------------------------------------------------------

//------------------------------------------------------------

c_addsub_1 add_lower (.A (dataa_w[WIDTH/2-1:0] ), // input wire [127 : 0] A.B (datab_w[WIDTH/2-1:0] ), // input wire [127 : 0] B.CLK (clock ), // input wire CLK.ADD (1'b0 ), // input wire ADD.C_IN (1'b1 ), // input wire C_IN.C_OUT (lower_cout ), // output wire C_OUT.S (lower_result )// output wire [127 : 0] S

);c_addsub_1 add_upper0 (.A (dataa_w[WIDTH-1:WIDTH/2] ), // input wire [127 : 0] A.B (datab_w[WIDTH-1:WIDTH/2] ), // input wire [127 : 0] B.CLK (clock ), // input wire CLK.ADD (1'b0 ), // input wire ADD.C_IN (1'b0 ), // input wire C_IN.C_OUT ( ), // output wire C_OUT.S (upper0_result )// output wire [127 : 0] S

);c_addsub_1 add_upper1 (.A (dataa_w[WIDTH-1:WIDTH/2] ), // input wire [127 : 0] A.B (datab_w[WIDTH-1:WIDTH/2] ), // input wire [127 : 0] B.CLK (clock ), // input wire CLK.ADD (1'b0 ), // input wire ADD.C_IN (1'b1 ), // input wire C_IN.C_OUT ( ), // output wire C_OUT.S (upper1_result )// output wire [127 : 0] S

);//------------------------------------------------------------

//------------------------------------------------------------//------------------------------------------------------------

//------------------------------------------------------------

endmodule

顶层top

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2025/2/10 10:20:41

// File Name : .v

// Module Name :

// Called By :

// Abstract :

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module top_add_sub#(

parameter U_DLY = 1'b1)(

input wire clk_p , //

input wire clk_n //);

//----------------------------------------------

// localparam

//----------------------------------------------parameter WIDTH = 256;

//----------------------------------------------

// register

//----------------------------------------------//----------------------------------------------

// wire

//----------------------------------------------

wire [WIDTH-1:0] dataa ; //

wire [WIDTH-1:0] datab ; //

wire [WIDTH-1:0] result ; // //----------------------------------------------

// assign

//----------------------------------------------

vio_0 u_vio_0 (.clk (clock ),// input wire cl.probe_out0 (dataa ), // output wire [255 : 0] probe_out0.probe_out1 (datab )// output wire [255 : 0] probe_out1

);

//------------------------------------------------------------

//------------------------------------------------------------clk_wiz_0 u_clk_wiz_0(// Clock out ports.clk_out1 (clock ), // output clk_out1// Status and control signals.locked (aclr ), // output locked// Clock in ports.clk_in1_p (clk_p ), // input clk_in1_p.clk_in1_n (clk_n )); // input clk_in1_n

//------------------------------------------------------------

//------------------------------------------------------------//c_addsub_0 u_c_addsub_0 (

// .A (dataa ), // input wire [255 : 0] A

// .B (datab ), // input wire [255 : 0] B

// .CLK (clock ), // input wire CLK

// .ADD (1'b0 ), // input wire ADD

// .C_IN (1'b1 ), // input wire C_IN

// .C_OUT ( ), // output wire C_OUT

// .S (result )// output wire [255 : 0] S

//);add_sub_timing u_add_sub_timing(.dataa (dataa ), // (input ) .datab (datab ), // (input ) .result (result ), // (output) .clock (clock )// (input ) );//------------------------------------------------------------

//------------------------------------------------------------ila_0 your_instance_name (.clk(clock), // input wire clk.probe0(dataa ), // input wire [255:0] probe0 .probe1(datab ), // input wire [255:0] probe1 .probe2(result ) // input wire [255:0] probe2

);

//------------------------------------------------------------

//------------------------------------------------------------

endmodule代码仿真。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/03/26 13:54:03

// Design Name:

// Module Name: tb_float_div_nd

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_add_sub;

parameter WIDTH = 256 ; reg clock ; //

reg rst_n ; //

reg [WIDTH-1:0] dataa ; //

reg [WIDTH-1:0] datab ; // wire [WIDTH-1:0] result ;

wire [WIDTH-1:0] result_1 ; wire flog;

assign flog = (result == result_1 ) ? 1 : 0;c_addsub_0 u_c_addsub_0 (.A (dataa ), // input wire [255 : 0] A.B (datab ), // input wire [255 : 0] B.CLK (clock ), // input wire CLK.ADD (1'b0 ), // input wire ADD.C_IN (1'b1 ), // input wire C_IN.C_OUT ( ), // output wire C_OUT.S (result )// output wire [255 : 0] S

);add_sub_timing u_add_sub_timing(.dataa (dataa ), // (input ) .datab (datab ), // (input ) .result (result_1 ), // (output) .clock (clock )// (input ) );initial

beginclock = 0;rst_n = 0;dataa = 0;datab = 0;

// #100;

// rst_n =1;

// #100;

// dataa = 'd128;

// datab = 'd64;

//

// #100;

// dataa = 'd55;

// datab = 'd44;#100;$stop;endalways@(posedge clock)

begindataa <= $random & 32'hfff;datab <= $random & 32'hfff;

endalways#5 clock = ~clock;endmodule

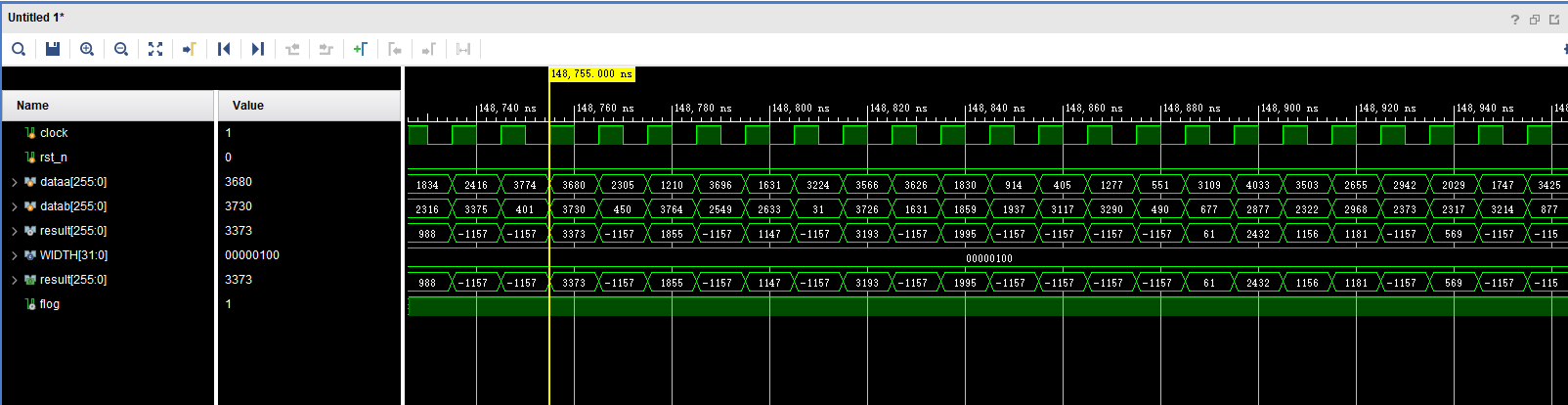

仿真结果

工程综合效果

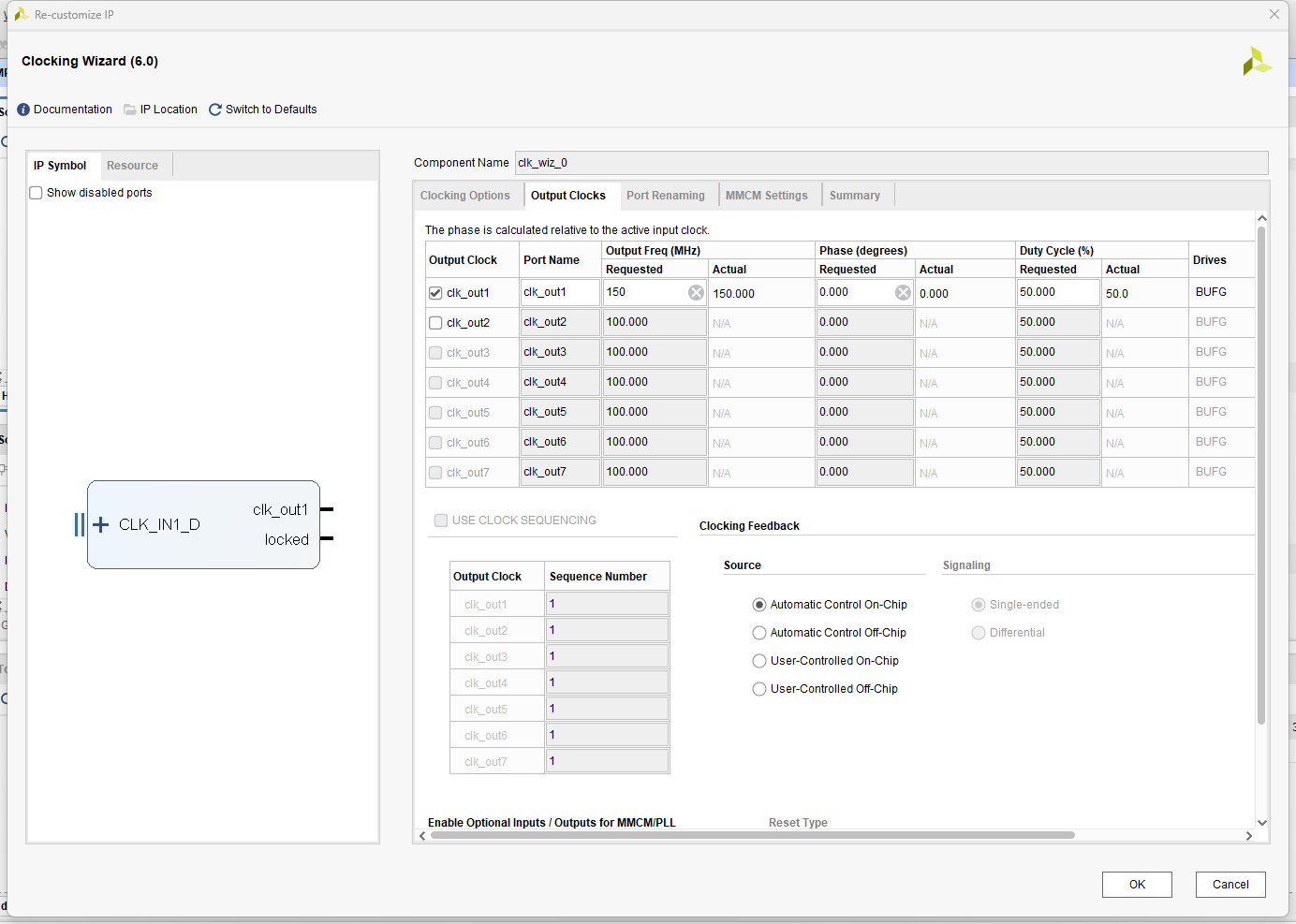

pll输出时钟150MHZ

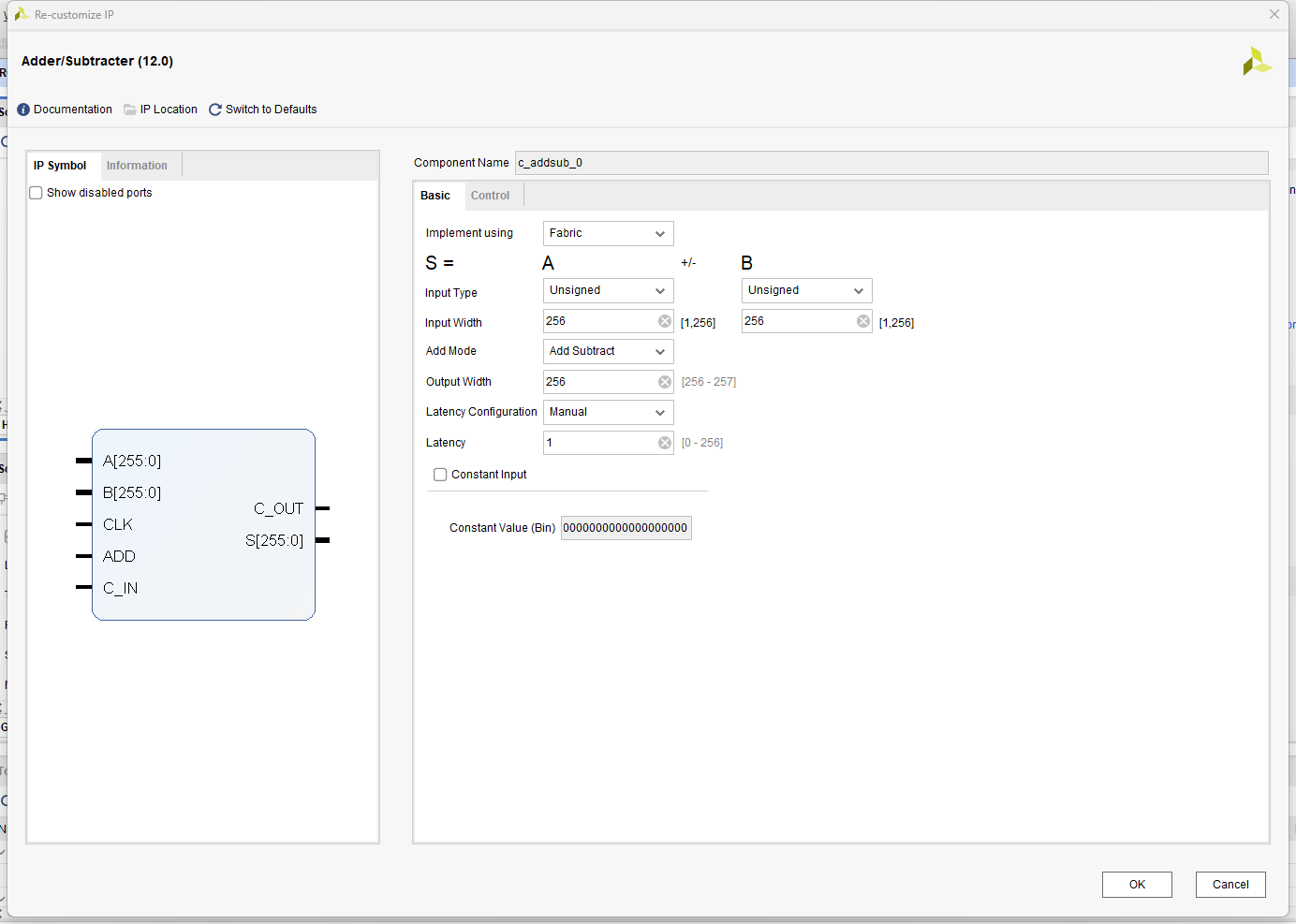

256位宽加法器设置

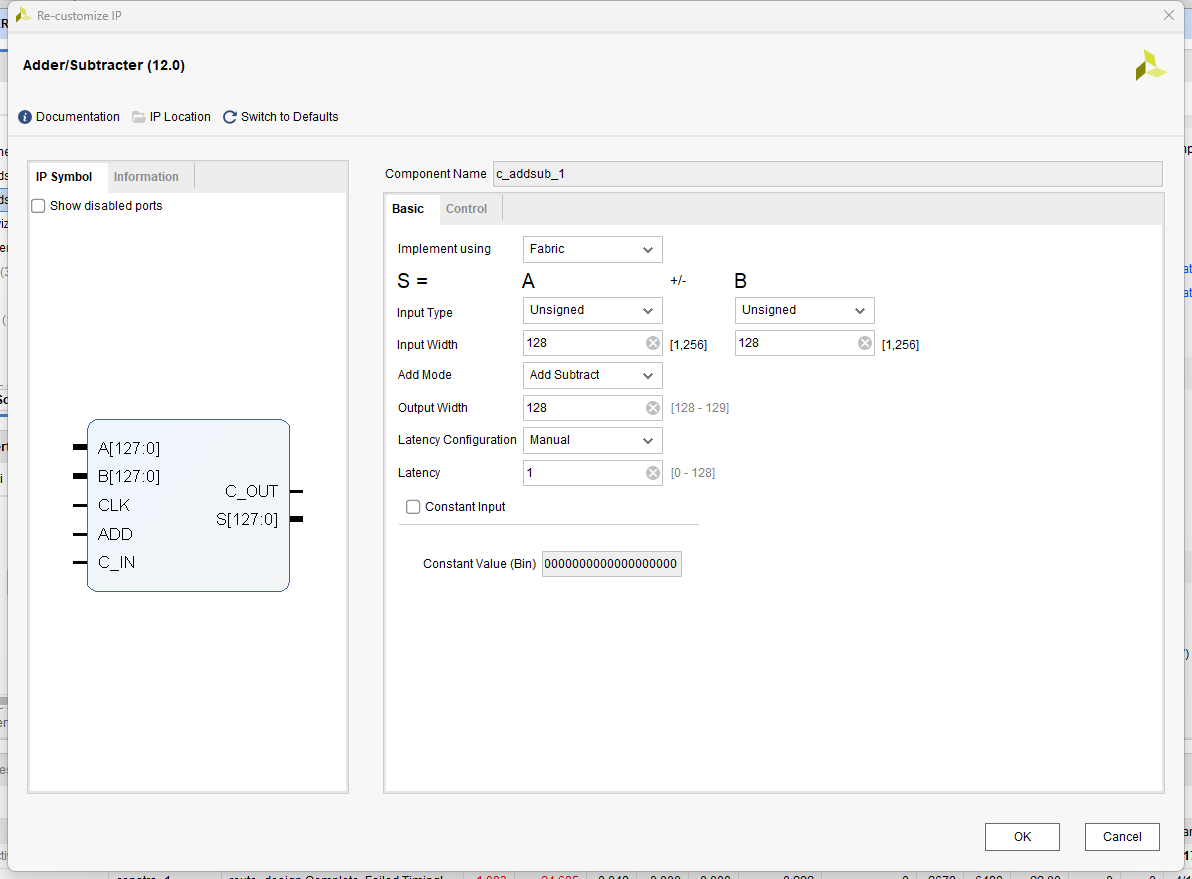

128位宽加法器设置

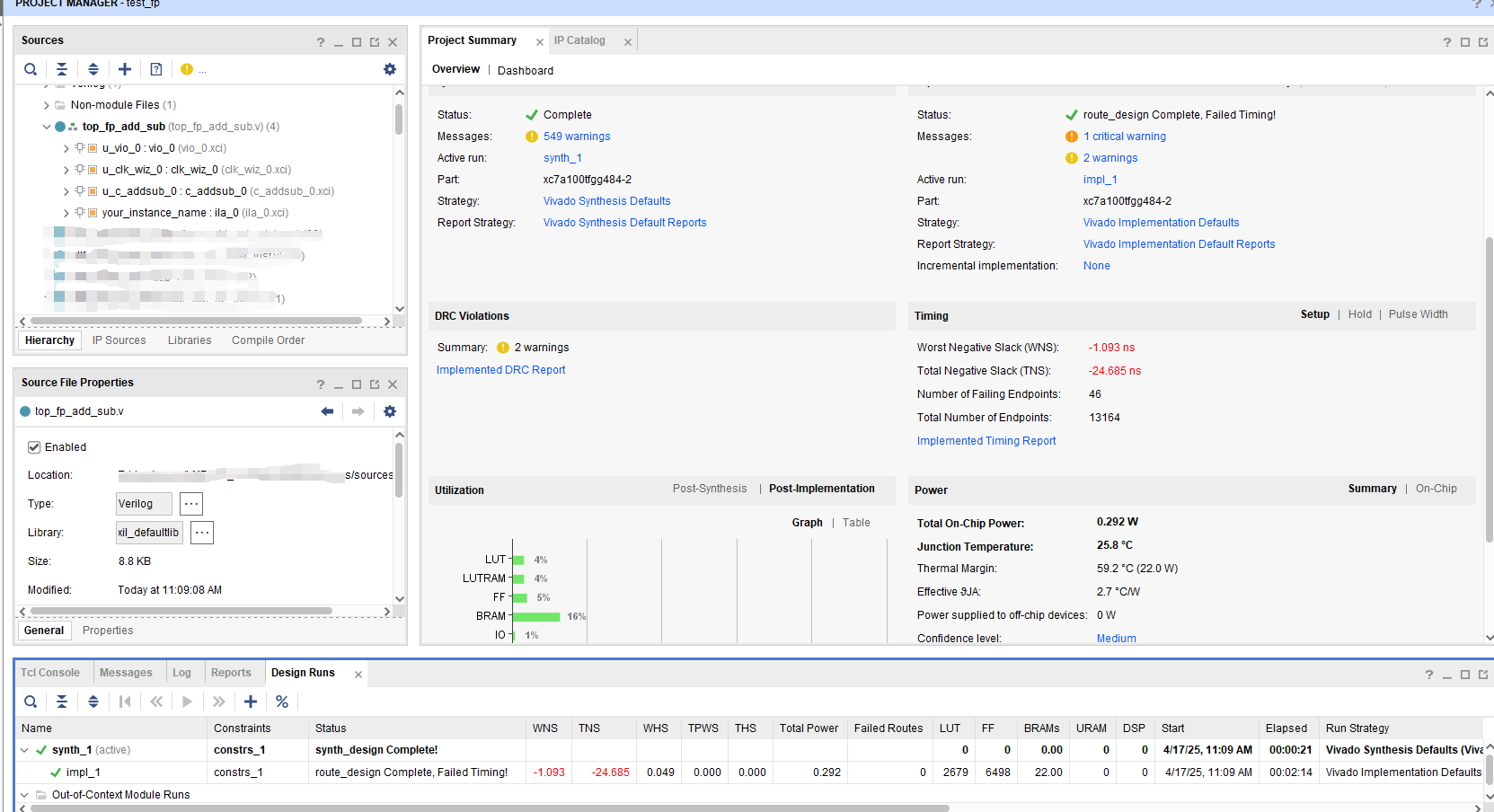

使用高位宽加减法器

综合时序

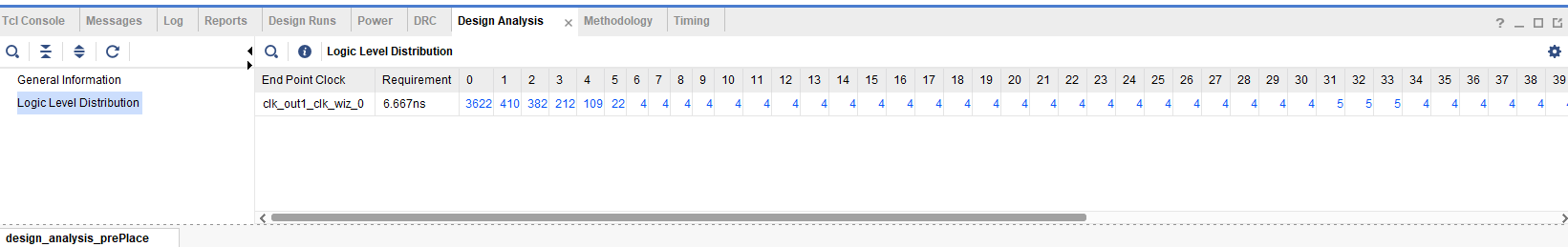

逻辑级数

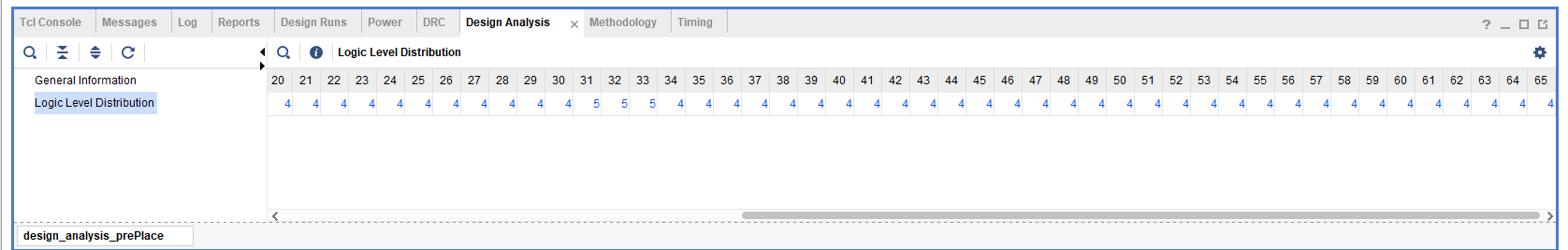

使用进位选择加减法器优化

综合时序

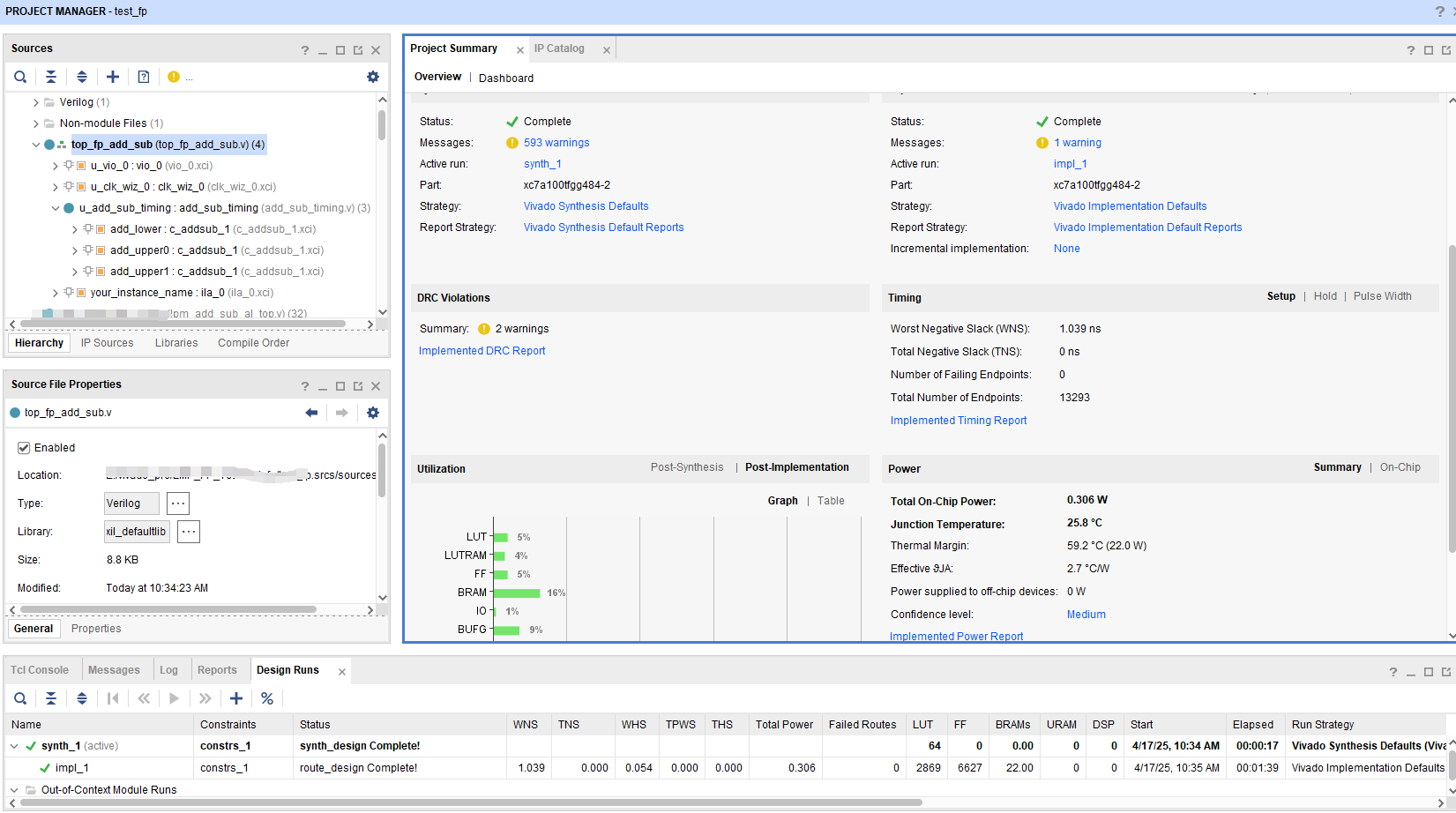

查看逻辑级数

相关文章:

一种大位宽加减法器的时序优化

平台:vivado2018.3 芯片:xc7a100tfgg484-2 (active) 在FPGA中实现超高位宽加减法器(如256)时,时序收敛常成为瓶颈。由于进位链(Carry Chain)跨越多级逻辑单元,关键路径延迟会随位宽…...

】大语言模型与传统编程的桥梁)

【专业解读:Semantic Kernel(SK)】大语言模型与传统编程的桥梁

目录 Start:什么是Semantic Kernel? 一、Semantic Kernel的本质:AI时代的操作系统内核 1.1 重新定义LLM的应用边界 1.2 技术定位对比 二、SK框架的六大核心组件与技术实现 2.1 内核(Kernel):智能任务调度中心 2…...

InfiniBand与RoCEv2负载均衡机制的技术梳理与优化实践

AI技术的高速迭代正驱动全球算力格局进入全新纪元。据IDC预测,未来五年中国智能算力规模将以超50%的年复合增长率爆发式扩张,数据中心全面迈入“智能算力时代”。然而,海量AI训练、实时推理等高并发场景对底层网络提出了更严苛的挑战——超大…...

Vue与React组件化设计对比

组件化是现代前端开发的核心思想之一,而Vue和React作为两大主流框架,在组件化设计上既有相似之处,也存在显著差异。本文将从语法设计、数据管理、组件通信、性能优化、生态系统等多个方向,结合实例详细对比两者的特点。 一、模板…...

UE中通过AAIController::MoveTo函数巡逻至目标点后没法正常更新巡逻目标点

敌人巡逻的逻辑如下: 敌人在游戏一开始的时候就通过moveto函数先前往首先设定的patroltarget目标,在距离patroltarget距离为patroradius(200unit)之内时就可以通过checkpatroltarget函数更新新的patroltarget目标,随后前往新的pat…...

Python-细节知识点range函数的详解

在 Python 中,range 是一个内置函数,用于生成一个不可变的整数序列,通常用于控制循环次数或生成数值范围。以下是详细说明: 基本语法 range(stop) # 生成 [0, stop) 的整数,步长为1 range(start, stop) …...

git rebase的使用

我的使用 git checkout feature # 本地分支 git pull origin main --rebase # 目标分支 git pull origin feature --rebase git push origin featuregit rebase 是 Git 中用于重写提交历史的强大工具,可将分支的提交移动到新的基点上,使历史更线性。以…...

:)

CMake Error at build/_deps/glog-src/CMakeLists.txt:1 (cmake_minimum_required):

这个错误提示意思是你当前系统上安装的 CMake 版本过低,不满足项目的要求。根据错误信息: CMake Error at build/_deps/glog-src/CMakeLists.txt:1 (cmake_minimum_required): CMake 3.22 or higher is required. You are running version 3.16.3 项目…...

MATLAB 控制系统设计与仿真 - 34

多变量系统知识回顾 - MIMO system 这一章对深入理解多变量系统以及鲁棒分析至关重要 首先,对于如下系统: 当G(s)为单输入,单输出系统时: 如果: 则: 所以 当G(s)为MIMO时,例如2X2时ÿ…...

【Unity】JSON数据的存取

这段代码的结构是为了实现 数据的封装和管理,特别是在 Unity 中保存和加载玩家数据时。以下是对代码设计的逐步解释: 1. PlayerCoin 类 PlayerCoin 是一个简单的数据类,用于表示单个玩家的硬币信息。它包含以下字段: count&…...

利用 Java 爬虫按关键字搜索淘宝商品

在电商领域,通过关键字搜索商品是常见的需求。淘宝作为国内知名的电商平台,提供了丰富的商品搜索功能。本文将详细介绍如何使用 Java 爬虫技术按关键字搜索淘宝商品,并获取搜索结果的详细信息。 一、准备工作 1. 注册淘宝开放平台账号 要使…...

【C】初阶数据结构11 -- 选择排序

本篇文章主要讲解经典排序算法 -- 选择排序 目录 1 算法思想 2 代码 3 时间复杂度与空间复杂度分析 1) 时间复杂度 2) 空间复杂度 1 算法思想 选择排序是一种在一段区间里面选择最小的元素和最大的元素的一种排序算法。假设这里排升序&#…...

【Semantic Kernel核心组件】Plugin:连接AI与业务逻辑的桥梁

目录 一、Plugin是什么?为什么它是SK的核心? 一、Plugin的核心机制与Python实现 1. 插件类型:语义函数与本地函数 语义函数(Semantic Function) 本地函数(Native Function) 2. Plugin的注…...

《基于神经网络实现手写数字分类》

《基于神经网络实现手写数字分类》 一、主要内容: 1、通过B站陈云霁老师的网课,配合书本资料,了解神经网络的基本组成和数学原理。 2、申请云平台搭建实验环境 3、基于5个不同的实验模块逐步理解实验操作步骤,并实现不同模块代码…...

车载诊断架构 --- 车载诊断概念的深度解读

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。 老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师: 周末洗了一个澡,换了一身衣服,出了门却不知道去哪儿,不知道去找谁,漫无目的走着,大概这就是成年人最深的孤独吧! 旧人不知我近况,新人不知我过…...

四、探索LangChain:连接语言模型与外部世界的桥梁

一、什么是 LangChain LangChain 是一个开源的软件框架,旨在帮助开发者高效构建和部署基于**大型语言模型(LLM)**的应用程序。它通过提供一系列工具、组件和接口,简化了从模型调用、提示工程到复杂应用开发的全流程,使得开发者能够快速将 LLM 集成到实际场景中。 1. 核心…...

LangChain4j中的Chat与语言模型API详解:构建高效对话系统的利器

LangChain4j中的Chat与语言模型API详解:构建高效对话系统的利器 引言:大模型时代的开发利器 在人工智能快速发展的今天,大型语言模型(LLM)已成为构建智能应用的核心组件。LangChain4j作为Java生态中领先的LLM集成框架…...

C++中const与constexpr的区别

在C中,const和constexpr都用于定义常量,但它们的用途和行为有显著区别: ### 1. **初始化时机** - **const**:表示变量是只读的,但其值可以在**编译时或运行时**初始化。 cpp const int a 5; // 编译…...

长亭2月公开赛Web-ssrfme

环境部署 拉取环境报错: 可以尝试拉取一下ubuntu:16.04,看是否能拉取成功 将wersion:"3"删掉 我拉去成功之后,再去拉取环境,成功! 访问环境 测试ssrf 源码 <?php highlight_file(__file__…...

AI日报 - 2025年4月18日

🌟 今日概览(60秒速览) ▎🤖 AGI探讨 | 专家激辩AGI定义与实现时间点,Causal AI被视为关键一步,o3模型预测2027年实现引关注。 Causal AI强调因果关系而非模式;专家清单推荐不同模型适用场景;AGI定义及何时…...

Spring IoC 详解

在 Spring IoC& DI 详解 中对 IoC已经有了介绍,下面对 IoC 进行详细介绍。 IoC,即控制反转,在之前我们编写程序的时候,我们都是自己 new 出来一个对象,然后自己去管理这个对象,但是这有时候有些麻烦&a…...

oracle查询当前用户所有字段和表

在 Oracle 数据库中,可以通过查询数据字典视图来获取某个表的字段(列)信息。以下是常用的查询方法: 查询当前用户下的表字段 如果您想查看当前用户下某个表的字段信息,可以查询 USER_TAB_COLUMNS 视图: SE…...

)

ACL(访问控制列表)

ACL(访问控制列表) 1、基础内容 访问控制列表ACL(Access ControlList)是由一条或多条规则组成的集合。所谓规则,是指描述报文匹配条件的判断语句,这些条件可以是报文的源地址、目的地址、端口号等。通过一系列规则来匹配报文,如…...

C语言数据结构---二叉树---堆的应用

1.建堆(向上调整) 1.1大堆 #include<stdio.h> void swap(int *p1,int *p2) {int temp *p1;*p1 *p2;*p2 temp; } void Ajustup(int *a,int child)//向上调整 {int parent (child - 1) / 2;while (child > 0){if (a[child] > a[parent]…...

在Linux下安装Gitlab

在Cenos7下安装GitLab 在ssh下安装 官方安装文档:https://gitlab.cn/install/?versionce 1. 使用阿里YUM 镜像云 下载 https://mirrors.aliyun.com/repo/Centos-7.repo替换 /etc/yum.repos.d/CentOS-Base.repo在目录/etc/yum.repos.d/下执行如下命令: curl …...

)

【算法】快速排序、归并排序(非递归版)

目录 一、快速排序(非递归) 1.原理 2.实现 2.1 stack 2.2 partition(array,left,right) 2.3 pivot - 1 > left 二、归并排序(非递归) 1.原理 2.实现 2.1 gap 2.1.1 i 2*gap 2.1.2 gap * 2 2.1.3 gap < array.…...

如何自学机器学习?零基础到实战的完整路径

机器学习作为人工智能的核心领域,已成为技术人必备的硬实力。本文为自学者梳理出一条从零基础到项目落地的系统学习路线,涵盖知识框架、工具链与实战技巧。 一、构建三大基础模块(1-2个月) 数学基石:线性代数重点掌握…...

)

PHP开发环境搭建(Hbuider+phpstudy)

目录 1.Hbuider下载 Hbuider的网址 2.Hbuilder的安装 1-首先找到刚刚下载的安装包 2-然后进行解压 3-进入解压后的文件夹HBuilderX,找到HBuilderX这一项,双击打开 4-选择你喜欢的风格,任意选择一个就可以了 5-选择你选快捷键的方案 6-点击开始体验就可了…...

【4.1.-4.20学习周报】

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 摘要Abstract一、方法介绍1.1HippoRAG 1.2HippoRAG2二、实验2.1实验概况2.2实验代码2.3实验结果 总结 摘要 本博客介绍了论文《From RAG to Memory: Non-Parametri…...

vim笔记

vim三种模式切换 命令常用 复制粘贴...

【JAVA】基础知识“抽象类”详解,从入门到理解~

目录 1. 抽象类 1.1 什么是抽象类❓ 1.2 为什么需要抽象类❓ 1.3 抽象类语法 1.4 抽象类特征 ① 抽象类是被abstract修饰的 ② 被abstract修饰的方法称为抽象方法,这个方法可以没有具体的实现 ③ 当一个类中含有抽象方法的时候,该类必须使用abst…...

docker 启动mysql9认证失败

docker compose 启动mysql9认证失败 随着mysql更新到了9版本,在docker中相较于8减少了一些体积,很吸引人尝试, 但是在使用原本的配置文件拉起mysql,连接时却提示权限认证失败 1045 - Access denied for user root172.18.0.1 (…...

【Axure绘制原型】图片切割、交互动效、热区、动态面板、元件显示隐藏、表单元件、表格、内联框架

切割 功能:将图片切成多部分。 通过移动鼠标可以调整两条虚线的位置,点击。虚线相当于切割刀,被虚线分离的部分将变成单独的图 切割后的图片: 交互 交互动效的构成: 目标:谁触发交互(元…...

:筛选特定空间范围内的POI数据)

DeepSeek智能时空数据分析(一):筛选特定空间范围内的POI数据

时空数据分析很有用,但是GIS/时空数据库技术门槛太高 时空数据分析在优化业务运营中至关重要,尤其在数据驱动决策的当下,其价值正随大模型时代的到来进一步凸显。然而,三大挑战仍制约其发展:技术门槛高,需…...

使用mybatisPlus自带的分页方法+xml实现数据分页

:因为需要实现多表关联分页,原本想的是直接使用selectpagehelper,但是pagehelper只对xml文件生效;后面发现可以直接使用mybatisplus自带的分页,不依靠pagehelper实现多表关联分页; 实现类:关键…...

第六节:React Hooks进阶篇-自定义Hook设计

实战题:实现一个useWindowSize或useFetch 自定义 Hook 设计实战:useWindowSize 与 useFetch 实现详解 一、useWindowSize:实时监听窗口尺寸 1. 基础实现(TypeScript 版) import { useState, useEffect } from react…...

Mybatis--XML映射文件配置和动态SQL

XML文件配置 MyBatis中文网 动态SQL...

【Java学习笔记】位运算

位运算 一、原码,反码,补码 (1) 二进制的最高位是符号位:0 表示正数,1 表示负数(怎么记? 1旋转一下变成-) (2) 正数的原码、反码、补码都一样(三码合一) (3) 负数的反码…...

循环队列的实现

循环队列 实现一个循环队列:C语言代码解析与设计思路1. 循环队列的基本概念2. 数据结构设计3. 初始化队列4. 入队操作5. 出队操作6. 获取队列头部和尾部元素7. 判断队列是否为空或满8. 释放队列资源9. 总结 实现一个循环队列:C语言代码解析与设计思路 在…...

案例驱动的 IT 团队管理:创新与突破之路:第五章 创新管理:从机制设计到文化养成-5.2 技术决策民主化-5.2.1案例:架构设计评审的“七人决策制“

👉 点击关注不迷路 👉 点击关注不迷路 👉 点击关注不迷路 文章大纲 案例驱动的 IT 团队管理:创新与突破之路 - 第五章 创新管理:从机制设计到文化养成5.2 技术决策民主化5.2.1 案例:架构设计评审的“七人决…...

数据库—MySQL游标详解笔记

一、游标是什么? 游标(Cursor) 是数据库中用于逐行遍历查询结果集的数据库对象。它允许开发者像操作指针一样逐行读取数据,适用于需要对查询结果逐行处理的复杂业务逻辑。 核心特点: 逐行操作:类似编程中…...

Genspark:重新定义AI搜索与代理的全能型工具

在当今快速发展的AI技术领域,搜索工具正在经历前所未有的变革。Genspark,这家由前百度高管景鲲和朱凯华创立的AI公司,为我们带来了全新的AI代理引擎体验。作为一位专注于AI工具分享的博主,今天我将为大家详细介绍这款强大的工具&a…...

深入理解设计模式之模板方法模式 1d87ab8b42e98069b6c2c5a3d2710f9a

深入理解设计模式之模板方法模式 深入理解设计模式之模板方法模式 在软件开发的漫长征程中,我们常常会遇到各种复杂的业务逻辑,其中部分逻辑具有相似的流程框架,但在具体细节上又有所不同。这种情况下,模板方法模式就如同一位得…...

Cursor + MCP,实现自然语言操作 GitLab 仓库

本分分享如何使用 cursor mcp 来操作极狐GitLab 仓库,体验用自然语言在不接触极狐GitLab 的情况下来完成一些仓库操作。 极狐GitLab 是 GitLab 在中国的发行版,关于中文参考文档和资料有: 极狐GitLab 中文文档极狐GitLab 中文论坛极狐GitL…...

)

界面开发框架DevExpress XAF实践:如何在Blazor项目中集成.NET Aspire?(一)

DevExpress XAF是一款强大的现代应用程序框架,允许同时开发ASP.NET和WinForms。DevExpress XAF采用模块化设计,开发人员可以选择内建模块,也可以自行创建,从而以更快的速度和比开发人员当前更强有力的方式创建应用程序。 .NET As…...

【C++】特化妙技与分文件编写 “雷区”

目录 目录非类型模板参数非类型模板参数vs宏代换 模板的特化函数模板的特化函数模板特化的坑 类模板特化全特化偏特化 模板分离编译原理解决方案 end 目录 非类型模板参数 模板参数可分为类型形参和非类型形参。 类型形参: 出现在模板参数列表中,跟在…...

qt+mingw64+cmake+libqrencode项目编译和搭建成功记录

最近要使用高拍仪拍照获取照片,然后识别照片中的二维码数据、使用QZxing只能识别出一个条码、另外一个条码准备测试用其他的开源项目(如libqrencode-4.1.1)来进行测试,故进行本文的项目环境搭建测试,最后成功。 本机开…...

观察者设计模式详解:解耦通知机制的利器

在面向对象设计中,设计模式为我们提供了通用的解决方案,以应对常见的开发问题。观察者设计模式是其中非常经典且实用的一种模式,广泛应用于GUI系统、事件处理、消息推送等场景。今天,我们就深入探讨观察者模式的概念、结构和特点&…...

Vim使用完全指南:从基础到高效编辑

Vim使用完全指南:从基础到高效编辑 一、Vim简介与基本概念 Vim(Vi IMproved)是从vi发展出来的一个功能强大的文本编辑器,以其高效性和灵活性著称,特别适合程序开发和系统管理任务。与常规文本编辑器不同,…...

C语言——数组

在C语言中,数组是一组相同类型元素的集合,并且每个数据都有自己对应的一个序号,我们称之为数组下标或者索引。接下来我们就来看看数组是如何定义的吧! 目录 1.一维数组 1.1 定义与初始化 1.2 一维数组的使用 1.3 一维数组在内…...