UG471 之 SelectIO 逻辑资源

背景

《ug471》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、Introduction

- 2、ILOGIC Resources

- 2.1、Combinatorial Input Path

- 2.2、Input DDR Overview (IDDR)

- 2.2.1、OPPOSITE_EDGE 模式

- 2.2.2、SAME_EDGE 模式

- 2.2.3、SAME_EDGE_PIPELINED 模式

- 2.3、Input DDR Resources (IDDR)

- 3、Input Delay Resources (IDELAY)

- 3.1、IDELAY Modes

- 3.2、IDELAY Timing

- 3.3、补充:波形图

- 4、IDELAYCTRL

- 4.1、IDELAYCTRL Overview

- 4.2、IDELAYCTRL Timing

- 4.3、IDELAYCTRL Locations

- 5、OLOGIC Resources

- 5.1、Output DDR Overview (ODDR)

- 5.1.1、OPPOSITE_EDGE 模式

- 5.1.2、SAME_EDGE 模式

- 5.2、Clock Forwarding

- 5.3、Output DDR Primitive (ODDR)

- 6、Output Delay Resources (ODELAY)—Not Available in HR Banks

- 6.1、ODELAY Modes

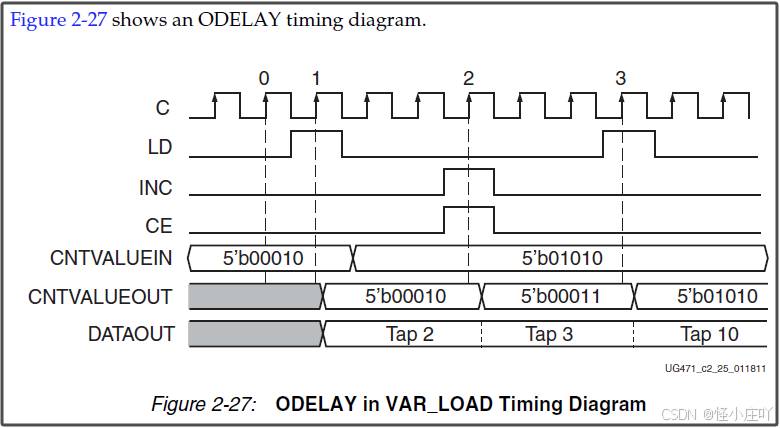

- 6.2、ODELAY Timing

- 6.3、补充:波形图

- 7、参考文献

前言

本文对应的是《ug471_7Series_SelectIO.pdf》的第 2 章 < SelectIO Logic Resources > 部分,是对7系列FPGA的所带有的I/O逻辑资源的一个概述与介绍。

1、Introduction

7系列FPGA的基本I/O逻辑资源,包括以下内容:

• Combinatorial input/output

• 3-state output control

• Registered input/output

• Registered 3-state output control

• Double-Data-Rate (DDR) input/output

• DDR output 3-state control

• IDELAY provides users control of an adjustable, fine-resolution delay taps

• ODELAY provides users control of an adjustable, fine-resolution delay taps

• SAME_EDGE output DDR mode

• SAME_EDGE and SAME_EDGE_PIPELINED input DDR mode

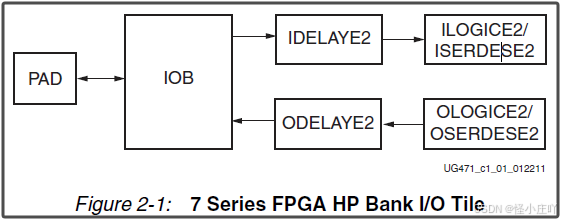

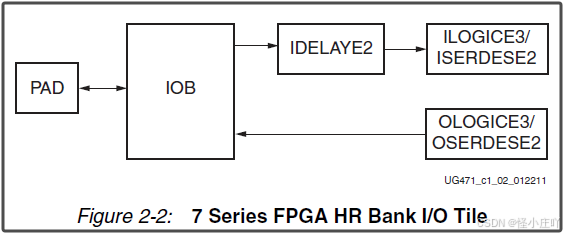

图2-1,展示了1.8V HP Bank 的一个 I/O Tile。

图2-2,展示了3.3V HR Bank 的一个 I/O Tile。

SelectIO™输入、输出和三态驱动器,都位于输入/输出缓冲器(input/output buffer,IOB)中。

HP Bank 有独立的IDELAY和ODELAY模块。HR Bank 的逻辑元素与 HP Bank 相同,只是缺少ODELAY模块。

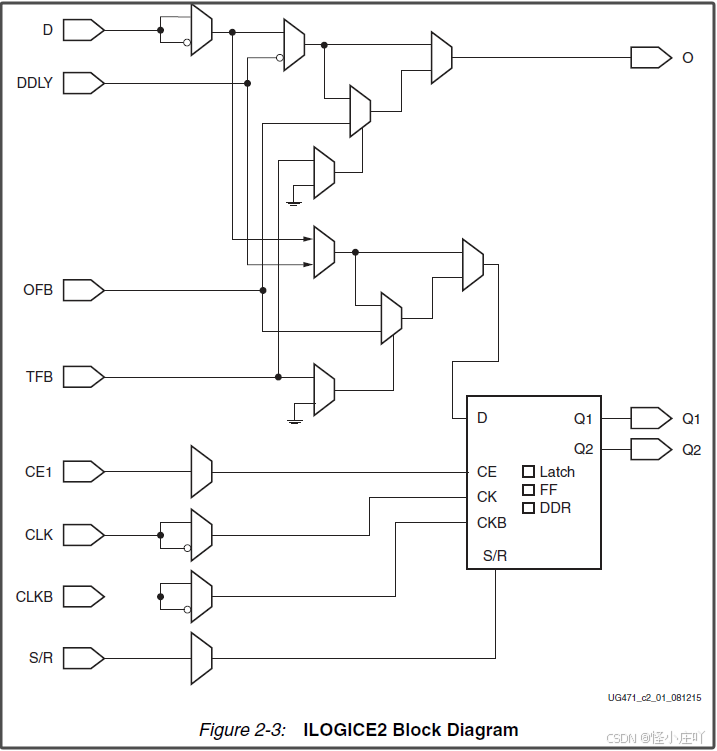

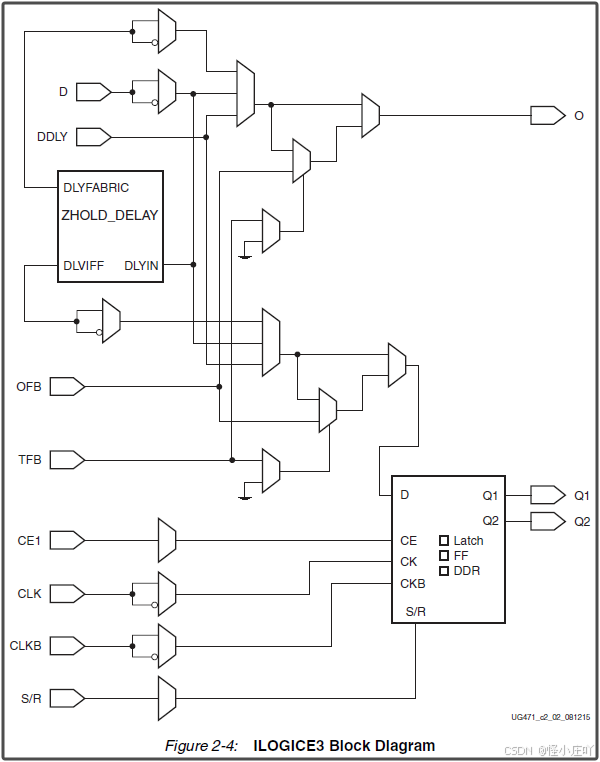

2、ILOGIC Resources

ILOGIC 模块与 输入/输出模块(I/O blockIOB)相邻,包含用于捕获通过 IOB 进入 FPGA 的数据的同步元件(synchronous elements)。

7 系列器件中的 ILOGIC 配置类型包括 ILOGICE2(HP I/O bank)和 ILOGICE3(HR I/O bank)。二者功能及端口完全一致,区别仅在于:

• ILOGICE3位于 HR bank,包含零保持延迟元件(zero hold delay element,ZHOLD)。

• ILOGICE2位于 HP bank,不含 ZHOLD 元件。

• 这些差异如图 2-3 和图 2-4 所示。

输入/输出互连(input/output interconnect,IOI)存储元件 D输入端 上的 ZHOLD 延迟,会自动匹配内部时钟分配延迟,可消除焊盘之间的保持时间要求,使之为零。ILOGIC 模块支持在输入端配置可选的静态未补偿(an optional static uncompensated)零保持(zero hold,ZHOLD)延迟线(delay line),用于补偿时钟插入延迟(clock insertion delays)。当时钟路径直接来自同一 Bank 或相邻 Bank 的 BUFG/BUFGCE 时,ZHOLD功能可经过优化用于补偿时钟插入延迟。除非时钟源为 MMCM 或 PLL,亦或在 Xilinx设计约束(XDC)中设置了 IOBDELAY 属性,ZHOLD 默认启用。重要提示:ZHOLD 并非适用于所有应用场景,需查阅时序报告以确认其对特定时钟方案的影响。

ILOGICE2 和 ILOGICE3 并非可实例化的原语。在布局布线后,如输入触发器(input flip-flop,IFD)或 IDDR(input DDR)等用户实例化的元件,则会被包含在ILOGICE2 或 ILOGICE3中。

ILOGIC 可支持以下操作:

• 边沿触发的 D 型触发器

• IDDR 模式(OPPOSITE_EDGE 或 SAME_EDGE 或 SAME_EDGE_PIPELINED)

• 电平敏感锁存器

• 异步 / 组合逻辑

ILOGIC 模块的寄存器具有一个公共的时钟使能信号(CE1),默认情况下为高电平有效。如果未连接该信号,任何存储元件的时钟使能引脚将默认为有效状态。ILOGIC 模块的寄存器有一个通用的同步或异步 置位和复位信号(SR 信号)。置位/复位 输入引脚 SR 会将存储元件强制设置为 SRVAL 属性所指定的状态。复位条件优先于置位条件。在 ILOGIC 模块中,可以为每个存储元件单独设置 SRVAL 属性,但对于同步或异步置位 / 复位(SRTYPE)的选择,却不能为 ILOGIC 模块中的每个存储元件单独进行设置。

博客在 《xilinx原语介绍及仿真之IDDR》中有进行ILOGICE的寄存器(IFD)使用的说明,并在有如下结论:

2.1、Combinatorial Input Path

组合输入路径,Combinatorial Input Path,组合输入路径用于在输入驱动器和 FPGA 逻辑之间建立直接连接。

在以下情况下,软件会自动使用该路径:

• 从输入数据到 FPGA 逻辑中的逻辑资源存在直接(未寄存)的连接。

• 将软件映射指令 “ pack I/O register/latches into IOBs ” 设置为 “OFF” 状态。

2.2、Input DDR Overview (IDDR)

7系列器件在 ILOGIC 模块中配备了专用寄存器,用于实现输入双倍数据速率(DDR)寄存器功能。通过实例化 IDDR 原语来使用这一功能。

当不使用IDDR功能时,在使用IDDR原语后,只需要添加(IOB == “TRUE”)原语,就可以使用ILOGICE中的触发器(FF)的功能。 这个触发器相比FPGA内部触发器更靠近FPGA管脚,使得建立时间余量更大,更有利于时序。(《xilinx原语介绍及仿真之IDDR》)

所有输入到 I/O tile 的时钟均采用全多路复用方式(fully multiplexed),即 ILOGIC 模块和 OLOGIC 模块之间不共享时钟。IDDR 原语支持以下工作模式:

• OPPOSITE_EDGE 模式

• SAME_EDGE 模式

• SAME_EDGE_PIPELINED 模式

SAME_EDGE模式 和 SAME_EDGE_PIPELINED模式 允许设计人员在 ILOGIC 模块内将下降沿数据转移到上升沿域,从而节省可配置逻辑块(CLB)和时钟资源,并提高性能。上述这些模式,通过 DDR_CLK_EDGE 属性来实现。

2.2.1、OPPOSITE_EDGE 模式

传统DDR 的 OPPOSITE_EDGE模式,是通过 ILOGIC 模块中的单个输入来实现的。上升沿、下降沿均采样:在时钟的上升沿,数据通过输出 Q1 传输至 FPGA 逻辑;在时钟的下降沿,数据则通过输出 Q2 传输至 FPGA 逻辑。且,输出相较于输入要延一拍。

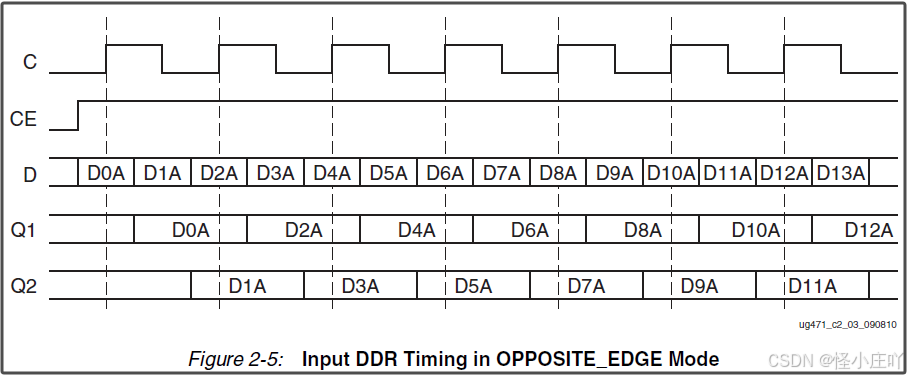

图 2-5 展示了 IDDR 在 OPPOSITE_EDG模式 下的时序图。

2.2.2、SAME_EDGE 模式

在 SAME_EDGE 沿模式下,数据会在同一个时钟边沿被送入FPGA逻辑。

输出结果,与OPPOSITE_EDGE 模式相比,差别在于数据对齐了,但错开了一位。

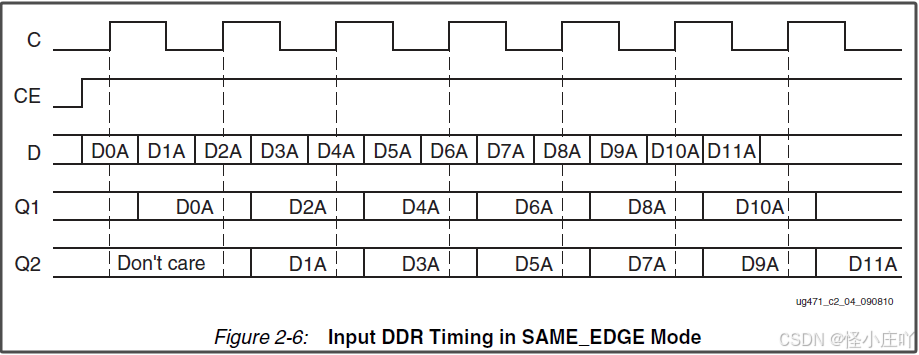

图2-6,展示 SAME_EDGE模式 下的IDDR时序图。在时序图中,输出对Q1和Q2不再是(0)和(1)。而是,第一对出现的是Q1(0)和Q2(don’t care),接着在下一个时钟周期出现的是(1)和(2)。

2.2.3、SAME_EDGE_PIPELINED 模式

在 SAME_EDGE_PIPELINED 模式下,数据在同一个时钟边沿被传输到 FPGA 逻辑中。

与 SAME_EDGE 模式不同的是,数据对不再被一个时钟周期分隔开。然而,为了消除 SAME_EDGE 模式中的时钟周期分隔效应(separated effect),需要额外的时钟延迟。

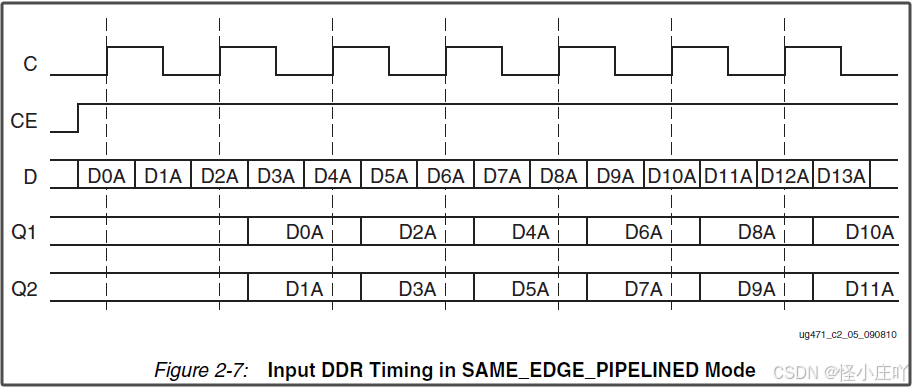

图 2-7, 展示了 IDDR 在 SAME_EDGE_PIPELINED 模式下的时序图。输出对 Q1 和 Q2 会同时被传输到 FPGA 逻辑中。

2.3、Input DDR Resources (IDDR)

- IDDR primitive

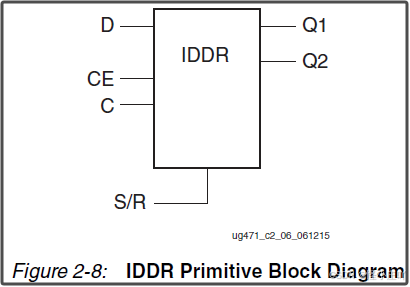

图2-8,展示了 IDDR 原语。其中,Set 和 Reset 不能同时断言。

3、Input Delay Resources (IDELAY)

Every I/O block contains a programmable delay primitive called IDELAYE2. The IDELAY can be connected to an ILOGICE2/ISERDESE2 or ILOGICE3/ISERDESE2 block.

IDELAYE2 is a 31-tap, wraparound, delay primitive with a calibrated tap resolution. Refer to the 7 series FPGA data sheets for delay values. It can be applied to the combinatorial input path, registered input path, or both. It can also be accessed directly from the FPGA logic. IDELAY allows incoming signals to be delayed on an individual input pin basis. The tap delay resolution is contiguously calibrated by the use of an IDELAYCTRL reference clock from the range specified in the 7 series FPGA data sheets.

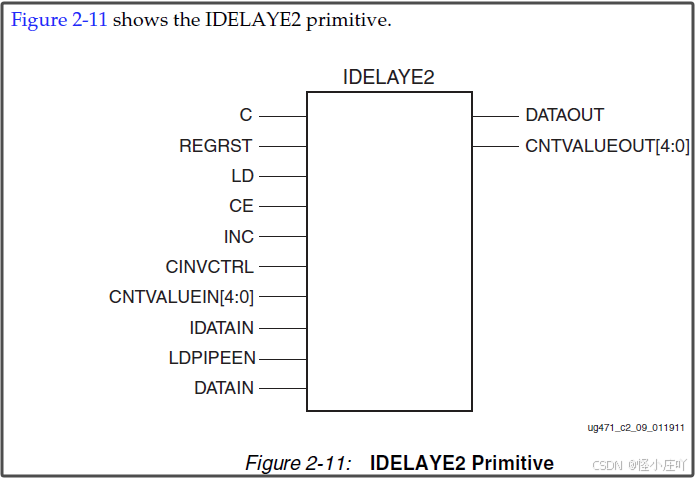

- IDELAYE2 primitive

3.1、IDELAY Modes

当用作输入延迟(IDELAY)时,数据输入可来自输入缓冲器(IBUF)或 FPGA 逻辑,输出则连接至 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2 模块。它有以下几种工作模式可供选择:

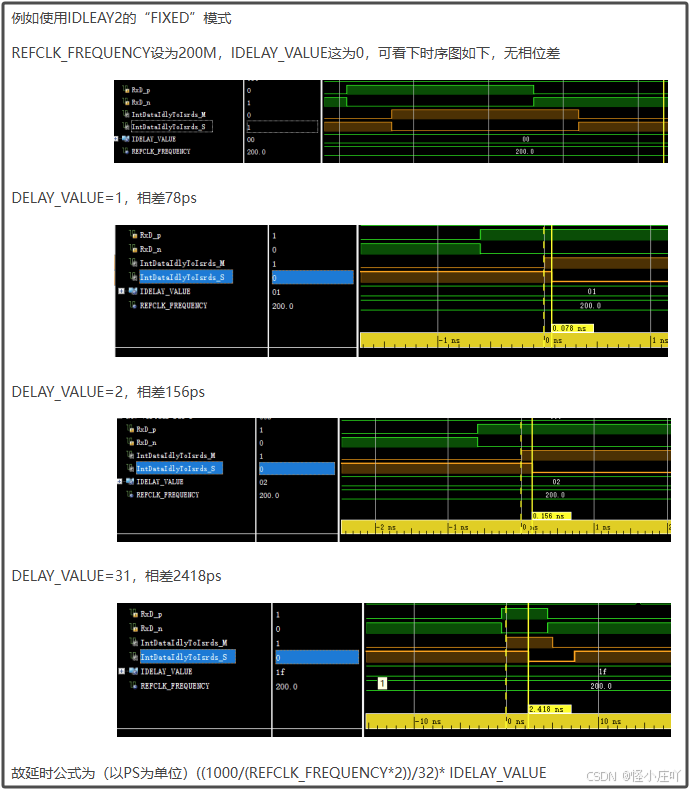

- Fixed delay mode( IDELAY_TYPE=FIXED )

在 fixed delay mode 下,延迟值在配置时根据 IDELAY_VALUE 属性确定的抽头编号(tap number)进行预设。一旦完成配置,该值便无法更改。使用此模式时,必须实例化 IDELAYCTRL 原语。

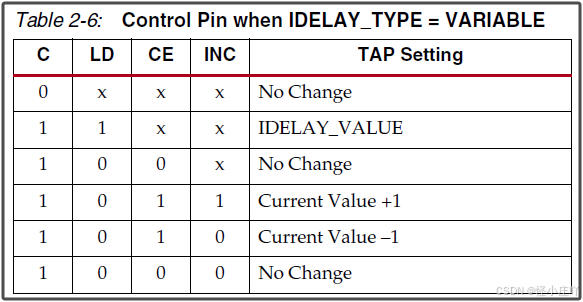

- Variable delay mode( IDELAY_TYPE=VARIABLE )

在 variable delay mode下,延迟值可以在配置完成后可通过操控控制信号 CE 和 INC 来改变。使用此模式时,同样必须实例化 IDELAYCTRL 原语。

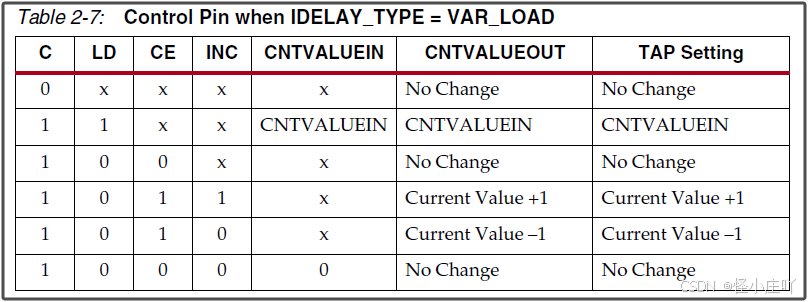

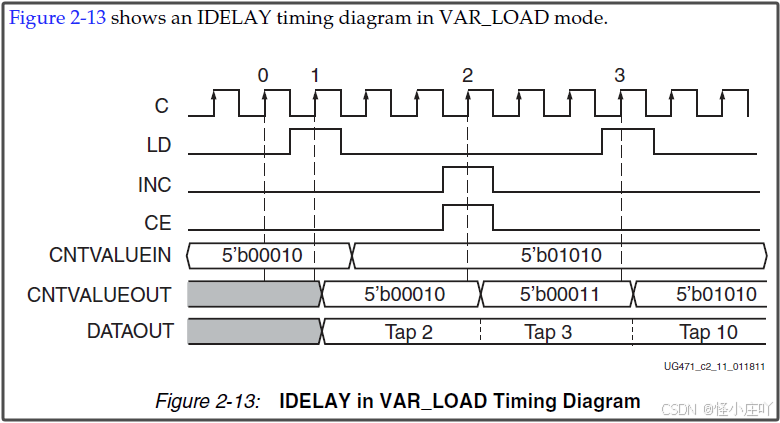

- Loadable variable mode( IDELAY_TYPE=VAR_LOAD )

在此模式下,除了具备与 Variable delay mode( IDELAY_TYPE=VARIABLE ) 相同的功能外,还可通过来自 FPGA 逻辑的 5 位输入 CNTVALUEIN[4:0] 加载 IDELAY 的 tap 。当 LD 引脚出现脉冲时,CNTVALUEIN[4:0] 上的值将成为新的 tap value 。使用此模式时,必须实例化 IDELAYCTRL 原语。

VAR_LOAD模式与VARIABLE模式相似,区别在于 VARIABLE模式为高电平时,是加载IDELAY_VALUE的值到内部作为延时数据,而VAR_LOAD模式在LD为高电平时,加载输入信号CNTVALUEIN的值作为内部新的延时数据。(《xilinx原语介绍及仿真之IDELAYE2 & IDELAYCTRL》)

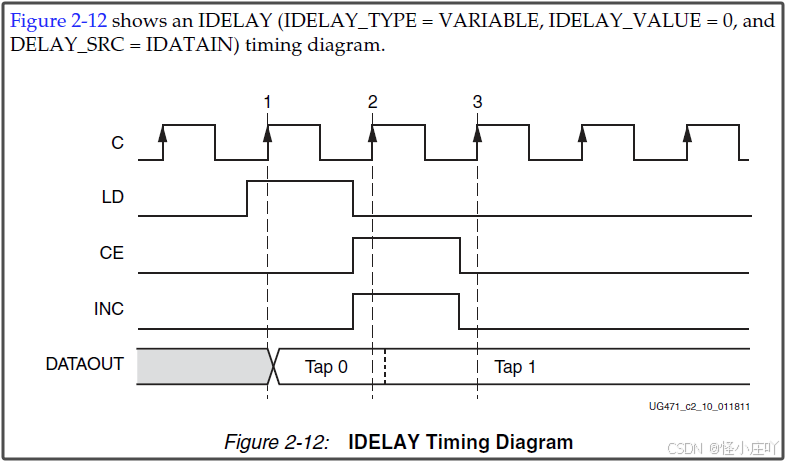

3.2、IDELAY Timing

3.3、补充:波形图

在《7系列selectio之DELAYE相关》中,看到这样一个波形,就直接截图给诸位道友展示了。请原谅笔者有些懒,没有自己跑仿真。

4、IDELAYCTRL

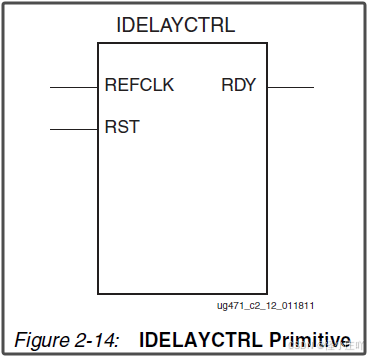

4.1、IDELAYCTRL Overview

如果实例化了 IDELAYE2 或 ODELAYE2 原语,那么也必须实例化 IDELAYCTRL 模块。 IDELAYCTRL 模块会持续校准其所在区域内的各个 delay taps(IDELAY/ODELAY),以降低工艺、电压和温度变化带来的影响。IDELAYCTRL 模块会使用用户提供的参考时钟(REFCLK)来校准 IDELAY 和 ODELAY。

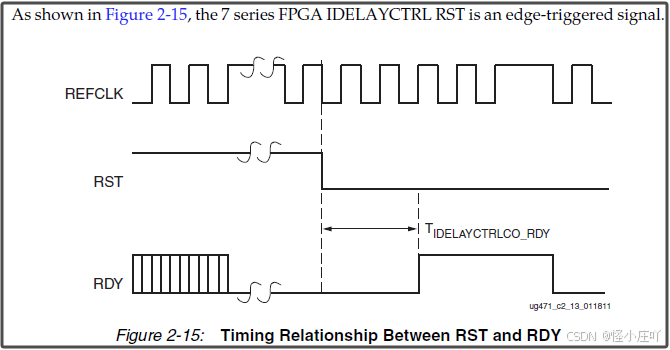

- RST - Reset

RST 为高电平有效异步复位信号。复位释放后延时一段时间将RDY信号拉高表示复位完成。

To ensure proper IDELAY and ODELAY operation, IDELAYCTRL must be reset after configuration and the REFCLK signal is stable. A reset pulse width TIDELAYCTRL_RPW is required.

- REFCLK - Reference Clock

REFCLK 为 IDELAYCTRL 提供时间基准,用于校准同一区域内所有 IDELAY 和 ODELAY 模块。

该时钟必须由 BUFG 或 BUFH 驱动,且设定值也不是可以随意给的,要求是 190-210、 290-310、390-410 这三个范围之间。

REFCLK must be FIDELAYCTRL_REF ± the specified ppm tolerance (IDELAYCTRL_REF_PRECISION) to guarantee a specified IDELAY and ODELAY resolution ( TIDELAYRESOLUTION ). REFCLK can be supplied directly from a user-supplied source or the MMCM and must be routed on a global clock buffer.

- RDY - Ready

RDY 表示 IDELAY 和 ODELAY 模块已完成校准。若 REFCLK 保持高电平或低电平超过一个时钟周期,RDY 信号将置为无效(低电平)。若 RDY 无效(低电平),则必须重新复位 IDELAYCTRL 模块。

The implementation tools allow RDY to be unconnected/ignored.

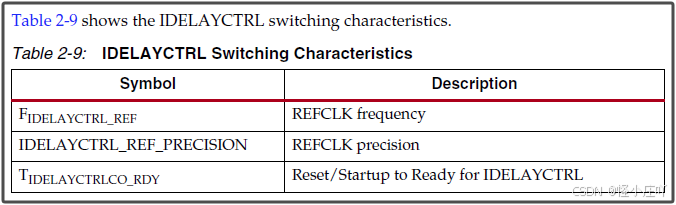

4.2、IDELAYCTRL Timing

4.3、IDELAYCTRL Locations

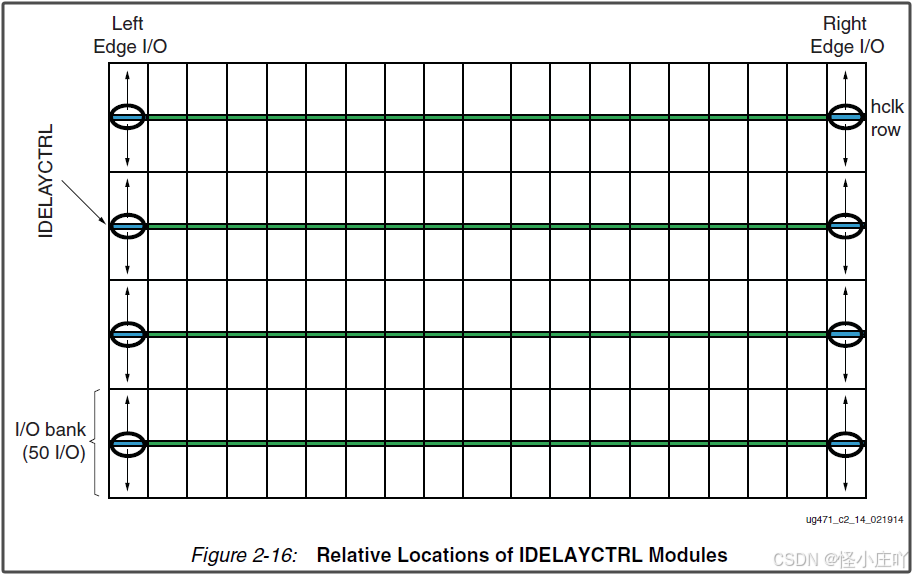

在每个时钟区域的每一 I/O 列中都存在 IDELAYCTRL 模块。一个 IDELAYCTRL 模块会对其所在时钟区域内的所有 IDELAYE2 和 ODELAYE2 模块进行校准。

图2-16,展示了IDELAYCTRL模块在FPGA架构中的相对位置。

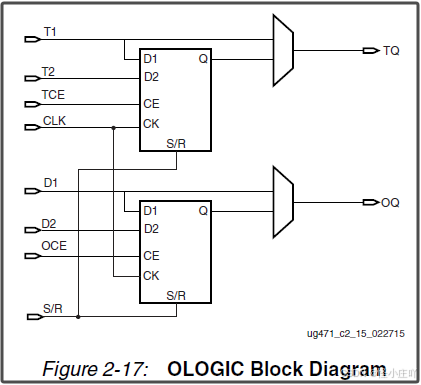

5、OLOGIC Resources

OLOGIC 模块靠近 I/O block( IOB )。OLOGIC 是一个专用的同步模块,用于通过 IOB 将数据从 FPGA 中输出。

OLOGIC 资源的类型包括 OLOGICE2(HP I/O banks)和 OLOGICE3(HR I/O banks)。

OLOGICE2 和 OLOGICE3 并非原语,不能被实例化。在布局布线之后,它们包含用户实例化的元件,比如 output flip-flop(OFD)或 output DDR element(ODDR)。

OLOGIC 由两个主要模块组成,一个用于配置输出数据路径,另一个用于配置三态控制路径。这两个模块有一个公共时钟(CLK),但使能信号不同,分别是 OCE 和 TCE。两者都具有由独立的 SRVAL 属性控制的异步和同步置位与复位(S/R 信号)功能。

输出路径和三态路径可以被独立配置为以下模式之一:

• 边沿触发的 D 型触发器

• DDR模式(SAME_EDGE 或 OPPOSITE_EDGE)

• 电平敏感锁存器

• 异步 / 组合逻辑

图 2-17,展示了 OLOGIC 模块中的各种逻辑资源。

- Combinatorial Output Data and 3-State Control Path

组合输出路径在 FPGA 逻辑与输出驱动器或输出驱动器控制之间建立直接连接。在以下情况下,软件会自动使用这些路径:

• 从 FPGA 逻辑中的逻辑资源到输出数据或三态控制存在直接(未寄存)的连接。

• “ pack I/O register/latches into IOBs ” 这一软件映射指令设置为 “关闭(OFF)” 状

5.1、Output DDR Overview (ODDR)

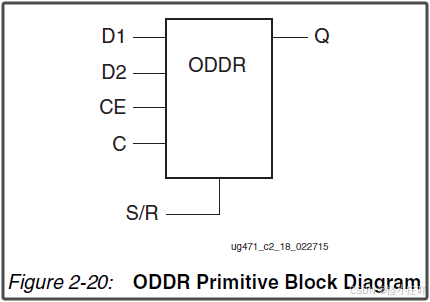

ODDR位于OLOGIC中,把FPGA内部逻辑中的单沿传输信号转换为双沿传输信号,输出给ODELAYE或者PAD。(《xilinx原语详解及仿真之ODDR》)

7 系列器件在 OLOGIC(输出逻辑)模块中设有专用寄存器,用于实现 ODDR 寄存器功能。通过实例化 ODDR 原语即可使用该功能。使用 OLOGIC 时,DDR 多路复用会自动进行,无需手动控制多路选择,该控制信号由时钟生成。

ODDR 原语只有一个时钟输入,下降沿数据由输入时钟的本地反相时钟驱动。所有输入到 I/O tile 的时钟均采用全多路复用方式(fully multiplexed),即 ILOGIC 模块和 OLOGIC 模块之间不存在时钟共享。ODDR 原语支持以下工作模式:

• OPPOSITE_EDGE 模式

• SAME_EDGE 模式

SAME_EDGE模式 允许设计人员在 ODDR时钟 的上升沿将两个数据输入都提供给 ODDR 原语,从而节省了可配置逻辑块(CLB)和时钟资源,并提升了性能。此模式通过 DDR_CLK_EDGE 属性实现,同时也支持三态控制。

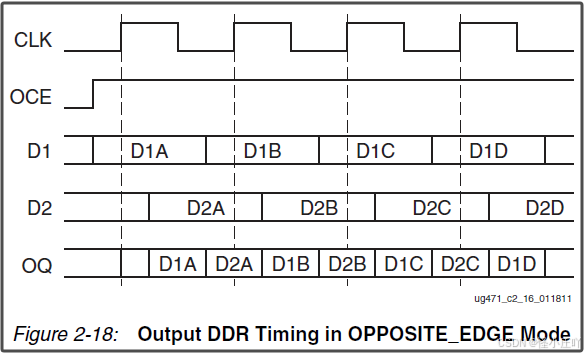

5.1.1、OPPOSITE_EDGE 模式

在 OPPOSITE_EDGE模式下,时钟(CLK)的上升沿和下降沿都被用于以两倍的数据传输速率捕获来自 FPGA 逻辑的数据。输出端的数据都会被传输到 IOB 的数据输入端或三态控制输入端。

如图 2-18 ,展示了在OPPOSITE_EDGE模式下的 output DDR 时序图。

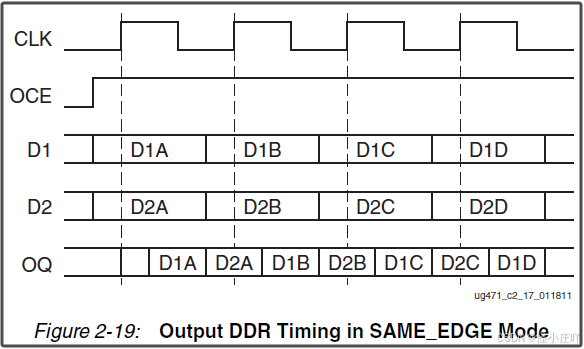

5.1.2、SAME_EDGE 模式

在 SAME_EDGE模式 下,数据可以在同一个时钟边沿被传输至 IOB 。在同一个时钟边沿将数据传输至 IOB,可避免出现建立时间违规的情况,并且与使用 CLB 寄存器相比,用户能够以最小的寄存器到寄存器延迟实现更高的 DDR 频率。

图 2-19 ,展示了SAME_EDGE 模式下的输出 DDR 时序图。

5.2、Clock Forwarding

Output DDR 可以将时钟的一个副本转发到输出端。这对于以相同延迟传播时钟信号和 DDR 数据,以及在每个时钟负载都有独立时钟驱动器的多时钟生成场景中非常有用。实现方法是将 ODDR 原语的 D1 输入端置为高电平,D2 输入端置为低电平。Xilinx 建议采用这种方案将时钟从 FPGA 逻辑转发至输出引脚。

5.3、Output DDR Primitive (ODDR)

6、Output Delay Resources (ODELAY)—Not Available in HR Banks

每个 HP I/O block 包含一个名为 ODELAYE2 的可编程绝对延迟原语。该 ODELAY 可连接至 OLOGICE2/OSERDESE2 模块。

ODELAY is a 31-tap,wraparound, delay primitive with a calibrated tap resolution.

它可应用于组合输出路径或寄存输出路径,也可直接从 FPGA 逻辑进行访问。ODELAY 允许对输出信号按单个信号进行延迟处理。通过从 7 系列 FPGA 数据手册规定的范围内选择 IDELAYCTRL 参考时钟,可调整 tap delay resolution 。

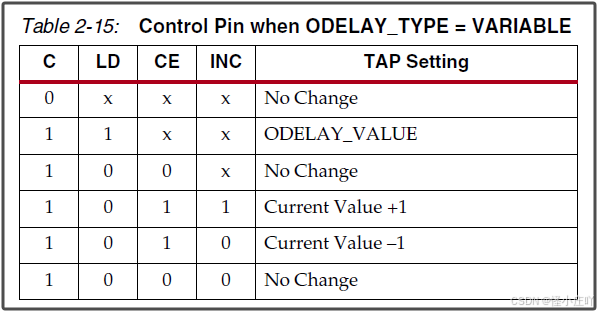

6.1、ODELAY Modes

当用作 ODELAY 时,数据输入来自 IBUF 或 FPGA 逻辑,输出则连接 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2。ODELAY 提供以下几种操作模式:

- Fixed delay mode( ODELAY_TYPE = FIXED )

在 fixed delay mode 下,延迟值在配置时根据 ODELAY_VALUE 属性确定的 tap number进行预设。一旦完成配置,该值便无法更改。使用此模式时,必须实例化 IDELAYCTRL 原语。

- Variable delay mode( ODELAY_TYPE = VARIABLE )

在 variable delay mode 下,配置完成后,可通过操控控制信号 CE 和 INC 来改变延迟值。使用此模式时,必须实例化 IDELAYCTRL 原语。

- Loadable variable delay mode (ODELAY_TYPE = VAR_LOAD)

在此模式下,除具备与 ODELAY_TYPE = VARIABLE 相同的功能外,还可通过来自 FPGA 逻辑的 5 位输入 CNTVALUEIN[4:0] 加载 ODELAY 的 tap。当 LD 引脚出现脉冲时,CNTVALUEIN<4:0 > 上的值将成为新的 tap value。由于具备这一功能,ODELAY_VALUE 属性将被忽略。使用此模式时,必须实例化 IDELAYCTRL 原语。

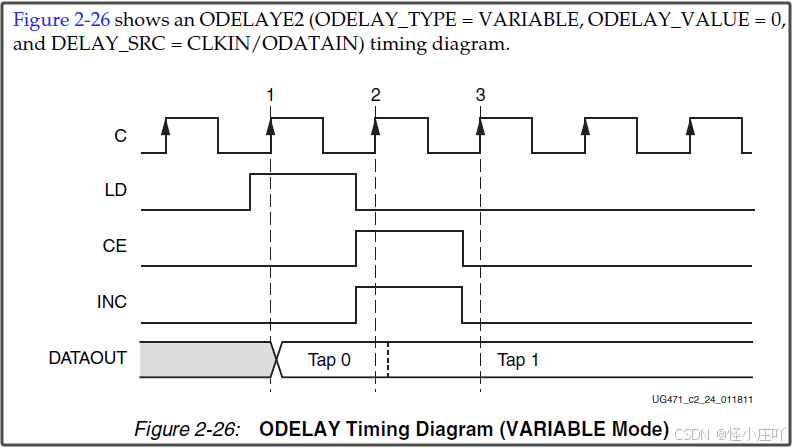

6.2、ODELAY Timing

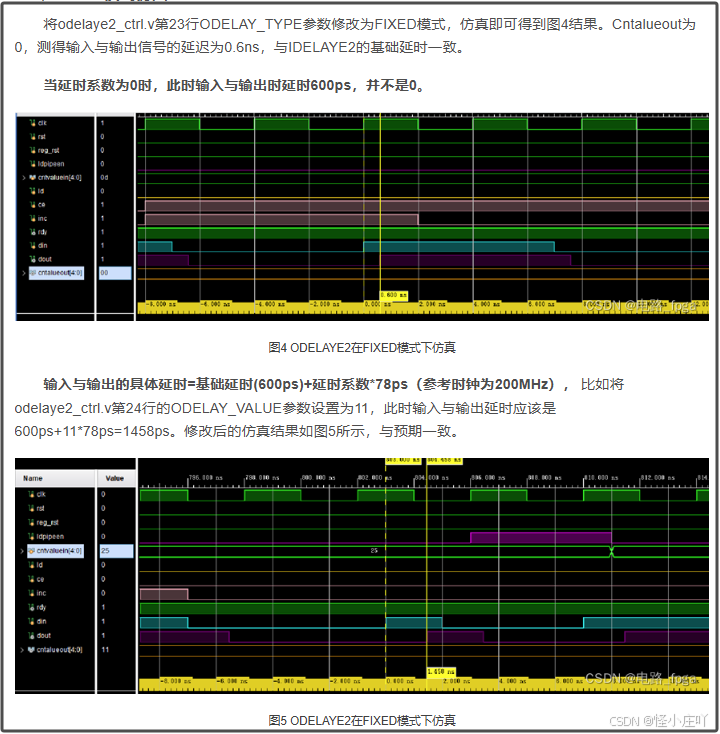

6.3、补充:波形图

但是在《xilinx原语介绍及仿真之ODELAYE2》中,看到了仿真波形,如下图所示。请原谅笔者有些懒,没有自己跑仿真。

7、参考文献

1、《ug471_7Series_SelectIO.pdf》

2、《GMII转RGMII(二)ILOGIC相关原语介绍》

3、《xilinx原语介绍及仿真之IDDR》,这篇也还不错。

4、《xilinx原语介绍及仿真之IDELAYE2 & IDELAYCTRL》

5、《7系列selectio之DELAYE相关》

6、《xilinx原语介绍及仿真之ODELAYE2》,这篇博客里面的仿真做的比较全,诸位道友感兴趣的话,可以去看一看。

7、《xilinx原语详解及仿真之ODDR》

相关文章:

UG471 之 SelectIO 逻辑资源

背景 《ug471》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。 第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。 第 2 章《SelectIO Logic Resources》介绍了输入输出数据…...

基于HISI3519dv500的yolov8-obb车位检测

1. 数据标注 标注软件:roLabelImg 安装方式:见 https://github.com/cgvict/roLabelImg.git 操作指南: 标注后的数据格式如下: <annotation verified"no"><folder>4800</folder><filename>fr…...

)

Prometheus生产实战全流程详解(存储/负载/调度篇)

一、存储架构实战(TSDB深度优化) 1. 存储拓扑设计 2. 关键参数调优 4. 性能压测对照表 二、负载治理实战(百万级Series管控) 三、调度优化实战(精准采集控制) 2. 优先级调度配置 3. 自适应抓取调整 4…...

Mac电脑远程连接window系统服务器

1.下载 首先需要下载Microsoft Remote Desktop软件,下载链接如下: https://go.microsoft.com/fwlink/?linkid868963 2、软件下载成功后,可按照引导程序进行安装,成功后进入软件,可看到如下界面:...

【Qt】编译 Qt 5.15.x For Windows 基础教程 Visual Studio 2019 MSVC142 x64

【Qt】编译 Qt 5.15.x For Windows 基础教程 Visual Studio 2019 MSVC142 x64 目录 【Qt】编译 Qt 5.15.x For Windows 基础教程 Visual Studio 2019 MSVC142 x64准备工作:(必须)第一步:第二步:第三步: 建议…...

触发非本类设置的槽函数)

【Qt】之【Bug】点击按钮(ui->pushButton)触发非本类设置的槽函数

解决 先说解决办法,按钮在ui为默认命名ui->pushButton,后面改了下按钮名为该按钮的功能相关,就不会随意触发其他槽函数了。 没想到是这个原因。。。 可能是之前默认的objectName与旧的槽函数自动连接了 记录一下,找了好久其他的原因。 以…...

buck和boost总结

目录 1. 基本概念与原理 2. 工作模式 3. 典型应用场景 4. Buck-Boost电路:升降压结合 5. 核心区别与选择 1. 基本概念与原理 Buck电路(降压电路) 通过开关器件(如MOSFET)周期性地导通和关断,控制电感充…...

rtsp,。。。。

下面是基于 FFmpeg H.264 RTSP GStreamer 的低延时视频传输方案的详细搭建指南。此方案可将延迟控制在 <100ms,适合远程驾驶、监控等实时性要求较高的应用场景。 📦 方案架构 摄像头(OpenCV)→ FFmpeg(H.264编码…...

微信小程序地图缩放scale隐性bug

bug1 在真机环境下通过this.mapCtx.getScale获取当前地图的缩放等级带小数, 当设置scale带小数时,地图会先执行到缩放到带小数的缩放等级,然后会再次缩放取整的缩放等级(具体向上取整还是向下取整未知,两种情况都观察…...

Java中关于多态的总结

多态是面向对象编程的三大特性之一(封装、继承、多态),它允许不同类的对象对同一消息做出不同的响应。 多态的基本概念 1、定义 多态(Polymorphism)指同一操作作用于不同的对象,可以有不同的解释,产生不同的执行结果…...

突破跨界传输瓶颈:Zynq OCM与DDR核间数据共享性能深度调优

一、当硬件加速遇上内存墙:Zynq数据共享的终极挑战 在某军工雷达信号处理项目中,工程师小王遇到了棘手难题——通过Zynq的ARM核与FPGA协同处理雷达回波数据时,系统吞吐量始终无法突破200MB/s的瓶颈。经过三天三夜的排查,发现问题的根源竟是OCM与DDR之间的数据传输效率不足…...

基于 Ubuntu 24.04 部署 WebDAV

无域名,HTTP 1. 简介 WebDAV(Web Distributed Authoring and Versioning)是一种基于 HTTP 的协议,允许用户通过网络直接编辑和管理服务器上的文件。本教程介绍如何在 Ubuntu 24.04 上使用 Apache2 搭建 WebDAV 服务,无…...

JVM、JRE、JDK的区别

JVM JVM全称Java虚拟机(Java Virtual Machine, JVM),它是运行java字节码的虚拟机,JVM针对不同的系统有不同的实现,目的运行相同的字节码有同样的结果,JVM是“一次编译,到处运行”实现的关键。如下不同的编程语言编译生成字节码文…...

解密火星文:LeetCode 269 题详解与 Swift 实现

文章目录 摘要描述题解答案题解代码分析构建图(Graph)拓扑排序(Topological Sort) 示例测试及结果时间复杂度空间复杂度实际场景类比总结 摘要 这篇文章我们来聊聊 LeetCode 269 题:火星词典(Alien Dictio…...

系统思考:短期困境与长期收益

最近在项目中,一直有学员会提到一个议题,如何平衡当前困境和长期收益? 我的思考是在商业和人生的路上,我们常常听到“鱼和熊掌不可兼得”的说法,似乎短期利益和长期目标注定是对立的。但事实上,鱼与熊掌是…...

K8S - Harbor 镜像仓库部署与 GitLab CI 集成实战

引言 在 Kubernetes 环境中,容器镜像的存储与管理至关重要。企业级镜像仓库(如 Harbor)为团队提供了安全、稳定、可扩展的镜像管理解决方案。 一、Harbor 安装与配置 Harbor 是由 VMware 开源的企业级云原生镜像仓库,它不仅支持…...

2025-05-10-FFmepg库裁切有水印的视频

裁后 代码 import subprocess# 文件路径 input_video_path "bg_video.mp4" output_video_path "output_video_cropped.mp4"# 裁剪视频下方的水印 def crop_video(input_video_path, output_video_path, crop_height):# 获取视频的分辨率def get_video…...

通信协议选型篇:如何根据项目需求选择合适的通信协议?

🧭 本文为《嵌入式通信协议全解析》第七篇,面向系统架构师、嵌入式开发者与技术决策者,提供一套实用的通信协议选型方法论,结合性能对比表、使用案例与决策树,助你在“带宽、功耗、距离、可靠性、生态”之间做出最优权衡。 🔍 一、为什么通信协议的选型很关键? 在嵌入…...

Altera系列FPGA纯verilog视频图像去雾,基于暗通道先验算法实现,提供4套Quartus工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目Altera系列FPGA相关方案推荐本博主已有的图像处理方案 3、设计思路框架工程设计原理框图输入Sensor之-->OV7725摄像头输入Sensor之-->OV5640摄像头输入Sensor之…...

+langchain框架+MCP(大模型上下文协议)+RAG+传统算法等研发数学教学管理与成绩提升系统)

大模型的实践应用39-Qwen3(72B)+langchain框架+MCP(大模型上下文协议)+RAG+传统算法等研发数学教学管理与成绩提升系统

大家好,我是微学AI,今天给大家介绍一下大模型的实践应用39-Qwen3(72B)+langchain框架+MCP(大模型上下文协议)+RAG+传统算法等研发数学教学管理与成绩提升系统。 在2025年AI技术快速发展的背景下,大模型已展现出在教育领域的巨大潜力。通义千问Qwen3作为阿里云推出的最新一代…...

算法)

【强化学习】动态规划(Dynamic Programming, DP)算法

1、动态规划算法解题 LeetCode 931. 下降路径最小和 给你一个 n x n 的 方形 整数数组 matrix ,请你找出并返回通过 matrix 的下降路径 的 最小和 。 下降路径 可以从第一行中的任何元素开始,并从每一行中选择一个元素。在下一行选择的元素和当前行所选…...

【Linux】深入拆解Ext文件系统:从磁盘物理结构到Linux文件管理

目录 1、理解硬件 (1)磁盘 (2)磁盘的物理结构 (3)磁盘的存储结构 (4)磁盘的逻辑结构 (5)CHS && LBA地址 2、引入文件系统 (1&…...

gdb跟踪被调试程序的子线程、子进程)

linux ptrace 图文详解(八) gdb跟踪被调试程序的子线程、子进程

目录 一、gdb跟踪被调试程序的fork、pthread_create操作 二、实现原理 三、代码实现 四、总结 (代码:linux 6.3.1,架构:arm64) One look is worth a thousand words. —— Tess Flanders 相关链接: …...

【列表类型】

1、按索引取值 索引可正向存取,也可反向存取 l [111, paipai, cat] # 正向取值 print(l[1]) # 方向取值 print(l[-1]) # 通过索引给列表重新赋值,前提:索引存在 l[0] ccat print(l) # 索引不存在的情况下,取值or重新赋值的情况下都会报错 …...

)

MySQL 8.0 OCP 英文题库解析(二)

Oracle 为庆祝 MySQL 30 周年,截止到2025.07.31 之前。所有人均可以免费考取 原价245美元的MySQL OCP 认证。 从今天开始,将英文题库免费公布出来,并进行解析,帮助大家在一个月之内轻松通过OCP认证。 本期公布试题6~15。 试题6: …...

》)

数据分析与逻辑思维:六步解决业务难题;参考书籍《数据分析原理:6步解决业务分析难题 (周文全, 黄怡媛, 马炯雄)》

文章目录 一、懂业务:业务背景与逻辑前提1.1 明确业务目标与问题定义1.2 培养批判性思维与高于业务视角 二、定指标:构建科学的指标体系2.1 指标拆解与维度分析2.2 典型指标体系案例:用户与业务视角 三、选方法:匹配业务需求的分析…...

人力资源管理系统如何有效提高招聘效率?

在传统招聘模式下,企业招聘常常陷入 “泥潭”。HR 每天需要花费大量时间在海量简历中 “大海捞针”,手动筛选、电话沟通、安排面试,流程繁琐且效率低下。好不容易邀约到候选人,却因面试安排冲突、信息传递不及时等问题,…...

FAISS 与机器学习、NLP 的关系

FAISS(Facebook AI Similarity Search)是一个用于高效相似性搜索和密集向量聚类的开源库,由 Facebook AI Research 开发。它在机器学习(特别是自然语言处理,NLP)领域中扮演着重要角色,主要解决大…...

文件包含2

远程文件包含与本地文件包含的区别 对比 对比项本地文件包含(LFI)远程文件包含(RFI)定义攻击者包含服务器本地的文件攻击者包含远程服务器(如HTTP/FTP)上的文件依赖条件不需要特殊配置需要allow_url_incl…...

嵌入式系统架构验证工具:AADL Inspector v1.10 全新升级

软件架构建模与早期验证是嵌入式应用的关键环节。架构分析与设计语言(AADL)是专为应用软件及执行平台架构模型设计的语言,兼具文本与图形化的双重特性。AADL Inspector是一款轻量级的独立工具: 核心处理能力包括 √ 支持处理AA…...

软考高级系统架构设计师备考分享:操作系统核心知识点整理

在备战软考高级系统架构设计师的过程中,操作系统作为核心考点之一,需要系统性地掌握其核心原理。本文将从操作系统分类、进程状态模型、同步互斥机制、死锁问题及存储管理五大模块展开梳理,结合考试高频考点和实际案例进行解析。 一、操作系统…...

22、城堡防御工事——React 19 错误边界与监控

一、魔法护盾:错误边界机制 1. 城墙结界(Error Boundary) // 客户端错误边界use client function useErrorBoundary() {const [error, setError] useState(null);const handleError useCallback((error, errorInfo) > {setError(erro…...

有关SOA和SpringCloud的区别

目录 1. 定义 2. 架构风格 3. 技术栈 4. 服务交互 5. 适用场景 前言 面向服务架构(SOA)是一种软件设计风格,它将应用程序的功能划分为一系列松散耦合的服务。这些服务可以通过标准的通信协议进行交互,通常是HTTP或其他消息传…...

大数据——Mac环境DataSpell集成Jupyter

1、设置 2、添加新的解释器 3、解释器类型选择Conda 4、进入选中全部,然后重启 5、dataspell右下角会显示当前项目的运行环境 6、创建Jupyter Notebook文件 7、测试 8、查看当前配置 (1)本地模式安装使用 (2)…...

解锁健康养生新境界

在追求高品质生活的当下,健康养生早已超越 “治未病” 的传统认知,成为贯穿全生命周期的生活艺术。它如同精密的交响乐,需饮食、运动、心理与生活习惯多维度协奏,方能奏响生命的强音。 饮食养生讲究 “顺时、适性”。遵循二十四节…...

WORD压缩两个免费方法

日常办公和学习中,Word文档常常因为包含大量图片、图表或复杂格式而导致文件体积过大,带来诸多不便,比如 邮件发送受限:许多邮箱附件限制在10-25MB,大文件无法直接发送 存储空间占用:大量文档占用硬盘或云…...

的消费者)

Zabbix监控 RabbitMQ 指定消息队列名称(pull_alarms )的消费者

✅ 1. 编写 RabbitMQ 队列监控脚本 创建脚本文件 /usr/local/bin/zbx_rabbitmq_metric.sh 并写入以下内容: #!/bin/bash # /usr/local/bin/zbx_rabbitmq_metric.shQUEUE$1 METRIC$2 USER$3 PASS$4if [[ -z "$QUEUE" || -z "$METRIC" || -z &q…...

RabbitMQ ②-工作模式

RabbitMQ 工作模式 官方提供了七种工作模式 Simple(简单模式) P:生产者,发布消息到队列C:消费者,从队列中获取消息并消费Queue:消息队列,存储消息。 一个生产者,一个…...

《探索React Native社交应用中WebRTC实现低延迟音视频通话的奥秘》

WebRTC,全称为Web Real-Time Communication,是一项开创性的开源技术,为Web和移动应用开启了实时通信的大门。它打破了传统通信的束缚,使得应用之间无需依赖繁琐的中间服务器,就能实现直接的点对点通信,这是…...

UI设计公司兰亭妙微分享:汽车 MHI 设计的界面布局创新法则

在汽车人机界面(MHI)设计中,界面布局犹如建筑蓝图,奠定了用户与汽车交互体验的基础。合理创新的布局能提升驾驶安全性与便捷性,融合极简美学与高效操作则成为现代汽车 MHI 界面布局设计的核心追求。 驾驶场景中&…...

- 递归)

【递归,搜索与回溯算法篇】专题(一) - 递归

文章目录 面试题 08.06. 汉诺塔问题21. 合并两个有序链表206. 反转链表24. 两两交换链表中的节点50. Pow(x, n) 面试题 08.06. 汉诺塔问题 题目链接: 面试题 08.06. 汉诺塔问题 题目描述: 在经典汉诺塔问题中,有 3 根柱子及 N 个不同大小的…...

B站pwn教程笔记-9

前言:可以去一些开源镜像站下载libc老的乌班图镜像,因为堆题的libc可能比较老,没有新的一些保护措施和机制。 格式化字符串漏洞 归根结底,可以读写任意地址内存。 泄露栈数据/任意地址数据 主要问题就是printf不知道自己有没有…...

和 网络摄像机(IPC,IP Camera))

NVR(网络视频录像机) 和 网络摄像机(IPC,IP Camera)

NVR(网络视频录像机) 和 网络摄像机(IPC,IP Camera) 是网络监控系统的两个核心组件,但功能定位完全不同。以下是它们的核心区别: 1. 功能角色 组件网络摄像机(IPC)NVR&a…...

数智读书笔记系列032《统一星型模型--一种敏捷灵活的数据仓库和分析设计方法》

引言 在当今数字化时代,数据仓库作为企业数据管理的核心基础设施,承担着整合、存储和提供企业数据的关键角色。随着商业环境的快速变化和业务需求的日益复杂,数据仓库的设计方法也在不断演进,以适应新的挑战和要求。 背景与意义 数据仓库领域长期存在着两种主流方法论之…...

互联网大厂Java求职面试:基于RAG的智能问答系统设计与实现

互联网大厂Java求职面试:基于RAG的智能问答系统设计与实现 场景背景 在某互联网大厂的技术面试中,技术总监张总正在面试一位名为郑薪苦的求职者。郑薪苦虽然对技术充满热情,但回答问题时总是带着幽默感,有时甚至让人哭笑不得。 …...

和Task.Factory.StartNew()对比(腾讯元宝))

[C#]Task.Run()和Task.Factory.StartNew()对比(腾讯元宝)

Task.Run和Task.Factory.StartNew都是用来创建并启动任务的方法,但它们的内部实现和使用场景有所不同。两者的主要区别:默认调度器、配置选项、异常处理、适用场景。建议用户大多数情况下使用Task.Run,除非需要StartNew的高级配置,…...

游戏数据的缓存简介)

Java游戏服务器开发流水账(3)游戏数据的缓存简介

简介 游戏服务器数据缓存是一种在游戏服务器运行过程中,用于临时存储经常访问的数据的技术手段,旨在提高游戏性能、降低数据库负载以及优化玩家体验。游戏开发中数据的缓存可以使用Java自身的内存也可以使用MemCache,Redis,注意M…...

PostgreSQL可见性映射VM

1.可见性映射 清理过程的代价高昂,为了减小清理的开销,在PostgreSQL 8.4版中引入了VM。 VM的基本概念很简单。 每个表都拥有各自的可见性映射,用于保存表文件中每个页面的可见性。 页面的可见性确定了每个页面是否包含死元组。清理过程可以…...

集成电路流片随笔26:tinyriscv的三级流水线细则pc

include "defines.v"// PC寄存器模块 module pc_reg(input wire clk,input wire rst,input wire jump_flag_i, // 跳转标志input wire[InstAddrBus] jump_addr_i, // 跳转地址input wire[Hold_Flag_Bus] hold_flag_i, // 流水线暂停标志input wire…...

如何解决Jmeter中的乱码问题?

在 JMeter 中遇到乱码问题通常是由于字符编码不一致导致的,常见于 HTTP 请求响应、参数化文件读取、报告生成等场景。以下是系统化的解决方案: 1. HTTP 请求响应乱码 原因: 服务器返回的字符编码(如UTF-8、GBK)与 J…...