蓝桥杯FPGA赛道第二次模拟题代码

一、顶层文件

module test(

input wire sys_clk,

input wire sys_rst,

input wire [3:0]key_in,

output reg [7:0]led,output wire scl,

inout wire sda,//i2c的信号output wire [7:0]sel,

output wire [7:0]seg//数码管的驱动

);wire [23:0] data ;

reg [31:0] dsp_data;

reg [23:0] bcd;wire S1_debounce,S1_debounce_reg;

wire S2_debounce,S2_debounce_reg;

wire S3_debounce,S3_debounce_reg;localparam KEY1_STATE1=2'b00;//停止状态

localparam KEY1_STATE2=2'b01;//启动状态localparam KEY2_STATE1=2'b00;

localparam KEY2_STATE2=2'b01;reg [1:0] key1_state;//当前状态

reg [1:0] key2_state;//当前状态//显示eeprom读取的数据

always @(posedge sys_clk or negedge sys_rst)beginif(!sys_rst)begindsp_data <={4'd11,4'd10,4'd10,4'd10,4'd10,4'd10,4'd10,4'd10};//初始值,表示没有效数字时钟的显示led <=8'b11111111;end else beginif(S1_debounce_reg&&!S1_debounce)beginled[0]<=~led[0];end bcd[7:4]<=data[7:0]/10;bcd[3:0]<=data[7:0]%10;bcd[11:8]<=data[15:8]%10;bcd[15:12]<=data[15:8]/10;bcd[19:16]<=data[23:16]%10;bcd[23:20]<=data[23:16]/10;dsp_data<={4'd11,bcd[23:16],4'd10,bcd[15:8],4'd10,bcd[7:4]};end

end

//按键一的状态

always @(posedge sys_clk or negedge sys_rst)beginif(!sys_rst)begin key1_state<=KEY1_STATE1;end else beginif(S1_debounce_reg&&!S1_debounce) beginkey1_state <= (key1_state ==KEY1_STATE1) ? KEY1_STATE2:KEY1_STATE1;endend

end

//检测按键二的状态

always @(posedge sys_clk or negedge sys_rst)beginif(!sys_rst)begin key2_state<=KEY2_STATE1;end else beginif(S2_debounce_reg&&!S2_debounce) beginkey2_state <= (key2_state ==KEY2_STATE1) ? KEY2_STATE2:KEY2_STATE1;endend

endwire [23:0] rd_data;

wire rd_data_vld;

//reg define

reg [23:0] wr_data;

reg wr_req;

reg rd_req=0;//检测写入EEPROM的条件

always @(posedge sys_clk or negedge sys_rst)beginif(!sys_rst)beginwr_req<=1'b0;end else if({key1_state==KEY1_STATE2&&(S1_debounce_reg&&!S1_debounce)}||{key1_state==KEY1_STATE1&&(S2_debounce_reg && !S2_debounce)})beginwr_data <=data;wr_req <=1'b1;end else wr_req<=1'b0;end reg [3:0] state=0;

reg [15:0] debounce_couter=0;//去抖计数器

reg [15:0] debounce_couter2=0;//去抖计数器//上电读取eeprom的数据always @(posedge sys_clk or negedge sys_rst)beginif(!sys_rst) beginstate <=0;rd_req<=0;debounce_couter <=16'b0;end else begin case(state)0:begin//状态0:等待读取开始state<=1;end 1:begin//状态1;从EEprom读取数据rd_req<=1;if(debounce_couter<=16'hFFFF)debounce_couter <=debounce_couter+1;elsestate <=2;end2:begin//状态2:数据加载完毕//进一步处理逻辑rd_req<=0;debounce_couter<=16'b0;end default:state <=0;endcaseend

end

//eeprom module

eeprom inst_eeprom(.clk(sys_clk),.rst(sys_rst),.wr_req(wr_req),.rd_req((~key_in[2])||rd_req),//read data from EEProm.device_id(),.reg_addr(8'h03),.reg_addr_vld(1'b1),.wr_data(wr_data),.wr_data_vld(wr_req),.rd_data(rd_data),.rd_data_vld(rd_data_vld),.ready(),.scl(scl),.sda(sda)

);

//按键模块

key debounce_L1(

.sys_clk(sys_clk),

.rst(sys_rst),

.key_in(key_in[0]),

.S_debounce(S1_debounce),

.S_debounce_reg(S1_debounce_reg)

);key debounce_L2(

.sys_clk(sys_clk),

.rst(sys_rst),

.key_in(key_in[1]),

.S_debounce(S2_debounce),

.S_debounce_reg(S2_debounce_reg)

);key debounce_L3(

.sys_clk(sys_clk),

.rst(sys_rst),

.key_in(key_in[2]),

.S_debounce(S3_debounce),

.S_debounce_reg(S3_debounce_reg)

);

//时间计数模块

counter_time u_couter_time(

.clk(sys_clk),

.rst_n(sys_rst),

.key_in1(S1_debounce_reg &&!S1_debounce),

.key_in2(S2_debounce_reg &&!S2_debounce),

.key_in3(S3_debounce_reg &&!S3_debounce),

.rd_req(rd_req),

.rd_data(rd_data),

.din_out(data)

);

//数码管显示模块

segdisplay segdisplay_inst(.clk(sys_clk),.rst(sys_rst),.dsp_data(dsp_data),.seg(seg),.sel(sel)

);

endmodule 二、数码管驱动

module segdisplay

(input wire clk ,input wire rst ,input wire [31:0] dsp_data ,output reg [7:0] seg ,//段选端output reg [7:0] sel //位选段

);localparam [7:0] DIGIT0 =8'b1100_0000 ;//16精制C0

localparam [7:0] DIGIT1 =8'b1111_1001 ;//F9

localparam [7:0] DIGIT2 =8'b1010_0100;//A4

localparam [7:0] DIGIT3 =8'b1011_0000;//B0

localparam [7:0] DIGIT4 =8'b1001_1001;//99

localparam [7:0] DIGIT5 =8'b1001_0010;//92

localparam [7:0] DIGIT6 =8'b1000_0010;//82

localparam [7:0] DIGIT7 =8'b1111_1000;//F8

localparam [7:0] DIGIT8 =8'b1000_0000;//80

localparam [7:0] DIGIT9 =8'b1001_0000 ;//90

localparam [7:0] DIGITX =8'b1011_1111 ;//

localparam [7:0] DIGOFF =8'b1111_1111 ;//FF

localparam [7:0] DIGITC =8'hC6 ;

localparam DSP_COUNT = 20'd50000; //reg [19:0] dsp_count ;

reg [3:0] bits ;

reg [3:0] bcd ;//1ms的计数器

always @(posedge clk or negedge rst)begin if(!rst)dsp_count <= 20'd0;else begin if (dsp_count == DSP_COUNT-1) begin dsp_count <= 20'd0;end else dsp_count <= dsp_count + 20'd1;end

end

//位选端

always @(posedge clk or negedge rst) begin if(!rst)beginsel <= 8'b1111_1111;bits <=4'd0;end else begin if(dsp_count==DSP_COUNT-1)begin//每一毫秒更新一次if(bits==4'd8)bits <=4'd0;elsebits<=bits+4'd1;case(bits)4'd0: begin sel<=8'b1111_1110;bcd<=dsp_data[31:28] ;end4'd1: begin sel<=8'b1111_1101;bcd<=dsp_data[27:24] ;end4'd2: begin sel<=8'b1111_1011;bcd<=dsp_data[23:20] ;end4'd3: begin sel<=8'b1111_0111;bcd<=dsp_data[19:16] ;end4'd4: begin sel<=8'b1110_1111;bcd<=dsp_data[15:12] ;end4'd5: begin sel<=8'b1101_1111;bcd<=dsp_data[11:8] ;end4'd6: begin sel<=8'b1011_1111;bcd<=dsp_data[7:4] ;end4'd7: begin sel<=8'b0111_1111;bcd<=dsp_data[3:0] ;enddefault:sel<=8'b1111_1111;endcaseend end

end

//段选端

always @(posedge clk or negedge rst)beginif(!rst)seg<=DIGOFF;else begin case(bcd)4'd0: seg<=DIGIT0;4'd1: seg<=DIGIT1;4'd2: seg<=DIGIT2;4'd3: seg<=DIGIT3;4'd4: seg<=DIGIT4;4'd5: seg<=DIGIT5;4'd6: seg<=DIGIT6;4'd7: seg<=DIGIT7;4'd8: seg<=DIGIT8;4'd9: seg<=DIGIT9;4'd10:seg<=8'b1011_1111;//-4'd11:seg<=8'b1000_1100;//pdefault: seg<=DIGOFF;endcaseend

end

endmodule 三、按键驱动

module key(input wire sys_clk,input wire rst,input wire [0:0] key_in,//按键输入信号,假设最多支持4个按键output reg [0:0] S_debounce,//去抖后的按键输出output reg [0:0] S_debounce_reg //去抖的寄存器输出

);reg [15:0] debounce_counter;//去抖计数器//按键去抖模块

always @(posedge sys_clk or negedge rst)beginif(!rst)beginS_debounce<=0;S_debounce_reg<=0;debounce_counter<=16'b0;end else begin//针对每个按键经行去抖if(key_in==1'b0)begin//按键按下if(debounce_counter< 16'hFFFF)debounce_counter<=debounce_counter+1;elseS_debounce_reg<=1'b1;//该按键去抖确认按下end else begindebounce_counter<=16'b0;S_debounce_reg<=1'b0;//按键松开endend//更新去抖后的按键输出S_debounce <=S_debounce_reg;end

endmodule四、计数器模块

module counter_time(

input wire clk,

input wire rst_n,

input wire key_in1,//消抖后的脉冲信号,高有效

input wire key_in2,//消抖后的脉冲信号,高有效

input wire key_in3,//消抖后的脉冲信号,高有效

input wire [23:0]rd_data,

input wire rd_req,

output wire [23:0]din_out//输出当前计数值

);parameter MAX_1MS=16'd49_999;//1ms

parameter MAX_1S=10'd999;//1ms*1000=1s

parameter MAX_1MIN=6'd59;//1s*60=1min

parameter MAX_1H=6'd59;//1min*60=1hreg flag;//开始、暂停结束信号

reg [15:0]cnt_1ms;

wire add_cnt_1ms;

wire end_cnt_1ms;reg [9:0]cnt_1s;

wire add_cnt_1s;

wire end_cnt_1s;reg [5:0]cnt_1min;

wire add_cnt_1min;

wire end_cnt_1min;reg [5:0]cnt_1h;

wire add_cnt_1h;

wire end_cnt_1h;reg [7:0] data_min;//保存此时有多少分钟

reg [7:0] data_s;//保存此时有多少秒

reg [7:0] data_ms;//保存此时有多少毫秒,只取高两位//flag

always @(posedge clk or negedge rst_n)beginif(!rst_n)beginflag<=1'b0;endelse if(key_in1) beginflag<=~flag;endelse beginflag<=flag;endend

//1ms计数器

always @(posedge clk or negedge rst_n or posedge key_in2) beginif(!rst_n||key_in2)begincnt_1ms<=16'd0;end else if(add_cnt_1ms)beginif(end_cnt_1ms)begincnt_1ms<=16'd0;end else begincnt_1ms<=cnt_1ms+1'b1;endend

end assign add_cnt_1ms=flag;

assign end_cnt_1ms=add_cnt_1ms&&{cnt_1ms==MAX_1MS};//1S计数器

always @(posedge clk or negedge rst_n ) beginif(!rst_n)begincnt_1s<=10'd0;end else if(key_in3||rd_req)begincnt_1s<=rd_data[7:0]*10;endelse if(key_in2)begincnt_1s<=0;endelse if(add_cnt_1s)beginif(end_cnt_1s)begincnt_1s<=10'd0;endelse begincnt_1s<=cnt_1s+1'b1;endend

end assign add_cnt_1s=end_cnt_1ms;

assign end_cnt_1s=add_cnt_1s&&cnt_1s==MAX_1S;//1min计数器

always @(posedge clk or negedge rst_n or posedge key_in2) beginif(!rst_n||key_in2)begincnt_1min<=6'd0;end else if(key_in3||rd_req)begincnt_1min<=rd_data[23:16];endelse if(add_cnt_1min)beginif(end_cnt_1min)begincnt_1min<=6'd0;endelse begincnt_1min<=cnt_1min+1'b1;endend

end assign add_cnt_1min=end_cnt_1s;

assign end_cnt_1min=add_cnt_1min&&cnt_1s==MAX_1MIN;

//1H计数器

always @(posedge clk or negedge rst_n or posedge key_in2) beginif(!rst_n||key_in2)begincnt_1h<=6'd0;end else if(key_in3||rd_req)begincnt_1h<=rd_data[15:8];endelse if(add_cnt_1h)beginif(end_cnt_1h)begincnt_1h<=6'd0;endelse begincnt_1h<=cnt_1h+1'b1;endend

end assign add_cnt_1h=end_cnt_1min;

assign end_cnt_1h=add_cnt_1h&&cnt_1h==MAX_1H;//数据输出

always @(posedge clk or negedge rst_n)begin if(!rst_n)begindata_min<=8'd3;data_s<=8'd7;data_ms<=8'd2;

end

else

begindata_min<=cnt_1h;data_s<=cnt_1min;data_ms<=cnt_1s/10;end

end

assign din_out={data_min,data_s,data_ms};

endmodule五、I2C驱动

module i2c( input clk ,input rst ,input [7:0] wr_data ,input [4:0] cmd ,input cmd_vld ,output [7:0] rd_data ,output rd_data_vld ,output reg rev_ack ,output done ,output reg scl ,inout sda

);//para define

localparam IDLE = 7'b0000001,START = 7'b0000010,WR_DATA = 7'b0000100,RD_DATA = 7'b0001000,R_ACK = 7'b0010000,T_ACK = 7'b0100000,STOP = 7'b1000000;

parameter T = 100_000,SCL_MAX = 50_000_000 / T;

parameter SCL_LOW_HALF = (SCL_MAX * 1 / 4) - 1,SCL_HIGH_HALF = (SCL_MAX * 3 / 4) - 1;

`define START_BIT 5'b00001

`define WRITE_BIT 5'b00010

`define READ_BIT 5'b00100

`define STOP_BIT 5'b01000

`define ACK_BIT 5'b10000

`define ACK 0

`define NO_ACK 1//reg define

reg [6:0] cstate ;

reg [6:0] nstate ;

reg [4:0] cmd_r ;

reg [7:0] wr_data_r ;

reg [7:0] rd_data_r ;

reg sda_out ;

reg OE ;

reg [8:0] cnt_bit ;

reg [3:0] num ;

reg [3:0] cnt_num ;//wire define

wire sda_in ;

wire add_cnt_bit ;

wire end_cnt_bit ;

wire add_cnt_num ;

wire end_cnt_num ;

wire IDLE_START ;

wire START_WR_DATA ;

wire WR_DATA_R_ACK ;

wire R_ACK_IDLE ;

wire IDLE_WR_DATA ;

wire R_ACK_STOP ;

wire STOP_IDLE ; wire IDLE_RD_DATA ;

wire RD_DATA_T_ACK ;

wire T_ACK_IDLE ;

wire T_ACK_STOP ;assign add_cnt_bit = cstate != IDLE;

assign end_cnt_bit = add_cnt_bit && cnt_bit == SCL_MAX - 1'd1;

assign add_cnt_num = end_cnt_bit;

assign end_cnt_num = add_cnt_num && cnt_num == num - 1;assign IDLE_START = (cstate == IDLE) && cmd_vld && (cmd & `START_BIT) ;

assign START_WR_DATA = (cstate == START) && end_cnt_num && (cmd_r & `WRITE_BIT) ;

assign WR_DATA_R_ACK = (cstate == WR_DATA) && end_cnt_num ;

assign R_ACK_IDLE = (cstate == R_ACK) && end_cnt_num && !(cmd_r & `STOP_BIT) ;

assign IDLE_WR_DATA = (cstate == IDLE) && cmd_vld && (cmd & `WRITE_BIT) ;

assign R_ACK_STOP = (cstate == R_ACK) && end_cnt_num && (cmd_r & `STOP_BIT) ;

assign STOP_IDLE = (cstate == STOP) && end_cnt_num ;

assign IDLE_RD_DATA = (cstate == IDLE) && cmd_vld && (cmd & `READ_BIT) ;

assign RD_DATA_T_ACK = (cstate == RD_DATA) && end_cnt_num ;

assign T_ACK_IDLE = (cstate == T_ACK) && end_cnt_num && !(cmd_r & `STOP_BIT) ;

assign T_ACK_STOP = (cstate == T_ACK) && end_cnt_num && (cmd_r & `STOP_BIT) ;assign sda = OE ? sda_out : 1'bz;

assign sda_in = sda;

assign done = R_ACK_IDLE || T_ACK_IDLE || STOP_IDLE;

assign rd_data = rd_data_r;

assign rd_data_vld = T_ACK_IDLE || T_ACK_STOP;//

always @(posedge clk or negedge rst) beginif (!rst) beginwr_data_r <= 'd0;cmd_r <= 'd0;endelse if (cmd_vld) beginwr_data_r <= wr_data;cmd_r <= cmd;end

end//

always @(posedge clk or negedge rst) begin if(!rst)begincnt_bit <= 'd0;end else if(add_cnt_bit)begin if(end_cnt_bit)begin cnt_bit <= 'd0;endelse begin cnt_bit <= cnt_bit + 1'd1;end end

end //IIC_SCL

always @(posedge clk or negedge rst) beginif (!rst) beginscl <= 'd1;endelse if (cnt_bit == (SCL_MAX - 1 ) >> 1 || STOP_IDLE) beginscl <= 'd1;endelse if (end_cnt_bit) beginscl <= 'd0;end

end//

always @(posedge clk or negedge rst)begin if(!rst)begincnt_num <= 'd0;end else if(add_cnt_num)begin if(end_cnt_num)begin cnt_num <= 'd0;endelse begin cnt_num <= cnt_num + 1'd1;end end

end //

always @(*) begincase (cstate)IDLE : num = 1;START : num = 1;WR_DATA : num = 8;RD_DATA : num = 8;R_ACK : num = 1;T_ACK : num = 1;STOP : num = 1;default : num = 1;endcase

end//

always @(posedge clk or negedge rst)begin if(!rst)begincstate <= IDLE;end else begin cstate <= nstate;end

end//

always @(*) begincase(cstate)IDLE : beginif (IDLE_START) beginnstate = START;endelse if (IDLE_WR_DATA) beginnstate = WR_DATA;endelse if (IDLE_RD_DATA) beginnstate = RD_DATA;endelse beginnstate = cstate;endend START : beginif (START_WR_DATA) beginnstate = WR_DATA;endelse beginnstate = cstate;endend WR_DATA : beginif (WR_DATA_R_ACK) beginnstate = R_ACK;endelse beginnstate = cstate;endend RD_DATA : beginif (RD_DATA_T_ACK) beginnstate = T_ACK;endelse beginnstate = cstate;endend R_ACK : beginif (R_ACK_STOP) beginnstate = STOP;endelse if (R_ACK_IDLE) beginnstate = IDLE;endelse beginnstate = cstate;endend T_ACK : beginif (T_ACK_STOP) beginnstate = STOP;endelse if (T_ACK_IDLE) beginnstate = IDLE;endelse beginnstate = cstate;endend STOP : beginif (STOP_IDLE) beginnstate = IDLE;endelse beginnstate = cstate;endend default : nstate = cstate;endcase

end//

always @(posedge clk or negedge rst) beginif (!rst) beginOE <= 'b0;end else if (IDLE_START || START_WR_DATA || IDLE_WR_DATA || R_ACK_STOP || RD_DATA_T_ACK) beginOE <= 'b1;end else if (IDLE_RD_DATA || WR_DATA_R_ACK || STOP_IDLE) beginOE <= 'b0;end

end//

always @(posedge clk or negedge rst) beginif (!rst) beginsda_out <= 1;endelse begincase (cstate)IDLE :sda_out <= 1;START :beginif (cnt_bit == SCL_LOW_HALF) beginsda_out <= 'b1;endelse if (cnt_bit == SCL_HIGH_HALF) beginsda_out <= 'b0;endendWR_DATA :beginif (cnt_bit == SCL_LOW_HALF) beginsda_out <= wr_data_r[7 - cnt_num];endendT_ACK :beginif (cnt_bit == SCL_LOW_HALF) beginif (cmd & `ACK_BIT) beginsda_out <= `NO_ACK;endelse beginsda_out <= `ACK;endendendSTOP :beginif (cnt_bit == SCL_LOW_HALF) beginsda_out <= 'b0;endelse if (cnt_bit == SCL_HIGH_HALF) beginsda_out <= 'b1;endenddefault: sda_out <= 'b1;endcaseend

end//

always @(posedge clk or negedge rst) beginif (!rst) beginrev_ack <= 0;rd_data_r <= 8'b0;endelse begincase (cstate)RD_DATA:beginif (cnt_bit == SCL_HIGH_HALF) beginrd_data_r[7-cnt_num] <= sda_in;endendR_ACK :beginif (cnt_bit == SCL_HIGH_HALF) beginrev_ack <= sda_in;endenddefault:; endcaseend

endendmodule

六、eeprom模块

module eeprom ( input wire clk ,input wire rst ,input wire wr_req ,input wire rd_req ,input wire [6:0] device_id ,input wire [7:0] reg_addr ,input wire reg_addr_vld,input wire [7:0] wr_data ,input wire wr_data_vld ,output wire [7:0] rd_data ,output wire rd_data_vld ,output wire ready ,output wire scl ,inout wire sda

); //para define

`define START_BIT 5'b00001

`define WRITE_BIT 5'b00010

`define READ_BIT 5'b00100

`define STOP_BIT 5'b01000

`define ACK_BIT 5'b10000

localparam IDLE = 6'b000001,WR_REQ = 6'b000010,WR_WAIT = 6'b000100,RD_REQ = 6'b001000,RD_WAIT = 6'b010000,DONE = 6'b100000;localparam WR_CTRL_BYTE = 8'b1010_0000;

localparam RD_CTRL_BYTE = 8'b1010_0001;//wire define

wire IDLE_WR_REQ ;

wire IDLE_RD_REQ ;

wire WR_REQ_WR_WAIT ;

wire RD_REQ_RD_WAIT ;

wire WR_WAIT_WR_REQ ;

wire WR_WAIT_DONE ;

wire RD_WAIT_RD_REQ ;

wire RD_WAIT_DONE ;

wire DONE_IDLE ;

wire done ;

wire add_cnt_byte ;

wire end_cnt_byte ;//reg define

reg [5:0] cstate ;

reg [5:0] nstate ;

reg [2:0] num ;

reg [4:0] cmd ;

reg cmd_vld ;

reg [7:0] op_wr_data ;

reg [15:0] addr_r ;

reg [7:0] wr_data_r ;

reg [2:0] cnt_byte ;

reg wr_req_r ;

reg rd_req_r ;assign add_cnt_byte = done;

assign end_cnt_byte = add_cnt_byte && cnt_byte == num - 1;

assign IDLE_WR_REQ = (cstate == IDLE) && wr_req_r;

assign IDLE_RD_REQ = (cstate == IDLE) && rd_req_r;

assign WR_REQ_WR_WAIT = (cstate == WR_REQ) && 1;

assign RD_REQ_RD_WAIT = (cstate == RD_REQ) && 1;

assign WR_WAIT_WR_REQ = (cstate == WR_WAIT) && done;

assign WR_WAIT_DONE = (cstate == WR_WAIT) && end_cnt_byte;

assign RD_WAIT_RD_REQ = (cstate == RD_WAIT) && done;

assign RD_WAIT_DONE = (cstate == RD_WAIT) && end_cnt_byte;

assign DONE_IDLE = (cstate == DONE) && 1;

assign ready = cstate == IDLE; //

always @(posedge clk or negedge rst) beginif (!rst) beginwr_req_r <=0;rd_req_r <= 0;endelse beginwr_req_r <= wr_req;rd_req_r <= rd_req;end

end//

always @(posedge clk or negedge rst) beginif (!rst) beginaddr_r <= 'd0;endelse if (reg_addr_vld) beginaddr_r <= reg_addr;end

end//

always @(posedge clk or negedge rst) beginif (!rst) beginwr_data_r <= 'd0;endelse if (wr_req) beginwr_data_r <= wr_data;end

end//

always @(posedge clk or negedge rst)begin if(!rst)begincnt_byte <= 'd0;end else if(add_cnt_byte)begin if(end_cnt_byte)begin cnt_byte <= 'd0;endelse begin cnt_byte <= cnt_byte + 1'd1;end end

end //

always @(posedge clk or negedge rst) beginif (!rst) beginnum <= 1;endelse if (wr_req) beginnum <= 4;endelse if (rd_req) beginnum <= 5;endelse if (end_cnt_byte) beginnum <= 1;end

end//

always @(posedge clk or negedge rst)begin if(!rst)begincstate <= IDLE;end else begin cstate <= nstate;end

end//

always @(*) begincase(cstate)IDLE :beginif (IDLE_WR_REQ) beginnstate = WR_REQ;endelse if (IDLE_RD_REQ) beginnstate = RD_REQ;endelse beginnstate = cstate;endend WR_REQ :beginif (WR_REQ_WR_WAIT) beginnstate = WR_WAIT;endelse beginnstate = cstate;endend WR_WAIT :beginif (WR_WAIT_DONE) beginnstate = DONE;endelse if (WR_WAIT_WR_REQ) beginnstate = WR_REQ;endelse beginnstate = cstate;endend RD_REQ :beginif (RD_REQ_RD_WAIT) beginnstate = RD_WAIT;endelse beginnstate = cstate;endend RD_WAIT :beginif (RD_WAIT_DONE) beginnstate = DONE;endelse if (RD_WAIT_RD_REQ) beginnstate = RD_REQ;endelse beginnstate = cstate;endend DONE :beginif (DONE_IDLE) beginnstate = IDLE;endelse beginnstate = cstate;endend default : nstate = cstate;endcase

end//

always @(posedge clk or negedge rst) beginif (!rst) beginTX(0,4'h0,8'h00);endelse begincase (cstate)RD_REQ:begincase (cnt_byte)0 : TX(1,(`START_BIT | `WRITE_BIT),WR_CTRL_BYTE);1 : TX(1,(`WRITE_BIT ),addr_r[15:8]);2 : TX(1,(`WRITE_BIT ),addr_r[7:0] );3 : TX(1,(`START_BIT | `WRITE_BIT),RD_CTRL_BYTE);4 : TX(1,(`READ_BIT | `STOP_BIT ),8'h00 );default: TX(0,cmd,op_wr_data);endcaseendWR_REQ:begincase (cnt_byte)0 : TX(1,(`START_BIT | `WRITE_BIT),WR_CTRL_BYTE);1 : TX(1,(`WRITE_BIT ),addr_r[15:8]);2 : TX(1,(`WRITE_BIT ),addr_r[7:0] );3 : TX(1,(`WRITE_BIT | `STOP_BIT ),wr_data_r );default: TX(0,cmd,op_wr_data);endcaseenddefault: TX(0,cmd,op_wr_data);endcaseend

endi2c inst_i2c(.clk (clk),.rst (rst),.wr_data (op_wr_data),.cmd (cmd),.cmd_vld (cmd_vld),.rd_data (rd_data),.rd_data_vld (rd_data_vld),.done (done),.scl (scl),.sda (sda));task TX;input task_cmd_vld ;input [3:0] task_cmd ;input [7:0] task_wr_data ;begincmd_vld = task_cmd_vld ;cmd = task_cmd ;op_wr_data = task_wr_data ;end

endtaskendmodule

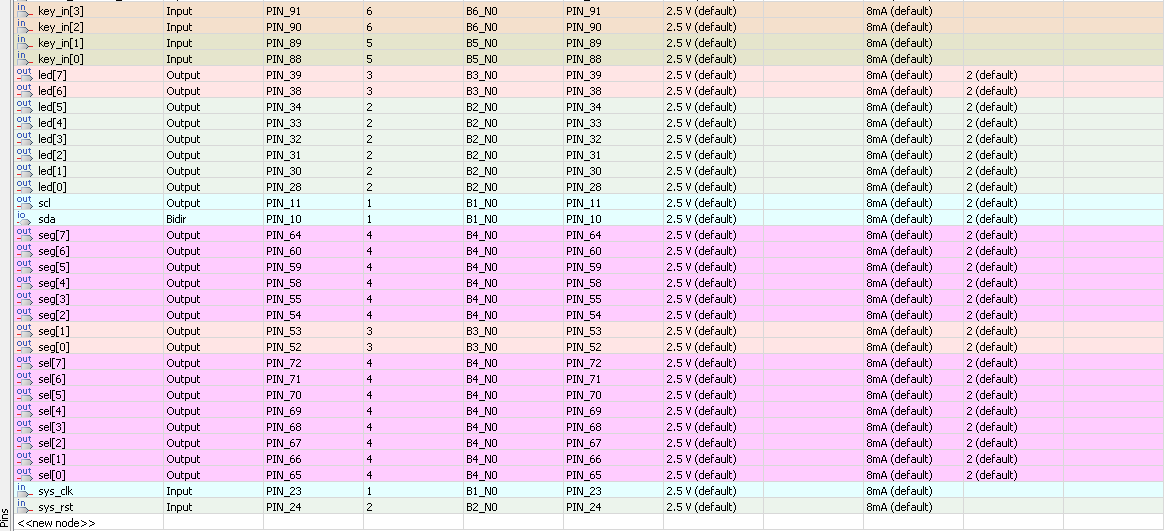

七、管脚约束

声明: 本代码借鉴网络资料,如有侵权请联系作者删除,如有错误请在评论区或者私信作者纠正。

相关文章:

蓝桥杯FPGA赛道第二次模拟题代码

一、顶层文件 module test( input wire sys_clk, input wire sys_rst, input wire [3:0]key_in, output reg [7:0]led,output wire scl, inout wire sda,//i2c的信号output wire [7:0]sel, output wire [7:0]seg//数码管的驱动 );wire [23:0] data ; reg [31:0] dsp_dat…...

keep the pipe Just full But no fuller - BBR 与尘封 40 年的求索

推荐一部短视频 Keep the pipe just full, but no fuller,作者就是大名鼎鼎的 L. Kleinrock,现代分组交换网的奠基人,这里有关于他这个人的介绍: https://www.lk.cs.ucla.edu/index.html https://en.wikipedia.org/wiki/Leonard…...

《React Native热更新实战:用Pushy打造无缝升级体验》

《React Native热更新实战:用Pushy打造应用“空中加油”,实现无缝升级体验》 写在前面:当你的APP需要"空中加油"时… 想象一下这样的场景:凌晨2点,你的React Native应用刚上线就爆出重大BUG,用户差评如潮水般涌来,应用商店审核至少需要3天…此刻你多么希望能…...

【开源解析】基于Python的智能文件备份工具开发实战:从定时备份到托盘监控

📁【开源解析】基于Python的智能文件备份工具开发实战:从定时备份到托盘监控 🌈 个人主页:创客白泽 - CSDN博客 🔥 系列专栏:🐍《Python开源项目实战》 💡 热爱不止于代码࿰…...

第四章:基于langchain构造一个完整RAG系统

文章目录 引言一、RAG的基本原理1.1 什么是RAG?1.2 RAG的应用场景 二、RAG系统的构建步骤2.1 环境准备2.2 加载和处理文档2.2.1 文档加载2.2.2 文本分割 2.3 构建嵌入模型2.4 创建向量存储与检索器2.5 检索与生成2.5.1 检索相关文档2.5.2 生成答案 三、完整代码示例…...

)

uniapp|实现多终端视频弹幕组件、内容轮询、信息表情发送(自定义全屏半屏切换、弹幕启用)

基于UniApp框架实现跨终端视频弹幕组件的开发,结合CSS3动画与setInterval轮询机制,完成弹幕从右向左的动态滚动效果,针对交互需求,设计弹幕启用开关、全屏/半屏模式切换功能,并利用cover-view组件解决原生层级覆盖问题。 目录 引言视频弹幕的交互价值与多终端适配需求Un…...

——栈的应用—数制转换)

数据结构(四)——栈的应用—数制转换

利用栈进行数制转换: 十进制转换八进制:先将十进制数除以八得到余数,余数入栈,然后将得到的商继续除以八,直到商为零 #include <stdio.h> #include <stdlib.h>#define MAXSIZE 100//数制转换//定义链表节…...

flinksql bug : Max aggregate function does not support type: CHAR

这个问题是flink中 CHAR 存在语义歧义,主要涉及到位数的关系,这里不做多讨论。 这个问题已经有人提了pr,新版本可以关注是否有解决 这个报错发生在 max(测试字段) ,这个测试字段如果是char 就会报错不支持 解决办法:…...

解决社区录音应用横屏状态下,录音后无法播放的bug

最近看到社区有小伙伴反映,社区录音应用横屏时,录音后无法播放的问题。现分享解决办法。 社区录音应用的来源:https://gitee.com/openharmony/applications_app_samples/tree/OpenHarmony-5.0.2-Release/code/SystemFeature/Media/Recorder …...

【MySQL】存储引擎 - InnoDB详解

📢博客主页:https://blog.csdn.net/2301_779549673 📢博客仓库:https://gitee.com/JohnKingW/linux_test/tree/master/lesson 📢欢迎点赞 👍 收藏 ⭐留言 📝 如有错误敬请指正! &…...

软件工程之形式化说明技术深度解析

按照形式化的程度,可以把软件工程使用的方法划分成非形式化、半形式化和形式化3种。用自然语言描述需求规格说明书,是典型的非形式化方法。用数据流图或实体-联系图建立模型,是典型的半形式化方法。 所谓形式化方法,是描述系统性…...

Nacos源码—6.Nacos升级gRPC分析一

大纲 1.Nacos 2.x版本的一些变化 2.客户端升级gRPC发起服务注册 3.服务端进行服务注册时的处理 4.客户端服务发现和服务端处理服务订阅的源码分析 1.Nacos 2.x版本的一些变化 变化一:客户端和服务端的交互方式由HTTP升级为gRPC Nacos 1.x服务端会提供一系列的…...

使用 React 实现语音识别并转换功能

在现代 Web 开发中,语音识别技术的应用越来越广泛。它为用户提供了更加便捷、自然的交互方式,例如语音输入、语音指令等。本文将介绍如何使用 React 实现一个简单的语音识别并转换的功能。 功能概述 我们要实现的功能是一个语音识别测试页面࿰…...

2.5 点云数据存储格式——大型点云传输格式

通常,进行大型点云数据传输时,一般采用一种后缀为bin的文...

)

Windows系统下使用Kafka和Zookeeper,Python运行kafka(一)

下载和安装见Linux系统下使用Kafka和Zookeeper 配置 Zookeeper Zookeeper 是 Kafka 所依赖的分布式协调服务。在 Kafka 解压目录下,有一个 Zookeeper 的配置文件模板config/zookeeper.properties,你可以直接使用默认配置。 启动 Zookeeper 打开命令提示符(CMD),进入 K…...

——栈和队列)

数据结构(三)——栈和队列

一、栈和队列的定义和特点 栈:受约束的线性表,只允许栈顶元素入栈和出栈 对栈来说,表尾端称为栈顶,表头端称为栈底,不含元素的空表称为空栈 先进后出,后进先出 队列:受约束的线性表࿰…...

零基础入门Hadoop:IntelliJ IDEA远程连接服务器中Hadoop运行WordCount

今天我们来聊一聊大数据,作为一个Hadoop的新手,我也并不敢深入探讨复杂的底层原理。因此,这篇文章的重点更多是从实际操作和入门实践的角度出发,带领大家一起了解大数据应用的基本过程。我们将通过一个经典的案例——WordCounter&…...

在Postman中高效生成测试接口:从API文档到可执行测试的完整指南

引言 在API开发与测试流程中,Postman是一款高效的工具,能将API文档快速转化为可执行的测试用例。本文以《DBC协议管理接口文档》为例,详细讲解如何通过Postman实现接口的创建、配置、批量生成及自动化测试,帮助开发者和测试人员提升效率,确保接口质量。 一、准备工作:理…...

飞云分仓操盘副图指标操作技术图文分解

如上图,副图指标-飞云分仓操盘指标,指标三条线蓝色“首峰线”,红色“引力1”,青色“引力2”,多头行情时“首峰线”和“引力1”之间显示为红色,“引力1”和“引力2”多头是区间颜色显示为紫色。 如上图图标信…...

K8s中的containerPort与port、targetPort、nodePort的关系:

pod中的containerPort与service中的port、targetPort、nodePort的关系: 1、containerPort为pod的配置,对应pod内部服务监听的具体端口,例如nginx服务默认监听80端口,那么nginx的pod的containerPort应该配置为80,例如m…...

jquery+ajax+SpringBoot实现前后端分离技术

一、前端方面: 第1步,在前端HTML页面的头部引入jquery <head><meta http-equiv"Content-Type" content"text/html;charsetUTF-8"><title>XXX</title><link rel"stylesheet" type"text/…...

)

阀门产业发展方向报告(石油化工阀门应用技术交流大会)

本文大部分内容来自中国通用机械工业协会副会长张宗列在“2024全国石油化工阀门应用技术交流大会”上发表的报告。 一、国外阀门产业发展 从全球阀门市场分布看,亚洲是最大的工业阀门市场,美洲是全球第二大工业阀门市场,欧洲位列第三。 从国…...

华为云Astro后端开发中对象、事件、脚本、服务编排、触发器、工作流等模块的逻辑关系如何?以iotDA数据传输过程举例演示元素工作过程

目录 🏭 类比总览:低代码平台就像一座自动化工厂 🧱 1. 对象(Object) = 工厂里的“原材料仓库” 🧱 2. 结构体(Structure) = 自定义的“装配模具” 🔔 3. 事件(Event) = 触发的“感应器” ✍️ 4. 脚本(Script) = 后台的“逻辑处理代码” ⚙️ 5. 服务编…...

面向小型企业顶点项目的网络安全咨询人机协作框架

1. 简介 1.1. 背景和动机 由于小型企业无法访问结构化系统,且缺乏大型组织通常拥有的专用资源,它们经常面临巨大的网络安全挑战 [ [1 ]。为大型企业设计的网络安全框架通常对小型企业来说过于复杂且不切实际,导致它们容易受到复杂的网络威胁 2 ]。这种复杂性可能导致小型…...

RSAC 2025观察:零信任+AI=网络安全新范式

2025年4月28日~5月1日,全球最具影响力的网络安全盛会RSAC 2025在美国旧金山举办,吸引了全球44,000名网络安全从业者参与。大会以“Many Voices. One Community.”为主题,聚焦AI安全、供应链风险、零信任等核心议题。其中,AI Agent…...

ruoyi-flowable-plus 前端框架启动报错修复

版本 1. ruoyi-flowable-plus 前端框架启动报错修复 启动时设置环境变量 "scripts": {"dev": "SET NODE_OPTIONS--openssl-legacy-provider && vue-cli-service serve","build:prod": "vue-cli-service build",&qu…...

安全可控·高效响应|北峰智能互通矿业通信系统解决方案

项目概况 随着矿业行业工作环境日益复杂,涵盖地下开采、露天挖掘、矿物运输及深加工等多个环节,作业区域呈现广阔且分散的特点,往往存在诸多安全风险。当面临突发事故,由于应急救援体系不完善,救援通信系统相对落后&a…...

ubuntu查看安装的软件包的位置

在 Ubuntu 中,libcli11-dev 是一个 头文件库(header-only),因此它不会像动态库(.so 文件)那样有明确的下载路径。但你可以通过以下方法查看它的安装位置: 1. 查看 libcli11-dev 安装的文件 使用…...

【金仓数据库征文】金仓数据库 KES 助力企业数据库迁移的实践路径

在企业数字化转型浪潮的强力推动下,数据库迁移已成为企业升级 IT 架构、提升数据管理能力的关键环节。从 MySQL 到金仓数据库 KingbaseES(KES)的迁移方案,为企业提供了一条高效、可靠的数据库升级路径。 一、迁移挑战与金仓数据…...

Nginx1.26.2安装包编译安装并配置stream模块

准备nginx安装文件:nginx-1.26.2.tar.gz cd /usr/local wget http://nginx.org/download/nginx-1.26.2.tar.gz tar -zxvf nginx-1.26.2.tar.gz && cd nginx-1.26.2 1.创建安装目录 mkdir nginx 2.解压安装文件nginx-1.26.2.tar.gz tar -zxvf nginx-1.26…...

kotlin @JvmStatic注解的作用和使用场景

1. JvmStatic 的作用 JvmStatic 是 Kotlin 提供的一个注解,用于在 JVM 上将伴生对象(companion object)中的方法或属性暴露为 Java 静态方法或字段。 作用对象:只能用在 companion object 中的函数或属性。效果: 在 …...

Blind SSRF with Shellshock exploitation过关

Blind SSRF with Shellshock exploitation 生活就像一杯咖啡,苦与甜都是必需的,关键是要学会享受每一口。 先说通关方法: 1.首先在bp的扩展商店安装插件 Collaborator Everywhere 2.进入靶场首页 复制url https://0af600d3048daad080e6…...

2025-05-08 Unity 网络基础9——FTP通信

文章目录 1 FTP1.1 工作原理1.2 传输模式 2 搭建 FTP 服务器2.1 启用服务2.2 配置站点2.3 设置防火墙2.4 指定用户登录 3 常用 API3.1 NetworkCredential3.2 FtpWebRequest3.3 FtpWebResponse 4 实战操作4.1 上传文件4.2 下载文件4.3 删除文件4.4 获取文件大小4.5 创建文件夹4.…...

)

3.2.3 掌握RDD转换算子 - 5. 合并算子 - union()

在本节课中,我们学习了Spark RDD的union()算子,它能够将两个数据类型一致的RDD合并为一个新的RDD,主要用于整合不同数据源。通过案例演示,我们成功将两个简单的数字RDD合并,直观地看到合并结果是按原顺序纵向拼接&…...

数据来源合法性尽职调查:保障权益的关键防线

首席数据官高鹏律师团队 在当今数字化时代,数据已成为企业和个人最为宝贵的资产之一。然而,伴随着数据的广泛应用与流通,其来源的合法性问题愈发凸显,犹如隐藏在暗处的礁石,稍不留神就可能让涉事主体陷入法律的漩涡。…...

sui在windows虚拟化子系统Ubuntu和纯windows下的安装和使用

一、sui在windows虚拟化子系统Ubuntu下的安装使用(WindowsWsl2Ubuntu24.04) 前言:解释一下WSL、Ubuntu的关系 WSL(Windows Subsystem for Linux)是微软推出的一项功能,允许用户在 Windows 系统中原生运行…...

springmvc的入门案例

springmvc的概述 SpringMVC的概述 是一种基于Java实现的MVC设计模型的请求驱动类型的轻量级WEB框架。Spring MVC属于SpringFrameWork的后续产品,已经融合在Spring Web Flow里面。Spring 框架提供了构建 Web 应用程序的全功能 MVC 模块。使用 Spring 可插入的 MVC 架…...

【MCP】为什么使用Streamable HTTP: 相比SSE的优势与实践指南

在现代Web开发中,实时通信已经成为许多应用的核心需求。从聊天应用到股票市场更新,从游戏服务器到AI模型通信,各种技术应运而生以满足这些需求。最近,Model Context Protocol (MCP) 引入了一种新的传输机制 —— Streamable HTTP&…...

的使用)

CentOS的防火墙工具(firewalld和iptables)的使用

CentOS的防火墙工具因版本不同而异,以下是具体操作步骤: 一、firewalld(CentOS 7及以上默认工具) 1、安装与启动: 安装:sudo yum install firewalld 启动服务:sudo systemctl start fir…...

解析小米大模型MiMo:解锁语言模型推理潜力

一、基本介绍 1.1 项目背景 在大型语言模型快速发展的背景下,小米AI团队推出MiMo系列模型,突破性地在7B参数规模上实现卓越推理能力。传统观点认为32B以上模型才能胜任复杂推理任务,而MiMo通过创新的训练范式证明:精心设计的预训练和强化学习策略,可使小模型迸发巨大推理…...

web 自动化之 Selenium 元素定位和浏览器操作

文章目录 一、元素定位的八大方法1、基于 id/name/class/tag_name 定位2、基于 a 标签元素的链接文本定位3、基于xpath定位4、css定位 二、浏览器操作1、信息获取2、 浏览器关闭3、 浏览器控制 一、元素定位的八大方法 web 自动化测试就是通过代码对网页进行测试,在…...

vscode如何使用 GitHub Copilot

1.在vscode中扩展工具栏搜索“copilot”,选择GitHub Copilot安装。 2.使用快捷键CtrlAltI 打开聊天界面,输入问题后回车即可使用。 注意: 使用copilot需要使用GitHub账号先登录,如果打不开登录页面,需要修改host文件&a…...

AWS之存储服务

存储术语 分类 接口/技术类型 应用场景特点 关系及区别 机械硬盘接口 IDE(Integrated Drive Electronics) 早期用于个人电脑,现已逐渐淘汰 机械硬盘接口、固态硬盘接口是硬盘与主机或其他设备连接的物理和协议规范; FC - …...

安装 Docker

一、CentOS 系统安装 Docker 1. 卸载旧版本(如有) sudo yum remove docker \docker-client \docker-client-latest \docker-common \docker-latest \docker-latest-logrotate \docker-logrotate \docker-engine 2. 安装依赖工具 sudo yum install -y…...

代理协议解析:如何根据需求选择HTTP、HTTPS或SOCKS5?

在现代网络中,代理服务器是一种常见的工具,用于提高安全性、匿名性和访问速度。常见的代理协议包括HTTP、HTTPS和SOCKS5。本文将详细解析这三种代理协议,并帮助您根据具体需求选择最合适的代理协议。 一、HTTP代理 1.1 特点 用途广泛&…...

用于构建安全AI代理的开源防护系统

大家读完觉得有帮助记得及时关注!!! 大型语言模型(LLMs)已经从简单的聊天机器人演变为能够执行复杂任务的自主代理,例如编辑生产代码、编排工作流程以及基于不受信任的输入(如网页和电子邮件&am…...

CTF-DAY10

[SWPUCTF 2021 新生赛]zipbomb 题目描述: 请注意,不要以任何方式尝试完全解压该文件,运存被塞满后果自负。请尝试分析该文件。 使用WinRAR解压打开 CTFSHOW刷题 crypto11 密文:a8db1d82db78ed452ba0882fb9554fc 提交 flag{明…...

vs swr 请求)

WHAT - react-query(TanStack Query) vs swr 请求

文章目录 react-query什么是 TanStack Query(原 React Query)核心特性 TanStack Query vs SWR 对比具体特性对比哪个更适合你 总结 react-query react-query(现已更名为 TanStack Query)和 SWR 一样,都是专注于 远程数…...

WebFlux与HttpStreamable关系解析

1-Streamable 1-WebFlux与HttpStreamable关系解析2-MCP协议Streamable HTTP 2-参考网址 MCP协议Streamable HTTPMCP协议重大升级,Spring AI Alibaba联合Higress发布业界首个Streamable HTTP实现方案 3-WebFlux与HttpStreamable关系解析 WebFlux 和 HttpStreamabl…...

深度学习工程化:基于TensorFlow的模型部署全流程详解

深度学习工程化:基于TensorFlow的模型部署全流程详解 引言 在深度学习项目中,模型训练只是第一步,将模型成功部署到生产环境才是真正创造价值的关键。本文将全面介绍TensorFlow模型从训练到部署的完整工程化流程,涵盖多种部署场…...