紫光同创FPGA实现HSSTHP光口视频传输+图像缩放,基于Aurora 8b/10b编解码架构,提供3套PDS工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 紫光同创FPGA相关方案推荐

- 我这里已有的 GT 高速接口解决方案

- Xilinx系列FPGA实现GTP光口视频传输方案推荐

- Xilinx系列FPGA实现GTX光口视频传输方案推荐

- Xilinx系列FPGA实现GTH光口视频传输方案推荐

- Xilinx系列FPGA实现UltraScale-GTH光口视频传输方案推荐

- Xilinx系列FPGA实现UltraScale-GTY光口视频传输方案推荐

- 紫光同创PGL100G系列FPGA实现HSSTLP光口视频传输方案推荐

- 3、设计思路框架

- 工程设计原理框图

- 输入Sensor之-->OV7725摄像头

- 输入Sensor之-->OV5640摄像头

- 输入Sensor之-->芯片解码的HDMI

- 图像缩放模块详解

- 图像缩放模块使用(重点阅读)

- 图像缩放模块仿真

- 视频数据组包

- 基于HSSTHP高速接口的视频传输架构

- HSSTHP IP 简介

- HSSTHP基本结构

- HSSTHP发送和接收处理流程

- HSSTHP的参考时钟

- HSSTHP发送接口

- HSSTHP接收接口

- HSSTHP IP核调用和使用

- 数据对齐

- 视频数据解包

- 图像缓存架构

- HDMI输出架构

- 工程源码架构

- 4、PDS工程源码1详解:OV7725输入版本

- 5、PDS工程源码2详解:OV5640输入版本

- 6、PDS工程源码3详解:HDMI输入版本

- 7、上板调试验证并演示

- 准备工作

- HSSTHP光口视频缩放传输效果演示

- 8、福利:工程源码获取

紫光同创FPGA实现HSSTHP光口视频传输+图像缩放,基于Aurora 8b/10b编解码架构,提供3套PDS工程源码和技术支持

1、前言

国产FPGA现状:

“苟利国家生死以,岂因祸福避趋之!”大洋彼岸的我优秀地下档员,敏锐地洞察到祖国的短板在于先进制程半导体的制造领域,于是本着为中华民族伟大复兴的中国梦贡献绵薄之力的初心,懂先生站在高略高度和长远角度谋划,宁愿背当代一世之骂名也要为祖国千秋万世谋,2018年7月,懂先生正式打响毛衣战,随后又使出恰勃纸战术,旨在为祖国先进制程半导体领域做出自主可控的战略推动;2019年初我刚出道时,还是Xilinx遥遥领先的时代(现在貌似也是),那时的国产FPGA还处于黑铁段位;然而才短短7年,如今的国产FPGA属于百家争鸣、百花齐放、八仙过海、神仙打架、方兴未艾、得陇望蜀、友商都是XX的喜极而泣之局面,此情此景,不得不吟唱老人家的诗句:魏武挥鞭,东临碣石有遗篇,萧瑟秋风今又是,换了人间。。。

目前对于国产FPGA优势有以下几点:

1:性价比高,与同级别国外大厂芯片相比,价格相差几倍甚至十几倍;

2:自主可控,国产FPGA拥有完整自主知识产权的产业链,从芯片到相关EDA工具;

3:响应迅速,FAE技术支持比较到位,及时解决开发过程中遇到的问题,毕竟中文数据手册;

4:采购方便,产业链自主可控,采购便捷;

FPGA实现SFP光口视频编解码现状;

目前FPGA实现SFP光口传输方案很丰富,主流还是Xilinx的GT系列,此外国产FPGA厂商也纷纷抄袭Xilinx推出了自己的高速接口方案;基于Xilinx系列FPGA的SFP光口视频编解码主要有以下几种,Artix7系列的GTP、Kintex7系列的GTX、更高端FPGA器件的GTH、GTY、GTV、GTM等,线速率越来越高,应用场景也越来越高端;编码方式也是多种多样,有8b/10b编解码、64b/66b编解码、HDMI编解码、SDI编解码等等;国产的紫光同创也推出了HSSTLP、HSSTHP等方案,官方宣称其性能可对标Xilinx的GTP、GTX,但本博实际测试发现,HSSTLP/HP无论是功能还是性能都无法与Xilinx的GTP/GTX相媲美,但将个烂就也行,毕竟聊胜于无嘛;本设计采用紫光同创系列FPGA的HSSTHP作为高速接口、8b/10b编解码的方式实现SFP光口视频编解码;

FPGA实现图像缩放现状:

FPGA实现图像缩放大体分两种方案,第一种是使用纯verilog代码实现,其优势是可移植性强,可广泛应用于各种型号FPGA,维护性强,通用性强,缺点是开发难度大,对开发者技术要求很高,功能和性能不够灵活;第二种是使用纯HLS代码实现,比如Xilinx的Video Processing Subsystem,其优势是开发难度小,对开发者技术要求很低,可快速实现部署,特别适用于Xilinx的Zynq系列FPGA,功能和性能很灵活,缺点是可移植性很差,目前仅限于Xilinx系列FPGA,维护性差,通用性差;本设计采用纯verilog代码方案实现双线性插值的图像缩放;

工程概述

本文使用紫光同创的Titan2系列FPGA做基础的图像视频采集系统;视频输入源有多种,一种是板载的HDMI输入接口,另一种是传统摄像头,包括OV7725、OV5640和AR0135;如果你的FPGA开发板没有视频输入接口,或者你的手里没有摄像头时,可以使用FPGA逻辑实现的动态彩条模拟输入视频,代码里通过parametr参数选择视频源,默认不使用动态彩条;FPGA首先对摄像头进行i2c初始化配置,然后采集摄像头视频;然后对输入视频做图像缩放操作,图像缩放模块可实现任意比例缩放,支持临域插值和双线性插值2种算法,通过模块顶层参数选择,默认使用双线性插值;然后采集的输入视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTHP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTHP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR4作为缓存介质;然后Native视频时序控制图像缓存架构从DDR4中读取视频,并做Native视频时序同步,输出RGB888视频;然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;针对市场主流需求,本设计提供3套PDS工程源码,具体如下:

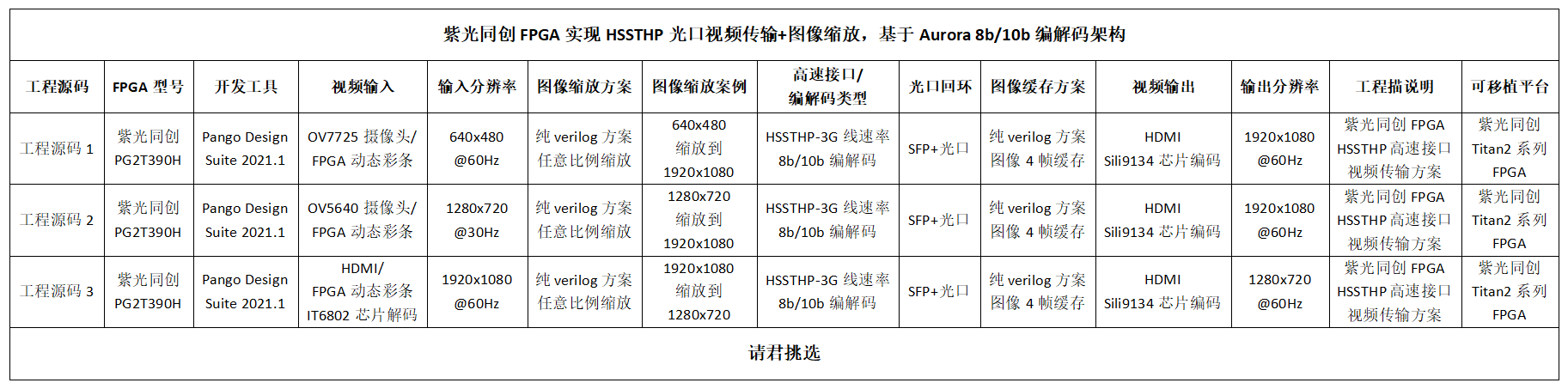

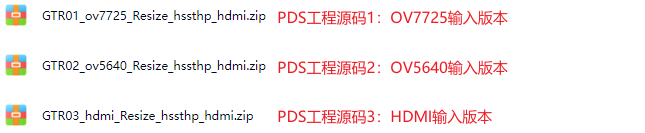

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为PG2T390H-6FFBG900;输入视频为OV7725摄像头或者动态彩条,默认使用OV7725;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为640x480@60Hz;然后对输入视频做图像缩放操作,将原视频从640x480缩放到1920x1080,您可修改缩放参数轻松缩放到其他分辨率,工程只是举例,修改方法博客有说明;然后缩放后的视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTHP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTHP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR4作为缓存介质;然后Native视频时序控制图像缓存架构从DDR4中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1920x1080@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用于紫光同创FPGA实现SFP光口的视频采集卡(光端机)应用;

工程源码2

开发板FPGA型号为PG2T390H-6FFBG900;输入视频为OV5640摄像头或者动态彩条,默认使用OV5640;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为1280x720@30Hz;然后对输入视频做图像缩放操作,将原视频从1280x720缩放到1920x1080,您可修改缩放参数轻松缩放到其他分辨率,工程只是举例,修改方法博客有说明;然后缩放后的视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTHP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTHP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR4作为缓存介质;然后Native视频时序控制图像缓存架构从DDR4中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1920x1080@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用于紫光同创FPGA实现SFP光口的视频采集卡(光端机)应用;

工程源码3

开发板FPGA型号为PG2T390H-6FFBG900;输入视频为HDMI视频,用笔记本电脑模拟,笔记本电脑通过HDMI线连接FPGA开发板的HDMI输入接口,板载的IT6802芯片实现HDMI视频解码,FPGA使用纯Verilog实现的i2c总线对IT6802进行初始化配置,分辨率配置为1920x1080@60Hz,输出RGB888视频给FPGA;然后对输入视频做图像缩放操作,将原视频从1920x1080缩放到1280x720,您可修改缩放参数轻松缩放到其他分辨率,工程只是举例,修改方法博客有说明;然后缩放后的视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用紫光同创官方的HSSTHP IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入紫光同创官方的HSSTHP IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后视频送入图像缓存架构实现视频3帧缓存功能,本设计使用DDR4作为缓存介质;然后Native视频时序控制图像缓存架构从DDR4中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1280x720@60Hz,然后视频送入Silicom9134芯片实现RGB转HDMI功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用于紫光同创FPGA实现SFP光口的视频采集卡(光端机)应用;

本博客描述了紫光同创FPGA实现HSSTHP光口视频传输+图像缩放的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

紫光同创FPGA相关方案推荐

鉴于国产FPGA的优异表现和市场需求,我专门开设了一个人紫光同创FPGA专栏,里面收录了基于紫光同创FPGA的图像处理、UDP网络通信、GT高速接口、PCIE等博客,感兴趣的可以去看看,博客地址:点击直接前往

我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

Xilinx系列FPGA实现GTP光口视频传输方案推荐

Xilinx 7系列FPGA基于GTP实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现GTX光口视频传输方案推荐

Xilinx 7系列FPGA基于GTX实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现GTH光口视频传输方案推荐

Xilinx 7系列FPGA基于GTH实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现UltraScale-GTH光口视频传输方案推荐

Xilinx UltraScale系列FPGA基于UltraScale-GTH实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

Xilinx系列FPGA实现UltraScale-GTY光口视频传输方案推荐

Xilinx UltraScale+系列FPGA基于UltraScale-GTY实现光口视频传输,其性能优于紫光同创FPGA的HSSTLP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

紫光同创PGL100G系列FPGA实现HSSTLP光口视频传输方案推荐

紫光同创PGL100G系列FPGA基于HSSTLP实现光口视频传输,其性能不及紫光同创FPGA的HSSTHP,有这方面需求的用户可以参考本博之前的博客,博客链接如下:

点击直接前往

3、设计思路框架

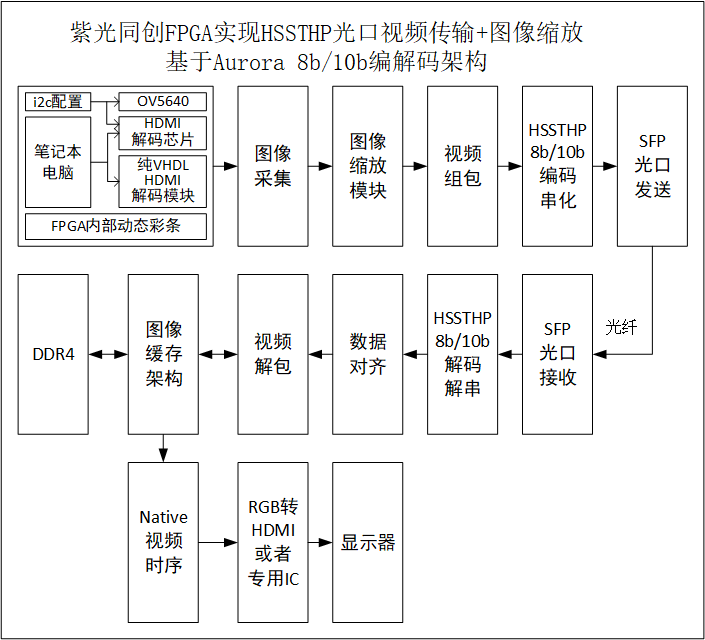

工程设计原理框图

工程设计原理框图如下:

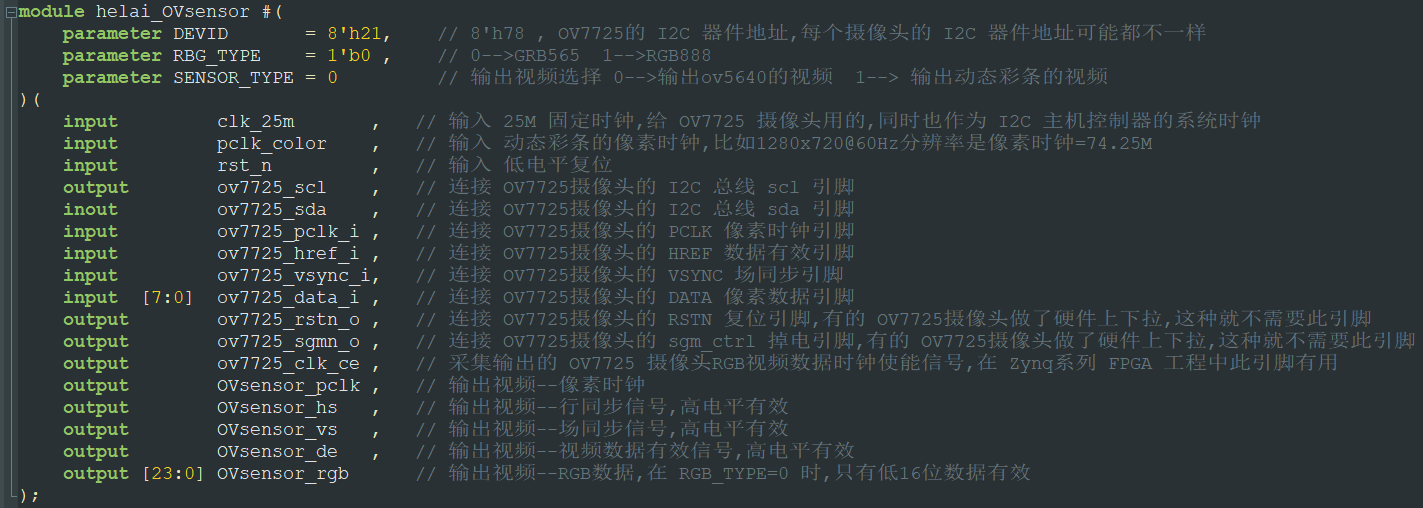

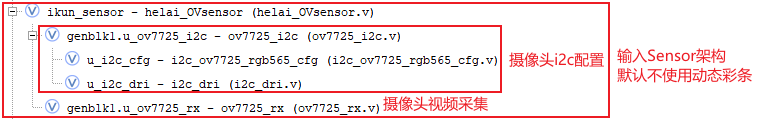

输入Sensor之–>OV7725摄像头

输入Sensor是本工程的输入设备,其一为OV7725摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV7725摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

OV7725摄像头需要i2c初始化配置,本设计配置为640x480@60Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV7725摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV7725摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

输入Sensor之–>OV5640摄像头

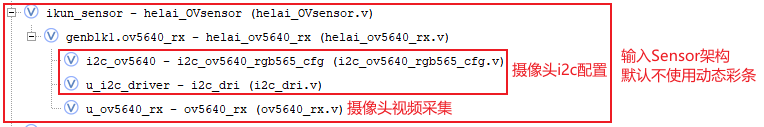

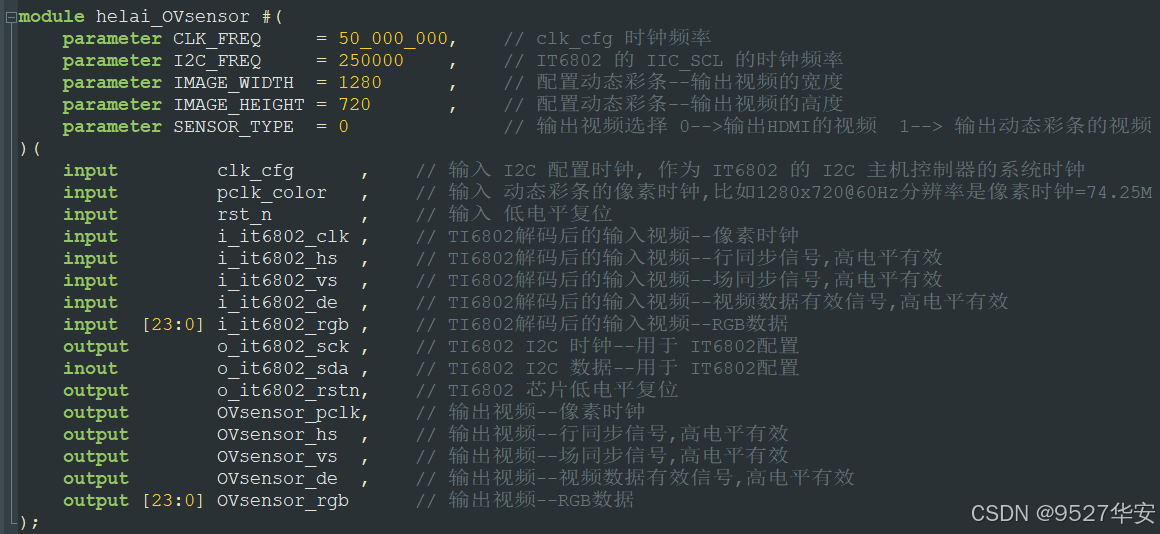

输入Sensor是本工程的输入设备,其一为OV5640摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV5640摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

OV5640摄像头需要i2c初始化配置,本设计配置为1280x720@30Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV5640摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV5640摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

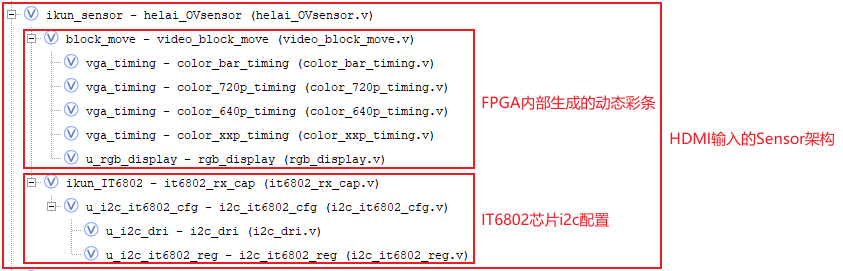

输入Sensor之–>芯片解码的HDMI

输入Sensor是本工程的输入设备,其二为板载的HDMI输入接口;输入源为板载的HDMI输入接口或动态彩条,分辨率为1920x1080@60Hz,使用笔记本电脑接入HDMI输入接口,以模拟输入Sensor;HDMI解码方案为芯片解码,使用IT6802,可将输入的HDMI视频解码为RGB888视频;FPGA纯verilog实现的i2c配置模块完成对IT6802芯片的配置,分辨率配置为1920x1080@60Hz;可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出HDMI接口采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

整个模块代码架构如下:

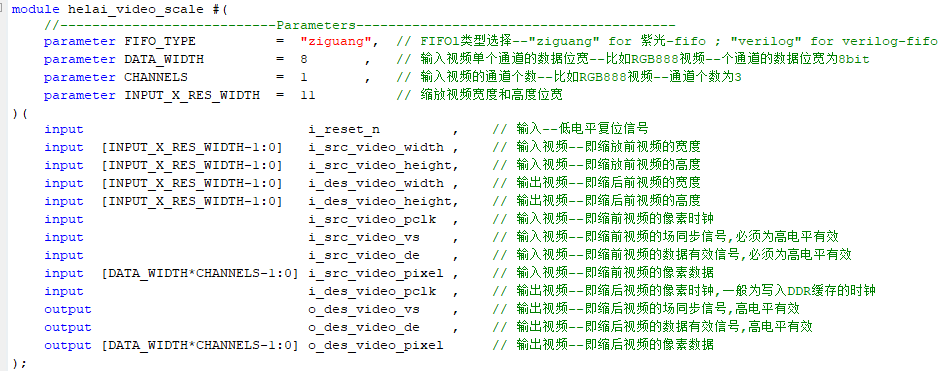

图像缩放模块详解

图像缩放模块功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

依据上图,图像缩放模块内部核心是例化了4个双口RAM,作用是缓存4行图像,以得到4个临近的像素,以此为基础做线性插值;如果是做图像放大操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中插入更多的像素点来扩大分辨率;如果是做图像缩小操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中删除更多的像素点来缩小分辨率;此外,前面描述的工作是实时的、整幅图像全部扫描式的进行,所以需要对RAM的读写操作进行精准控制;

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的PDS工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

FIFO_TYPE选择原则如下:

1:总体原则,选择"ziguang"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"ziguang";

3:当你图像缩放的视频分辨率较大时,请选"ziguang";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

代码里的配置如下:

图像缩放模块使用(重点阅读)

图像缩放模块使用非常简单,顶层代码里设置了四个参数,如下:

上图是将输入视频分辨率从1280x720缩放为1920x1080;

如果你想将输入视频分辨率从1280x720缩放为640x480;

则只需修改为如下:

再比如你想将输入视频分辨率从1280x720缩放为960x540;

则只需修改为如下:

在本博主这里,想要实现图像缩放,操作就是这么无脑简单,就该两个参数就能搞定貌似高大上的双线性插值图像缩放,这种设计、这种操作、这种工程源码,你还喜欢吗?

图像缩放模块仿真

图像缩放模块需要vivado和matlab联合仿真;

需要注意的是,仿真的目的是为了验证,这一步我已经替你们做完了,所以读者不再需要单独仿真,如果读者是在需要自己仿真玩玩儿,需要自己写仿真代码;vivado和matlab联合仿真详细步骤如下:

第一步:网上下载一张1280X720的图片,并用matlab将图片转换为RGB格式的txt文档;

第二步:在vivado下设计tstbench,将RGB格式的txt文档作为视频输入源给到图像缩放模块,并将缩放后的图像数据写入输出txt文档;

第二步:用matlab将输出txt文档转换为图片,并于原图一并输出显示以做比较;

根据以上方法得到以下仿真结果:

双线性插值算法原图1280X720缩小到800x600如下:

邻域插值算法原图1280X720缩小到800x600如下:

双线性插值算法原图1280X720放大到1920x1080如下:

邻域插值算法原图1280X720放大到1920x1080如下:

视频数据组包

由于视频需要在HSSTHP中通过aurora 8b/10b协议收发,所以数据必须进行组包,以适应aurora 8b/10b协议标准;视频数据组包模块代码位置如下:

首先,我们将16bit的视频存入FIFO中,存满一行时就从FIFO读出送入HSSTHP发送;在此之前,需要对一帧视频进行编号,也叫作指令,HSSTHP组包时根据固定的指令进行数据发送,HSSTHP解包时根据固定的指令恢复视频的场同步信号和视频有效信号;当一帧视频的场同步信号上升沿到来时,发送一帧视频开始指令 0,当一帧视频的场同步信号下降沿到来时,发送一帧视频开始指令 1,视频消隐期间发送无效数据 0 和无效数据 1,当视频有效信号到来时将每一行视频进行编号,先发送一行视频开始指令,在发送当前的视频行号,当一行视频发送完成后再发送一行视频结束指令,一帧视频发送完成后,先发送一帧视频结束指令 0,再发送一帧视频结束指令 1;至此,一帧视频则发送完成,这个模块不太好理解,所以我在代码里进行了详细的中文注释,需要注意的是,为了防止中文注释的乱序显示,请用notepad++编辑器打开代码;指令定义如下:

注意!!!指令可以任意更改,但最低字节必须为bc;

基于HSSTHP高速接口的视频传输架构

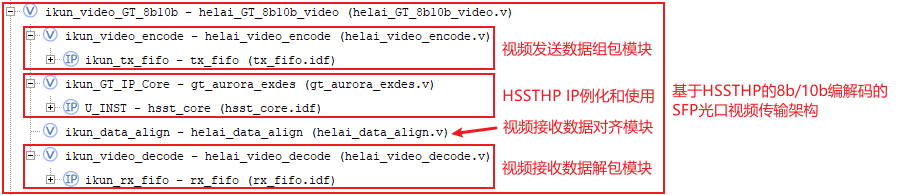

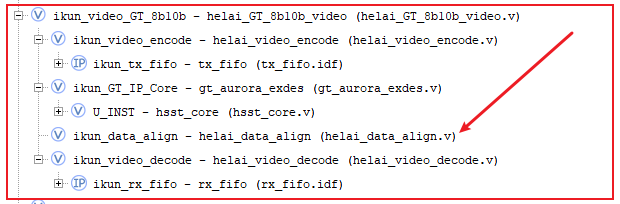

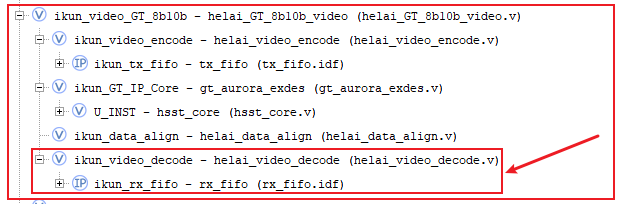

本设计使用HSSTHP高速接口传输视频,使用8b/10b编解码协议,搭建基于HSSTHP高速接口的视频传输架构,包括视频数据组包模块、HSSTHP IP核配置调用、接收数据对齐模块、视频数据解包模块等部分,总体代码架构如下:

基于HSSTHP高速接口的视频传输架构顶层接口核参数配置如下:

本设计共例化了2路HSSTHP,所以2路HSSTHP的收发回环方式也做了灵活的参数化配置,如果你只需要1路HSSTHP,则可删除另一路,如果你想例化更多路HSSTHP,则可根据上述设计方法扩展,十分方便;

HSSTHP IP 简介

关于HSSTHP介绍最详细的肯定是紫光同创官方的《Titan2 系列产品 HSSTHP IP用户指南》,我们以此来解读:

Titan2系列产品内置了高速串行接口模块,即 HSSTHP。除了 PMA,HSSTHP还集成了丰富的 PCS功能,可灵活应用于各种串行协议标准,每通道的收发速度高达12.5 Gb/s,收发器支持不同的串行传输接口或协议,支持 PCI1.0,PCI2.0,XAUI,千兆以太网,CPRI,SRIO 等协议,官方宣称可对标Xilinx的GTX;

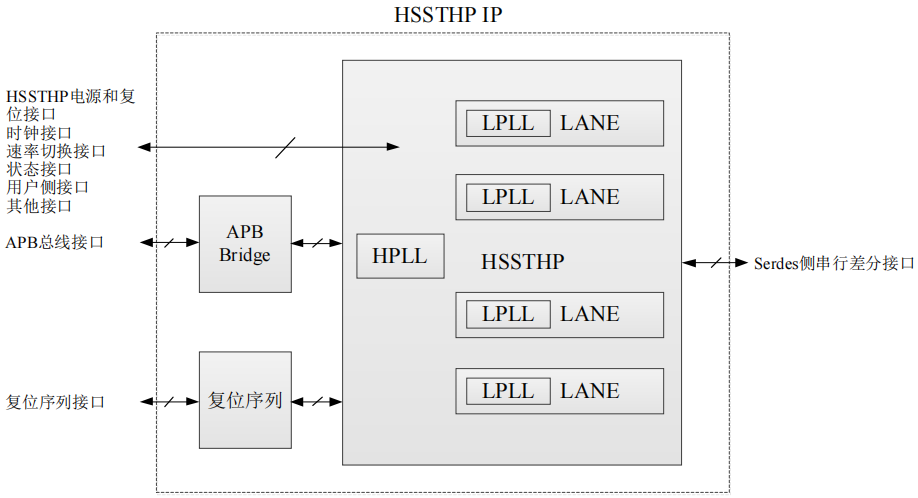

HSSTHP基本结构

紫光同创FPGA的HSSTHP模仿了Xilinx的GTX,HSSTHP基本结构如下:

每个 HSSTHP由两个 PLL 和四个收发 LANE 组成,其中每个 LANE 有两个子层:PCS(物理编码子层)和 PMA(物理媒体连接子层),PCS 子层包含 8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路;PMA 层主要进行串并、并串转换、预加重、去加重、串行数据的发送和数据时钟的提取,包括四个组件:PCS Transmitter,PMATransmitter,PCS Receiver,PMA Receiver。PCS Transmitter 和 PMA Transmitter组成发送通路,PCS Receiver 和 PMA Receiver 组成接收通路;HSSTLP 中的四个收发 LANE 共享 PLL0 和 PLL1,每个发送或者接收 LANE 都可以独立选择 PLL0 或者 PLL1,PLL 工作频率范围参见《Titan2 系列产品 HSSTHP IP用户指南》。PLL0 和 PLL1 都各自对应有一对外部差分参考时钟输入,每个 PLL 还可以选择来自另一个 PLL 的参考时钟或者来自 Fabric 的时钟作为参考时钟输入(Fabric 逻辑时钟做参考时钟,仅用于内部测试);PLL 输出频率支持动态再分频,以适应 Data Rate 范围。

HSSTHP发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

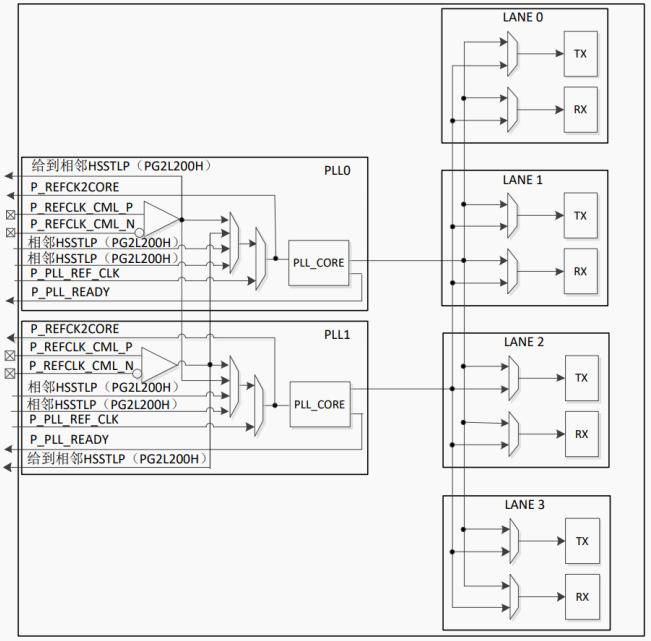

HSSTHP的参考时钟

HSSTHP参考时钟源选择的结构示意图如下:

HSSTHP支持PLL0、PLL1和LANE TX/RX 参考时钟的灵活选择:每个HSSTHP都有两对专用的差分参考时钟输入管脚 P_REFCK0P/P_REFCK0N和P_REFCK1P/P_REFCK1N,PLL 也可以选择来自 Fabric 的时钟P_PLL0_REF_CLK,P_PLL1_REF_CLK(Fabric 逻辑时钟做参考时钟,仅用于内部测试),仅Titan2器件支持选择来自相邻HSSTHP的参考时钟,通过PMA_PLL_REG_REFCLK_SEL和PMA_PLL_REG_CML_CLK_OUT_EN配置,PG2L 系列 25H、50H、100H 不支持这种用法,LANE TX,RX可以各自独立选择来自PLL0或者PLL1输出的时钟;专用时钟输入管脚P_REFCK0P/P_REFCK0N 和

P_REFCK1P/P_REFCK1N也可以通过端口P_PLL0_REFCK2CORE和P_PLL1_REFCK2CORE 输出到Fabric;

HSSTHP发送接口

紫光同创官方的《Titan2 系列产品 HSSTHP IP用户指南》详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲HSSTHP例化时留给用户的发送部分需要用到的接口;用户只需要关心发送接口的时钟和数据即可,以例化2路HSSTHP为例,经本博主优化,用户只需要关心如下HSSTHP发送接口即可快速使用HSSTHP;

HSSTHP接收接口

紫光同创官方的《Titan2 系列产品 HSSTHP IP用户指南》详细介绍了接收处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲HSSTHP例化时留给用户的发送部分需要用到的接口;用户只需要关心接收接口的时钟和数据即可,以例化2路HSSTHP为例,经本博主优化,用户只需要关心如下HSSTHP接收接口即可快速使用HSSTHP;

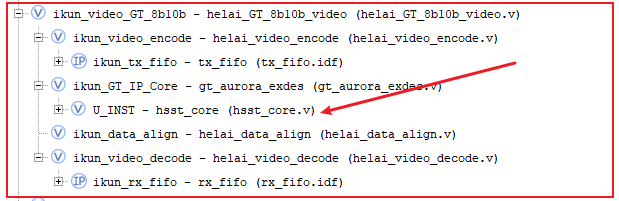

HSSTHP IP核调用和使用

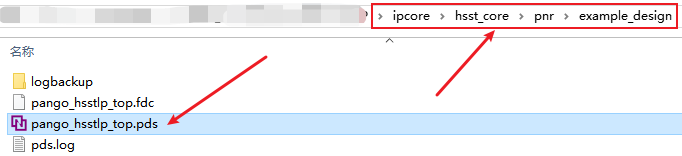

HSSTHP的使用比较特殊,需要先调用配置IP,然后再打开官方生成的Example工程,然后修改Example工程,删除数据生成和数据比对模块,再添加用户需要的信号逻辑,用起来比较麻烦;因为HSSTHP IP配置后并不能直接使用,需要修改其内部代码才能使用,这也是国产FPGA的不成熟之处;HSSTHP IP核配置调用在工程种位置如下:

IP配置好后,打开打开官方生成的Example工程,位置如下:

!!!注意

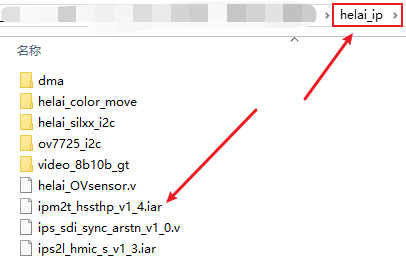

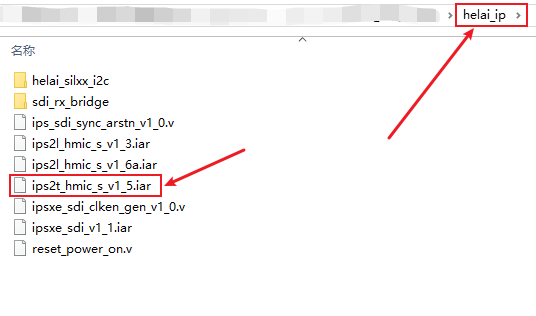

本设计使用的HSSTHP IP版本为ipm2t_hssthp_v1_4,安装包以放在资料中,请用户自行安装,安装包目录如下:

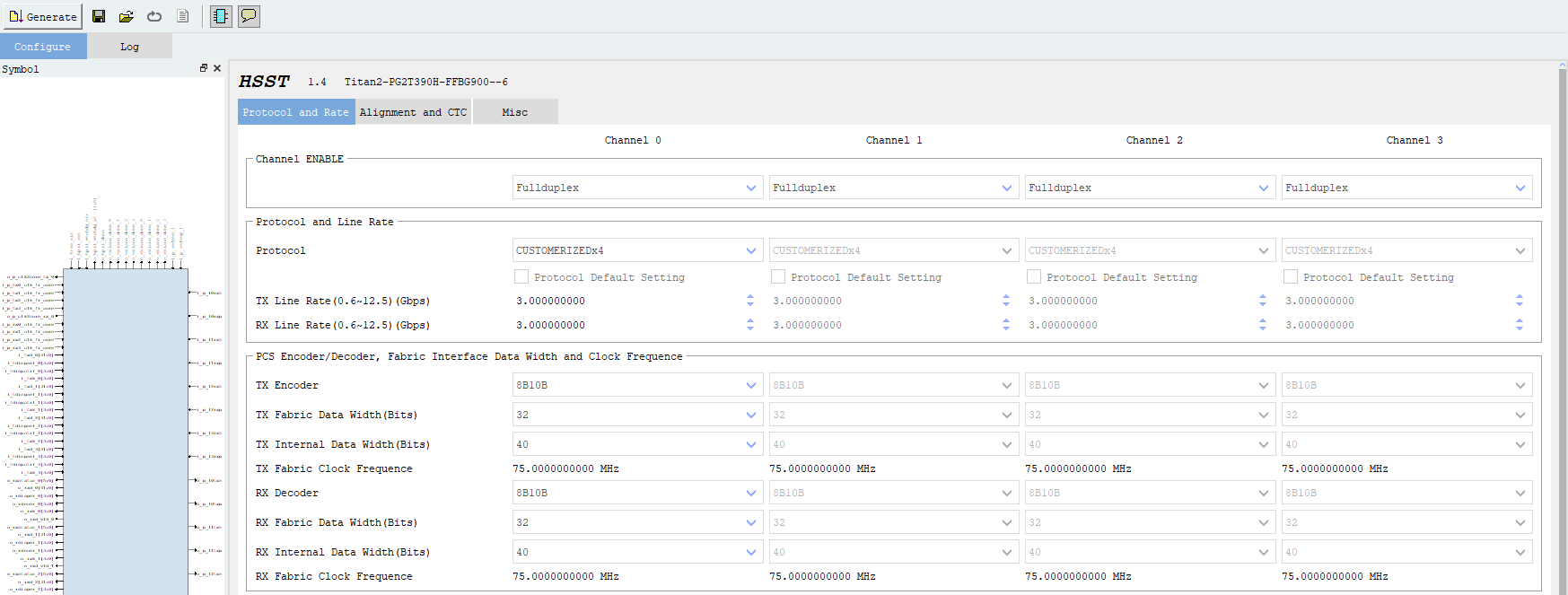

HSSTHP IP核调用和使用很简单,通过PDS的UI界面即可完成,如下:

这里对上图的标号做解释:

1:线速率,根据自己的项目需求来,HSSTHP线速率最高12.5G,由于我的项目是视频传输,所以在HSSTHP的速率范围内均可,为了通用性,我在工程中配置为3G;

2:参考时钟,这个得根据你的原理图来,可以是80M、125M、148.5M、156.25M等等,我的开发板是125M;

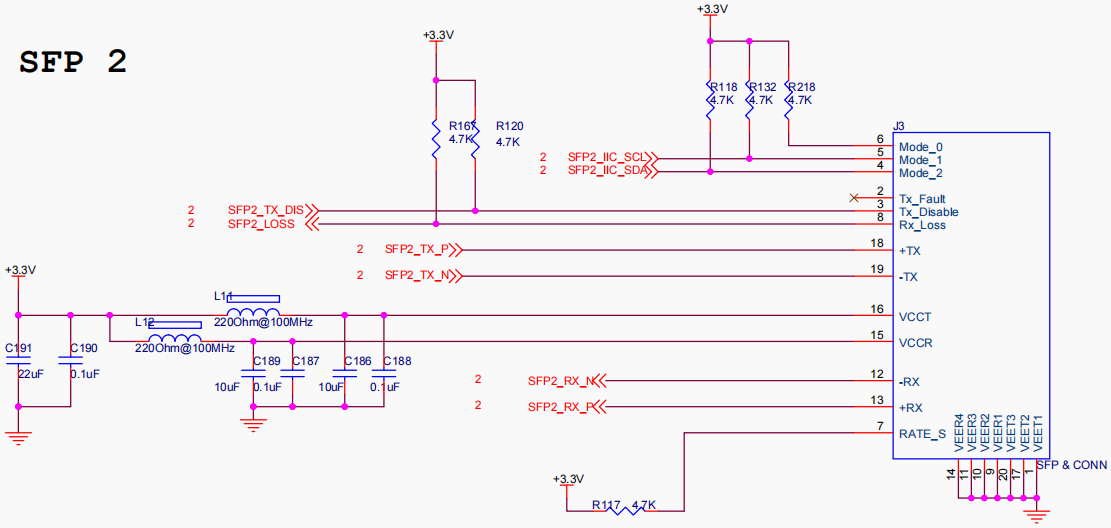

4:HSSTHP通道(Channel)的绑定,这个很重要,他的绑定参考依据有两个,一是你的开发板原理图,二是官方的参考资料《Titan2 系列产品 HSSTHP IP用户指南》;我的板子原理图如下:

数据对齐

由于HSSTHP资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;数据对齐模块顶层接口如下:

视频数据解包

数据解包是数据组包的逆过程,代码位置如下:

HSSTHP解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;由于数据解包是数据组包的逆过程,所以这里不再过多赘述,视频数据解包模块顶层接口如下:

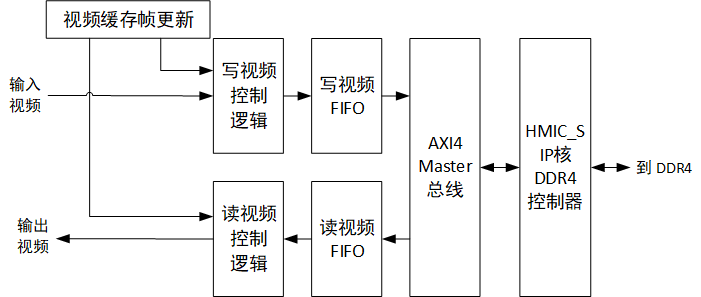

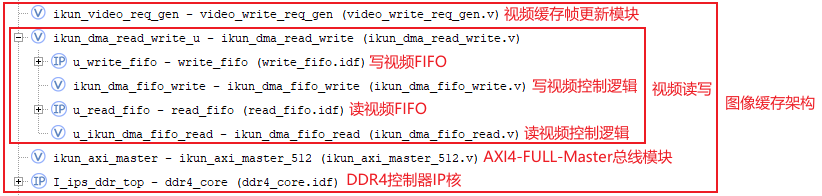

图像缓存架构

此模块为点对点视频接收端工程所独有;图像缓存架构实现的功能是将输入视频缓存到板载DDR4中再读出送后续模块,目的是实现视频同步输出,实现输入视频到输出视频的跨时钟域问题,更好的呈现显示效果;由于调用了紫光官方的HMIC_S IP核作为DDR4控制器,所以图像缓存架构就是实现用户数据到HMIC_S的桥接作用;架构如下:

图像缓存架构由视频缓存帧更新模块+写视频控制逻辑+读视频控制逻辑+AXI4-FULL-Master总线模块组成;AXI4-FULL-Master总线模块实际上就是一个AXI4-FULL总线主设备,与HMIC_S IP核对接,HMIC_S IP核配置为AXI4-FULL接口;写视频控制逻辑、读视频控制逻辑实际上就是一个视频读写状态机,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;写视频控制逻辑每次写入一次突发传输的视频数据,记作Y,即每次向DDR4中写入Y个像素,写M×N÷Y次即可完成1帧图像的缓存,读视频与之一样;同时调用两个FIFO实现输入输出视频的跨时钟域处理,使得用户可以忽略AXI4内部代码,以简单地像使用FIFO那样操作AXI4总线,从而达到读写DDR的目的,进而实现视频缓存;本设计图像缓存方式为4帧缓存;图像缓存模块代码架构如下:

DDR4控制器IP安装包以附带资料包中,如下:

HDMI输出架构

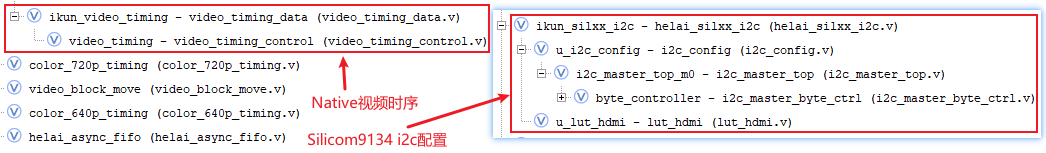

HDMI输出包括Native视频时序和HDMI编码,Native视频时序的作用是产生传统VGA的、RGB的视频流;HDMI编码采用Silicom9134芯片编码方式,FPGA仅需输出RGB视频流即可;HDMI输出代码架构如下:

工程源码架构

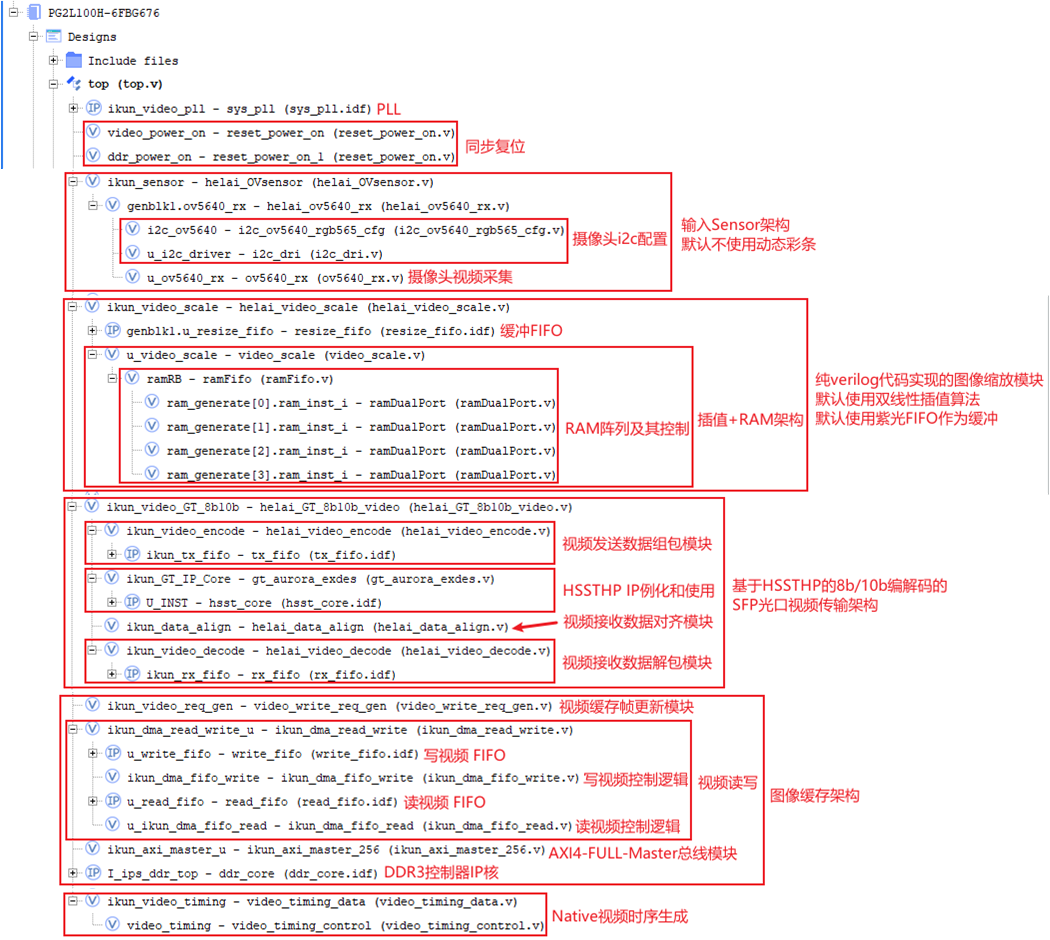

以工程2为例,工程源码架构如下:

4、PDS工程源码1详解:OV7725输入版本

开发板FPGA型号:紫光同创–PG2T390H-6FFBG900;

开发环境:Pango Design Suite 2021.1

输入:OV7725摄像头或FPGA内部动态彩条,分辨率640x480@60Hz;

输出:HDMI,Silicom9134芯片编码,1920x1080黑色背景下叠加显示缩放后的图像;

回环光口类型:SFP+光口;

高速接口类型:HSSTHP,线速率3Gbps;

高速接口编解码协议:8b/10b编解码;

图像缩放方案:纯Verilog图像缩放;

图像缩放实例:640x480缩放到1920x1080,其他分辨率缩放可自行修改;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程作用:紫光同创FPGA图像视频采集系统;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTHP光口视频传输的设计能力,以便能够移植和设计自己的项目;

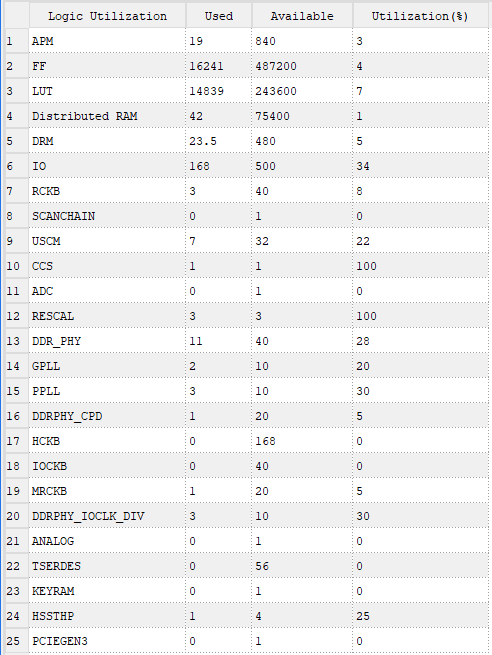

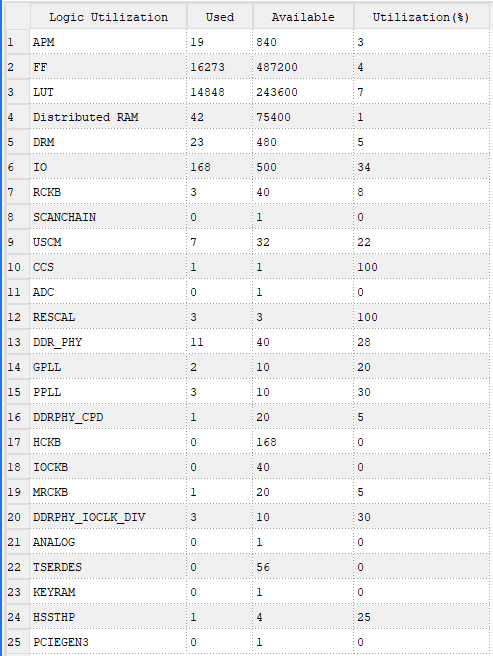

工程的资源消耗和功耗如下:

5、PDS工程源码2详解:OV5640输入版本

开发板FPGA型号:紫光同创–PG2T390H-6FFBG900;

开发环境:Pango Design Suite 2021.1

输入:OV5640摄像头或FPGA内部动态彩条,分辨率1280x720@30Hz;

输出:HDMI,Silicom9134芯片编码,1920x1080黑色背景下叠加显示缩放后的图像;

回环光口类型:SFP+光口;

高速接口类型:HSSTHP,线速率3Gbps;

高速接口编解码协议:8b/10b编解码;

图像缩放方案:纯Verilog图像缩放;

图像缩放实例:640x480缩放到1920x1080,其他分辨率缩放可自行修改;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程作用:紫光同创FPGA图像视频采集系统;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTHP光口视频传输的设计能力,以便能够移植和设计自己的项目;

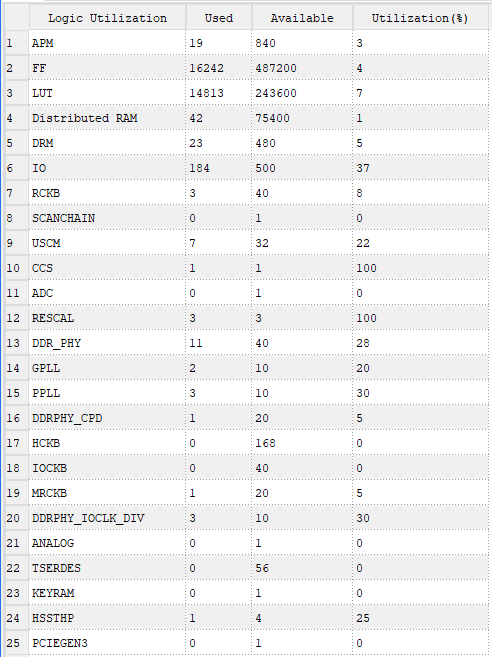

工程的资源消耗和功耗如下:

6、PDS工程源码3详解:HDMI输入版本

开发板FPGA型号:紫光同创–PG2T390H-6FFBG900;

开发环境:Pango Design Suite 2021.1

输入:HDMI或者FPGA内部动态彩条,silicom9011芯片解码方案,分辨率1920x1080@60Hz,笔记本电脑模拟输入源;

输出:HDMI,Silicom9134芯片编码,1920x1080黑色背景下叠加显示缩放后的图像;

回环光口类型:SFP+光口;

高速接口类型:HSSTHP,线速率3Gbps;

高速接口编解码协议:8b/10b编解码;

图像缩放方案:纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720,其他分辨率缩放可自行修改;

图像缓存方案:纯Verilog图像缓存,4帧缓存;

工程作用:紫光同创FPGA图像视频采集系统;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现HSSTHP光口视频传输的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

7、上板调试验证并演示

准备工作

你需要有以下装备才能移植并测试该工程代码:

1:FPGA开发板;

2:OV7725或OV5640摄像头或笔记本电脑,没有则请使用FPGA内部生成的彩条;

3:HDMI传输线;

4:HDMI显示,要求分辨率支持1920x1080;

SFP光模块和光纤;

我的开发板了连接如下:

HSSTHP光口视频缩放传输效果演示

HSSTHP光口视频缩放传输效果演示如下:

紫光-SFP缩放

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

相关文章:

紫光同创FPGA实现HSSTHP光口视频传输+图像缩放,基于Aurora 8b/10b编解码架构,提供3套PDS工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目紫光同创FPGA相关方案推荐我这里已有的 GT 高速接口解决方案Xilinx系列FPGA实现GTP光口视频传输方案推荐Xilinx系列FPGA实现GTX光口视频传输方案推荐Xilinx系列FPGA实…...

怎样避免住宅IP被平台识别

要有效避免住宅IP被平台识别,需从IP质量选择、环境参数伪装、行为模式模拟、技术细节处理等多维度构建防御体系。以下是基于行业实践的综合性解决方案: 一、确保住宅IP的高纯净度 选择真实家庭网络IP 验证IP是否归属真实家庭宽带(非机房IP伪装…...

Java的JDK、JRE、JVM三者间的关系)

(1-1)Java的JDK、JRE、JVM三者间的关系

目录 1.JVM (Java 虚拟机) 2. JRE (Java运行时环境) 3. JDK(Java开发工具包) 1.JVM (Java 虚拟机) JVM可看作程序的自行引擎,将字节码转化为特定平台上的机器代码执行 功能: 加载并执行字节码文件:JVM从 .class文件中加载字节码…...

:从理论到实践)

机器学习之嵌入(Embeddings):从理论到实践

机器学习之嵌入(Embeddings):从理论到实践 摘要 本文深入探讨了机器学习中嵌入(Embeddings)的概念和应用。通过具体的实例和可视化展示,我们将了解嵌入如何将高维数据转换为低维表示,以及这种转换在推荐系统、自然语言处理等领域的实际应用…...

)

【漫话机器学习系列】245.权重衰减(Weight Decay)

权重衰减(Weight Decay)详解 | L2正则化的奥秘 在深度学习和机器学习模型训练中,我们常常面临 过拟合(Overfitting) 的问题。 为了提高模型在未见数据上的泛化能力,正则化(Regularization&…...

配合gem5)

DSENT (Design Space Exploration of Networks Tool) 配合gem5

概述 DSENT是一种建模工具,旨在快速探索电子和新兴的片上光电网络(NoC)的设计空间。它为各种网络组件提供分析和参数化模型,并可在一系列技术假设下移植。给定架构级参数,DSENT从电气和光学构建块分层构建指定的模型,并输出详细的功率和面积估计。 版本 当前:0.91(2…...

汽车加气站操作工考试知识点总结

汽车加气站操作工考试知识点总结 加气站基本知识 了解加气站类型(CNG、LNG、LPG等)及其特点。 熟悉加气站的主要设备,如储气瓶组、压缩机、加气机、卸气柱、安全阀等。 掌握加气站工艺流程,包括卸气、储气、加压、加气等环节。…...

云蝠智能大模型语音交互智能体赋能电视台民意调研回访:重构媒体数据采集新范式

一、行业痛点与技术挑战 在媒体融合加速推进的背景下,电视台传统民意调研回访面临三大核心挑战: 人工成本高企:某省级卫视调研部门数据显示,人工外呼日均触达量仅 300-500 人次,人力成本占比超过 60%。数据质量参差&…...

数据可视化与数据编辑器:直观呈现数据价值

在当今数字化时代,数据可视化已成为企业洞察数据价值的关键手段。它与数据编辑器紧密结合,不仅能将复杂的数据转化为直观的图形、图表,以一种更加易懂的方式展现数据的规律、趋势和关系,还能借助数据编辑器随时对原始数据进行调整…...

)

ESP32蓝牙开发笔记(十四)

在 ESP32 的 BLE 开发中,esp_ble_gatts_add_char 是用于向 GATT 服务中添加特征(Characteristic)的核心函数。以下是该函数的详细说明、参数解析及示例代码: 函数原型 esp_err_t esp_ble_gatts_add_char(uint16_t service_handle…...

idea连接mongodb配置schemas

1. idea连接mongodb配置显示的schemas 默认展示 Default databse, 可以在此设置...

MySQL的函数

函数其实就是方法,就是别人封装好的东西 熟能生巧,加油!!!完整代码在最后。 一、聚合函数 - group_concat() 就是对数据进行分组然后合并 二、数学函数 函数很多,大家至少看一遍,有一个大概印…...

)

苍穹外卖(订单状态定时处理、来单提醒和客户催单)

订单状态定时处理、来单提醒和客户催单 Spring Task cron表达式 入门案例 ①导入maven坐标 spring-context(已存在) ②启动类添加注解 EnableScheduling 开启任务调度 ③自定义定时任务类 订单状态定时处理 需求分析 代码开发 自定义定…...

SpringBoot应急物资供应管理系统开发设计

概述 基于SpringBoot的应急物资供应管理系统功能完善,采用了现代化的开发框架,非常适合学习或直接应用于实际项目。 主要内容 5.1 管理员功能模块 管理员可通过登录界面进入系统,使用用户名、密码和角色信息进行身份验证。登录后…...

与过滤器(filters))

spring cloud gateway 断言(Predicates)与过滤器(filters)

断言 在 Spring Cloud Gateway 中,内置的断言(Predicates)用于对请求进行条件匹配。Spring Cloud Gateway 提供了多种内置断言,可以根据请求的路径、头部、方法等条件来决定是否将请求路由到特定的处理器。 内置断言 基于路径 …...

-04-(11-2))

MySQL-数据查询(多表连接JOIN)-04-(11-2)

学生表 学号 姓名 班级 课程编号 课程名称 是否结课 create table xs( xs_id int auto_increment primary key, xs_xm varchar(30), xs_bj varchar(30), xs_kcbh varchar(30), xs_kcmc varchar(30), xs_sfjk varchar(30) );insert xs values(1,张三,24大数据技术,1001,MYS…...

解决leetcode第3537题填充特殊网格

3537.填充特殊网格 难度:中等 问题描述: 给你一个非负整数N,表示一个x的网格。你需要用从0到-1的整数填充网格,使其成为一个特殊网格。一个网格当且仅当满足以下所有条件时,才能称之为特殊网格: 右上角…...

C++_MD5算法

文章目录 概要代码应用 概要 MD5算法在数据加密、一致性哈希、安全性验证等技术中有广泛的应用。 MD5算法的原理可简要的叙述为:MD5码以512位分组来处理输入的信息,且每一分组又被划分为16个32位子分组,经过了一系列的处理后,算法…...

深入理解C++ Lambda表达式:从基础到高级应用

在现代C编程中,Lambda表达式已经成为不可或缺的特性之一。自C11引入以来,Lambda极大地改变了我们编写函数对象和回调的方式,使代码更加简洁、表达力更强。本文将全面探讨C Lambda表达式的各个方面,从基础语法到高级应用场景&#…...

蓝桥杯 20. 倍数问题

倍数问题 原题目链接 题目描述 众所周知,小葱同学擅长计算,尤其擅长判断一个数是否是另一个数的倍数。但当面对多个数时,他就比较苦恼了。 现在小葱给了你 n 个数,希望你从中找出三个数,使得这三个数的 和是 K 的倍…...

)

2025最新出版 Microsoft Project由入门到精通(二)

目录 项目五部曲 第一步:先设置项目的信息和日历 项目的开始结束日期 项目的日历 默认日历改为全年无休(除法定节假日) 六天工作制/七天工作制设置方法 七天工作制的设置方法 全年无休工作制的设置方法 大小周交替日历设置方法&…...

从人体姿态到机械臂轨迹:基于深度学习的Kinova远程操控系统架构解析

在工业自动化、医疗辅助、灾难救援与太空探索等前沿领域,Kinova轻型机械臂凭借7自由度关节设计和出色负载能力脱颖而出。它能精准完成物体抓取、复杂装配和精细操作等任务。然而,实现人类操作者对Kinova机械臂的直观高效远程控制一直是技术难题。传统远程…...

【ABAP】定时任务DEBUG方法

事物码SM37 执行后,选中作业名,在输入框输入“JDBG”,进入调试模式(提前在需要的调试的程序设置断点)...

)

DDPM(Denoising Diffusion Probabilistic Models,去噪扩散概率模型)

简介 DDPM即去噪扩散概率模型(Denoising Diffusion Probabilistic Models),是一种生成式模型,在图像生成、视频生成等领域有广泛应用。以下是其详细介绍: 原理 DDPM的核心思想是通过在数据上逐步添加噪声来破坏数据…...

C26-冒泡排序法

一 算法步骤 外层循环:控制遍历轮数(共n-1轮,n为数组长度)内层循环:每轮比较相邻的元素,若顺序错误则交换,将当前一轮最大(最小)的元素移至末尾 二 实例 代码 #include <stdio.h> int main() {//数组及相关数据定义int arr[4]{12,4,78,23};int i;int j;int temp;int …...

CentOS 7.9 安装详解:手动分区完全指南

CentOS 7.9 安装详解:手动分区完全指南 为什么需要手动分区?CentOS 7.9 基本分区说明1. /boot/efi 分区2. /boot 分区3. swap 交换分区4. / (根) 分区 可选分区(进阶设置)5. /home 分区6. /var 分区7. /tmp 分区 分区方案建议标准…...

--- GPT3: Language Models are Few-Shot Learners)

大模型系列(五)--- GPT3: Language Models are Few-Shot Learners

论文链接: Language Models are Few-Shot Learners 点评: GPT3把参数规模扩大到1750亿,且在少样本场景下性能优异。对于所有任务,GPT-3均未进行任何梯度更新或微调,仅通过纯文本交互形式接收任务描述和少量示例。然而&…...

BK精密电源操作软件 9130BA系列和手侧user manual

BK精密电源操作软件 9130BA系列和手侧user manual...

MATLAB的cvpartition函数用法

1. 函数作用 cvpartition 将数据集划分为训练集和测试集,支持多种交叉验证方法,包括: Hold-Out验证:单次划分(如70%训练,30%测试)K折交叉验证:数据分为K个子集,依次用其…...

含铜废水回收的好处体现

一、环境保护:减少污染,守护生态安全 降低重金属污染 含铜废水若直接排放,铜离子会通过食物链富集,对水生生物和人体造成毒性影响(如肝肾损伤)。回收处理可去除废水中90%以上的铜离子,显著降低…...

C++20新特新——02特性的补充

虽然上节我们介绍了不少关于协程的特点,但是大家可能对协程还是不是很了解,没关系,这里我们再对其进行补充,详细讲解一下; 一、协程函数与普通函数的区别 这里我们再回归到问题:普通函数和协程在这方面的…...

【c++】 我的世界

太久没更新小游戏了 给个赞和收藏吧,求求了 要游戏的请私聊我 #include <iostream> #include <vector>// 定义世界大小 const int WORLD_WIDTH 20; const int WORLD_HEIGHT 10;// 定义方块类型 enum BlockType {AIR,GRASS,DIRT,STONE };// 定义世界…...

)

Redis从入门到实战 - 高级篇(上)

一、分布式缓存 1. 单点Redis的问题 数据丢失问题:Redis是内存存储,服务重启可能会丢失数据 -> 实现Redis数据持久化 并发能力问题:单节点Redis并发能力虽然不错,但也无法满足如618这样的高并发场景 -> 搭建主从集群&…...

常见的卷积神经网络列举

经典的卷积神经网络(CNN)在深度学习发展史上具有重要地位,以下是一些里程碑式的模型及其核心贡献: 1. LeNet-5(1998) 提出者:Yann LeCun特点: 首个成功应用于手写数字识别ÿ…...

Linux如何安装AppImage程序

Linux如何安装AppImage程序 文章目录 Linux如何安装AppImage程序 在 Linux 中,.AppImage 是一种便携式的应用程序格式,无需安装即可运行。 1.赋予该文件可执行权限 可以使用下列命令,赋予可执行权限 # 举个例子 chmod x /path/to/MyApp.App…...

人工智能如何进行课堂管理?

人工智能如何协助老师课堂管理? 第一步:在腾讯元宝对话框中输入:如何协助老师进行课堂管理,通过提问,我们了解了老师高效备课可以从哪些方面入手,提高效率。 第二步:编辑问题进行提问…...

如何理解参照权

在管理学和组织行为学中,“参照权力”(Referent Power)是一种非常重要的权力来源,它属于非强制性权力的一种,主要基于个人特质和人际关系。以下是对参照权力的详细解释: 一、定义 参照权力是指一个人由于…...

从一次被抄袭经历谈起:iOS App 安全保护实战

如何保护 iOS App 的最后一道防线:那些你可能忽略的混淆技巧 如果你曾认真反编译过别人的 .ipa 文件,很可能会有这种感受:“哇,这代码也太干净了吧。” 类名像 UserManager,方法名是 getUserToken,甚至资源…...

从交互说明文档,到页面流程图设计全过程

依据交互说明文档绘制页面流程图,能够将抽象的交互逻辑转化为可视化、结构化的表达,为开发、测试及团队协作提供清晰指引。接下来,我们以外卖 App 订单确认页为例,详细拆解从交互说明文档到完整页面流程图的设计全过程。 一、交互…...

fedora系统详解详细版本

Fedora 系统详解:从起源到实践的深度解析 一、Fedora 概述:开源社区的技术先锋 Fedora 是由 Fedora 项目社区 开发、Red Hat 公司赞助 的 Linux 发行版,以 自由开源、技术前沿 和 稳定性平衡 著称。它是 Red Hat Enterprise Linuxÿ…...

)

2025-05-07-FFmpeg视频裁剪(尺寸调整,画面比例不变)

原比例如图 原比例如图裁剪后的比例 代码: 方法一:极速 ffmpeg -i input.mp4 -vf "crop1080:750:0:345" -c:v libx264 -preset ultrafast -c:a copy output.mp4关键参数说明: vf “crop宽:高❌y”:定义裁剪区域。 …...

RISC-V JTAG:开启MCU 芯片调试之旅

在当今电子科技飞速发展的时代, MCU 芯片成为众多企业追求技术突破与创新的关键领域。而芯片的调试过程则是确保其性能与可靠性的重要环节。本文以国科安芯自研 AS32A601为例,旨在详细记录基于 RISC-V 架构的 MCU 芯片JTAG 调试过程及操作,为…...

51单片机快速成长路径

作为在嵌入式领域深耕18年的工程师,分享一条经过工业验证的51单片机快速成长路径,全程干货无注水: 一、突破认知误区(新手必看) 不要纠结于「汇编还是C」:现代开发90%场景用C,掌握指针和内存管…...

idea左侧项目资源管理器不见了处理

使用idea误触导致,侧边栏和功能栏没了,如何打开? 1.打开文件(File) 2. 打开设置(Settings) 3.选择Appearance&Behavior--->Appearance划到最下面,开启显示工具栏和左侧并排布…...

给小白的AI Agent 基本技术点分析与讲解

引言:重塑交互与自动化边界的 AI Agent 在人工智能技术飞速发展的浪潮中,AI Agent(智能体)概念的兴起标志着自动化和人机交互正迈向一个全新的阶段。传统的软件系统通常被设计来执行精确预设的指令序列,它们强大且高效…...

[特殊字符] 深入解析:Go 与 Rust 中的数组与动态集合结构

在 Go 和 Rust 这两种现代语言中,数组和动态集合(如切片或 Vec)是处理数据的基础工具。虽然它们都提供了高效的内存访问能力,但设计理念却截然不同: Go 更注重灵活性和性能,允许开发者直接操作底层指针和容…...

C25-数组应用及练习

第一题 题目: 代码 #include <stdio.h> int main() {//数组及相关数据定义int arr[10];int i;//基于循环的数组数据输入for(i0;i<10;i){arr[i]i;}//基于循环的数组数据输出for(i9;i>0;i--){printf("%d ",arr[i]);}return 0; }结果 第二题 题目 代码 …...

技术)

Soft Mask(软遮罩)技术

一、概述 Soft Mask是一种技术或工具,主要用于实现平滑的边缘遮罩效果。它在不同的应用领域有不同的实现和定义 1.在Unity UI设计中 SoftMask是一款专为Unity设计的高级遮罩工具,它突破了传统Mask的限制,提供了更为灵活和细腻的UI遮罩解决方案…...

683SJBH基于J2EE的广州旅游管理系统

第1章 绪论 课题背景 自互联网internet成为一种革命性的大众媒体以来,其发展速度之快令人惊叹。而作为世界最大朝阳产业的旅游,当它与电子商务这一新兴模式相结合时,其潜藏的商业价值表露无遗。根据CNN(美国有线电视新闻网&…...

关于STM32 SPI收发数据异常

问题描述: STM32主板做SPI从机,另一块linux主板做主机,通信的时候发现从机可以正确接收到主机数据,但是主机接收从机数据时一直不对,是随机值。 问题原因: 刚发现问题的时候,用逻辑分析仪抓包…...