国产紫光同创FPGA实现SDI视频编解码+图像缩放,基于HSSTHP高速接口,提供2套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 本博已有的 SDI 编解码方案

- 本方案在Xilinx--Artix7系列FPGA上的应用

- 本方案在Xilinx--Kintex系列FPGA上的应用

- 本方案在Xilinx--Zynq系列FPGA上的应用

- 本方案在Xilinx--UltraScale系列FPGA上的应用

- 3、详细设计方案

- 设计原理框图

- SDI 输入设备

- Gv8601a 均衡器

- 紫光HSSTHP 高速接口

- 紫光12G-SDI IP核

- BT1120转RGB

- 图像缩放模块详解

- 图像缩放模块使用(重点阅读)

- 图像缩放模块仿真

- 图像缓存架构

- 视频读取控制

- HDMI输出

- RGB转BT1120

- Gv8500 驱动器

- SDI转HDMI盒子

- 工程源码架构

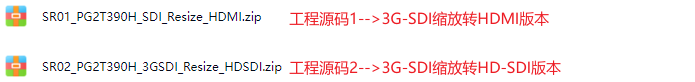

- 4、工程源码1详解-->3G-SDI缩放转HDMI版本

- 6、工程源码2详解-->3G-SDI缩放转HD-SDI版本

- 7、上板调试验证

- 准备工作

- 紫光同创FPGA SDI视频解码输出演示

- 9、福利:工程代码的获取

国产紫光同创FPGA实现SDI视频编解码+图像缩放,基于HSSTHP高速接口,提供2套工程源码和技术支持

1、前言

国产FPGA现状:

“苟利国家生死以,岂因祸福避趋之!”大洋彼岸的我优秀地下档员,敏锐地洞察到祖国的短板在于先进制程半导体的制造领域,于是本着为中华民族伟大复兴的中国梦贡献绵薄之力的初心,懂先生站在高略高度和长远角度谋划,宁愿背当代一世之骂名也要为祖国千秋万世谋,2018年7月,懂先生正式打响毛衣战,随后又使出恰勃纸战术,旨在为祖国先进制程半导体领域做出自主可控的战略推动;2019年初我刚出道时,还是Xilinx遥遥领先的时代(现在貌似也是),那时的国产FPGA还处于黑铁段位;然而才短短7年,如今的国产FPGA属于百家争鸣、百花齐放、八仙过海、神仙打架、方兴未艾、得陇望蜀、友商都是XX的喜极而泣之局面,此情此景,不得不吟唱老人家的诗句:魏武挥鞭,东临碣石有遗篇,萧瑟秋风今又是,换了人间。。。

目前对于国产FPGA优势有以下几点:

1:性价比高,与同级别国外大厂芯片相比,价格相差几倍甚至十几倍;

2:自主可控,国产FPGA拥有完整自主知识产权的产业链,从芯片到相关EDA工具;

3:响应迅速,FAE技术支持比较到位,及时解决开发过程中遇到的问题,毕竟中文数据手册;

4:采购方便,产业链自主可控,采购便捷;

FPGA实现SDI视频编解码现状:

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,比如Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,或者紫光同创系列FPGA的HSSTHP高速接口资源实现解串;优点是合理利用了FPGA资源,高速接口资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。本设计采用紫光同创Titan2系列FPGA的HSSTHP高速接口资源实现SDI视频解串和解码;

FPGA实现图像缩放现状:

FPGA实现图像缩放大体分两种方案,第一种是使用纯verilog代码实现,其优势是可移植性强,可广泛应用于各种型号FPGA,维护性强,通用性强,缺点是开发难度大,对开发者技术要求很高,功能和性能不够灵活;第二种是使用纯HLS代码实现,比如Xilinx的Video Processing Subsystem,其优势是开发难度小,对开发者技术要求很低,可快速实现部署,特别适用于Xilinx的Zynq系列FPGA,功能和性能很灵活,缺点是可移植性很差,目前仅限于Xilinx系列FPGA,维护性差,通用性差;本设计采用纯verilog代码方案实现双线性插值的图像缩放;

工程概述

本设计基于紫光同创的Titan2系列FPGA开发板实现SDI视频编解码,输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到FPGA开发板的BNC座子,然后同轴视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ的功能;然后差分SDI视频信号进入FPGA内部的HSSTHP高速资源,实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送紫光同创Titan2系列FPGA特有的12G–SDI IP核,进行SDI视频解码操作并输出BT1120视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;

本设计的目的是输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了两种输出方式,一种是HDMI输出,另一种是3G-SDI输出,这两种方式都需要对解码BT1120视频进行转RGB和图像缓存操作;本设计使用BT1120转RGB模块实现视频格式转换;然后对输入视频做图像缩放操作,图像缩放模块可实现任意比例缩放,支持临域插值和双线性插值2种算法,通过模块顶层参数选择,默认使用双线性插值;然后使用纯verilog实现的图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR4;图像从DDR4读出后,进入HDMI发送模块输出HDMI显示器,这是HDMI输出方式;或者经过RGB转BT1120模块实现视频格式转换,然后视频进入紫光同创Titan2系列FPGA特有的12G–SDI IP核,进行SDI视频编码操作并输出SDI视频,再经过FPGA内部的GTP高速资源,实现并行数据到高速串行的转换,本博称之为串化,差分高速信号再进入板载的Gv8500芯片实现差分转单端和驱动增强的功能,SDI视频通过FPGA开发板的BNC座子输出,通过同轴线连接到SDI转HDMI盒子连接到HDMI显示器,这是SDI输出方式;本博客提供2套工程源码,具体如下:

现对上述2套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为PG2T390H-6FFBG900;输入视频为3G-SDI相机或者HDMI转3G-SDI盒子,输入分辨率为1920x1080@60Hz,输入视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过HSSTHP高速接口将SDI视频解串为并行数据;再经过紫光同创Titan2系列FPGA特有的12G–SDI IP核将SDI解码BT1120数据;再经过BT1120转RGB模块将BT1120转换为RGB888视频;然后对输入视频做图像缩放操作,将原视频从1920x1080缩放到1280x720,您可修改缩放参数轻松缩放到其他分辨率,工程只是举例,修改方法博客有说明;再经过纯verilog实现的图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR4;然后从DDR45中读出视频送入送Silicom9134芯片实现RGB转HDMI输出,输出分辨率为1920x1080@60Hz,为了兼容缩放后的其他分辨率,本设计将背景分辨率设计为1920x1080,缩放后的图像叠加在其上显示即可,这也是本博主的创新点;最后通过HDMI显示器显示图像;该工程需要缓存,适用于紫光同创Titan2系列FPGA实现SDI转HDMI场景;

工程源码2

开发板FPGA型号为PG2T390H-6FFBG900;输入视频为3G-SDI相机或者HDMI转3G-SDI盒子,输入分辨率为1920x1080@60Hz,输入视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过HSSTHP高速接口将SDI视频解串为并行数据;再经过紫光同创Titan2系列FPGA特有的12G–SDI IP核将SDI解码BT1120数据;再经过BT1120转RGB模块将BT1120转换为RGB888视频;然后对输入视频做图像缩放操作,将原视频从1920x1080缩放到1280x720,您可修改缩放参数轻松缩放到其他分辨率,工程只是举例,修改方法博客有说明;再经过纯verilog实现的图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR4;然后从DDR4中读出视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过紫光同创Titan2系列FPGA特有的12G–SDI IP核,将BT1120视频编码为SDI视频;再经过HSSTHP高速接口资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1280x720@60Hz,这是HD-SDI标准;最后使用SDI转HDMI盒子连接到HDMI显示器显示;该工程需要缓存,适用于紫光同创Titan2系列FPGA实现3G-SDI转HD-SDI场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本方案在Xilinx–Artix7系列FPGA上的应用

本方案在Xilinx–Artix7系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Kintex系列FPGA上的应用

本方案在Xilinx–Kintex系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Zynq系列FPGA上的应用

本方案在Xilinx–Zynq系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–UltraScale系列FPGA上的应用

本方案在Xilinx–UltraScale系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

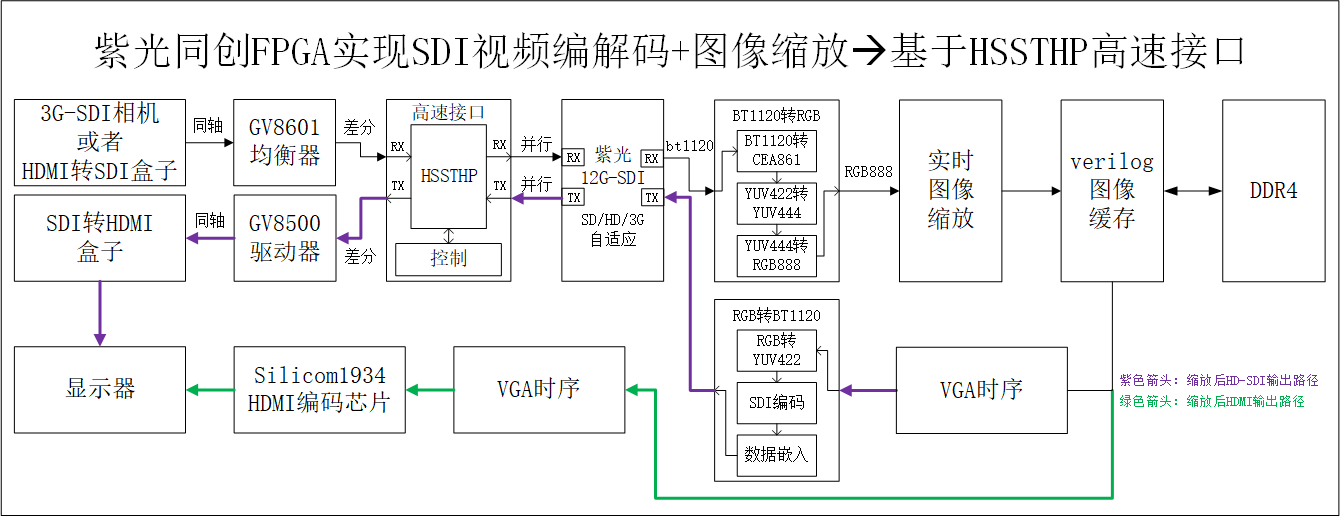

设计原理框图

设计原理框图如下:

!!!注意

!!!注意

紫色箭头:3G-SDI解码缩放转HD-SDI路径

绿色箭头:3G-SDI解码缩放转HDMI路径

SDI 输入设备

SDI 输入设备可以是SDI相机,代码兼容HD/SD/3G-SDI三种模式;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

Gv8601a 均衡器

Gv8601a芯片实现单端转差分和均衡EQ的功能,这里选用Gv8601a是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8601a均衡器原理图如下:

紫光HSSTHP 高速接口

本设计使用紫光同创Titan2系列FPGA特有的HSSTHP高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,HSSTHP起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,HSSTHP起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;

!!!注意

!!!注意

HSSTHP 高速接口的解串与串化功能集成在了紫光同创官方提供的12G-SDI IP核内部,所以这部分没有独立的代码例化;

紫光12G-SDI IP核

本设计使用紫光同创Titan2系列FPGA特有的12G-SDI IP核实现2G SDI视频编解码,该IP由紫光同创官方提供,集成度很高,具体性能如下:详情可参考《UG052007_Titan2_12GSDI_IP》;

SDI 接收端性能表现如下:

1、支持自动检测接收数据的 SDI 速率模式;

2、支持 SD-SDI、HD-SDI、3G-SDI、6G-SDI 和 12G-SDI 接收模式动态切换;

3、自动检测视频传输格式;

4、检测和捕捉 SMPTE 352 (Payload ID)包;

5、HD-SDI、3G-SDI、6G-SDI 和 12G-SDI 模式下,检查 CRC 错误;

6、SD-SDI 模式下,可选检查 EDH (SMPTE 165)包错误;

7、能够容忍最大±200ppm 频偏。

SDI 发送端性能表现如下:

1、支持 SD-SDI、HD-SDI、3G-SDI、6G-SDI 和 12G-SDI 发送模式动态切换;

2、HD-SDI、3G-SDI、6G-SDI 和 12G-SDI 模式下,支持 1 倍速率或者 1/1.001 倍速率 ,但不支持相互动态切换;

3、支持生成和插入 SMPTE 352 (Payload ID)包;

4、HD-SDI、3G-SDI、6G-SDI 和 12G-SDI 模式下,支持生成和插入 CRC 和 Line Numbers (LN);

5、SD-SDI 模式下,可选生成和插入 EDH (SMPTE 165)包。

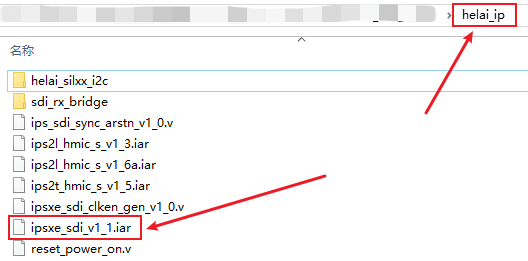

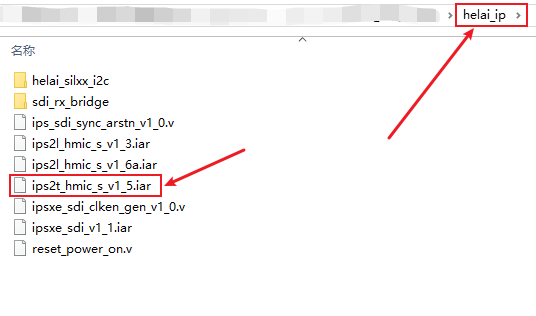

12G-SDI IP安装包以附带资料包中,如下:

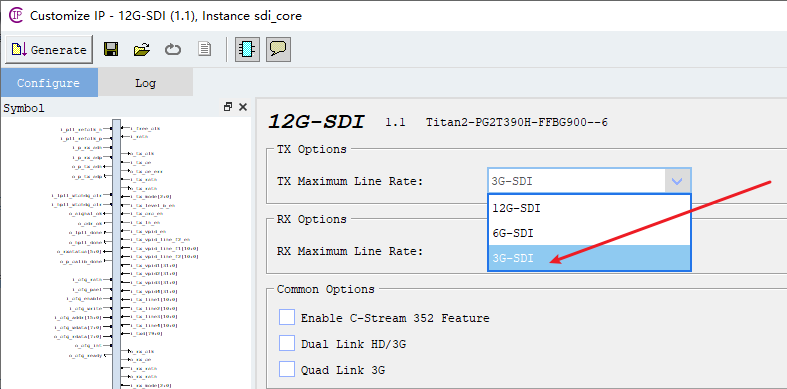

12G-SDI IP核使用配置十分简单,PDS的UI界面如下:

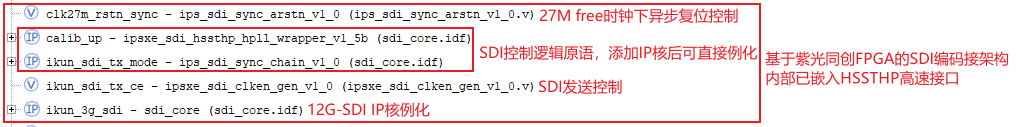

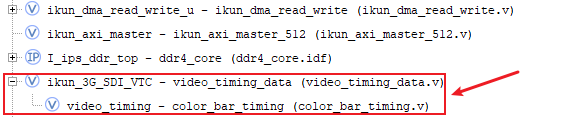

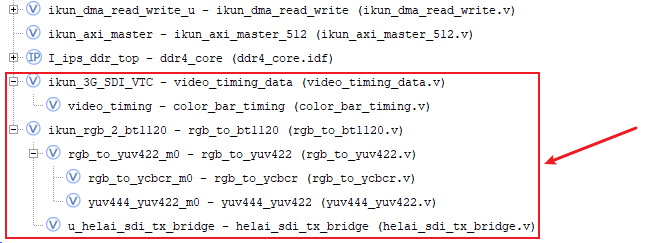

基于紫光同创FPGA 12G-SDI IP核的SDI视频编解码代码架构如下:

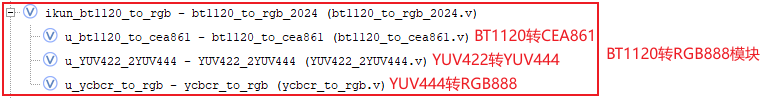

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

图像缩放模块详解

图像缩放模块功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

依据上图,图像缩放模块内部核心是例化了4个双口RAM,作用是缓存4行图像,以得到4个临近的像素,以此为基础做线性插值;如果是做图像放大操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中插入更多的像素点来扩大分辨率;如果是做图像缩小操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中删除更多的像素点来缩小分辨率;此外,前面描述的工作是实时的、整幅图像全部扫描式的进行,所以需要对RAM的读写操作进行精准控制;

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

代码里的配置如下:

图像缩放模块使用(重点阅读)

图像缩放模块使用非常简单,顶层代码里设置了四个参数,如下:

上图是将输入视频分辨率从1280x720缩放为1920x1080;

如果你想将输入视频分辨率从1280x720缩放为640x480;

则只需修改为如下:

再比如你想将输入视频分辨率从1280x720缩放为960x540;

则只需修改为如下:

在本博主这里,想要实现图像缩放,操作就是这么无脑简单,就该两个参数就能搞定貌似高大上的双线性插值图像缩放,这种设计、这种操作、这种工程源码,你还喜欢吗?

图像缩放模块仿真

图像缩放模块需要vivado和matlab联合仿真;

需要注意的是,仿真的目的是为了验证,这一步我已经替你们做完了,所以读者不再需要单独仿真,如果读者是在需要自己仿真玩玩儿,需要自己写仿真代码;vivado和matlab联合仿真详细步骤如下:

第一步:网上下载一张1280X720的图片,并用matlab将图片转换为RGB格式的txt文档;

第二步:在vivado下设计tstbench,将RGB格式的txt文档作为视频输入源给到图像缩放模块,并将缩放后的图像数据写入输出txt文档;

第二步:用matlab将输出txt文档转换为图片,并于原图一并输出显示以做比较;

根据以上方法得到以下仿真结果:

双线性插值算法原图1280X720缩小到800x600如下:

邻域插值算法原图1280X720缩小到800x600如下:

双线性插值算法原图1280X720放大到1920x1080如下:

邻域插值算法原图1280X720放大到1920x1080如下:

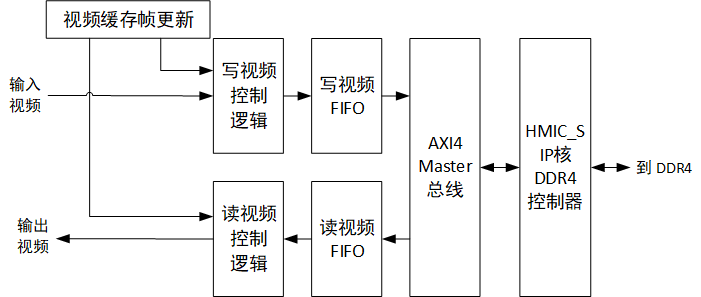

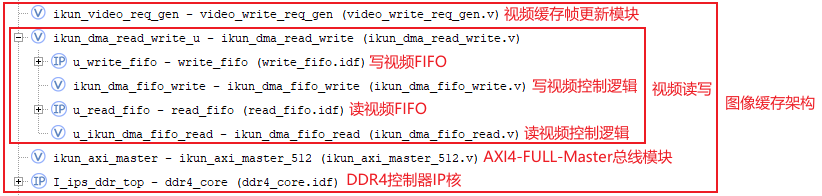

图像缓存架构

此模块为点对点视频接收端工程所独有;图像缓存架构实现的功能是将输入视频缓存到板载DDR4中再读出送后续模块,目的是实现视频同步输出,实现输入视频到输出视频的跨时钟域问题,更好的呈现显示效果;由于调用了紫光官方的HMIC_S IP核作为DDR4控制器,所以图像缓存架构就是实现用户数据到HMIC_S的桥接作用;架构如下:

图像缓存架构由视频缓存帧更新模块+写视频控制逻辑+读视频控制逻辑+AXI4-FULL-Master总线模块组成;AXI4-FULL-Master总线模块实际上就是一个AXI4-FULL总线主设备,与HMIC_S IP核对接,HMIC_S IP核配置为AXI4-FULL接口;写视频控制逻辑、读视频控制逻辑实际上就是一个视频读写状态机,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;写视频控制逻辑每次写入一次突发传输的视频数据,记作Y,即每次向DDR4中写入Y个像素,写M×N÷Y次即可完成1帧图像的缓存,读视频与之一样;同时调用两个FIFO实现输入输出视频的跨时钟域处理,使得用户可以忽略AXI4内部代码,以简单地像使用FIFO那样操作AXI4总线,从而达到读写DDR的目的,进而实现视频缓存;本设计图像缓存方式为4帧缓存;图像缓存模块代码架构如下:

DDR4控制器IP安装包以附带资料包中,如下:

视频读取控制

图像缓存架构使用VGA时序模块完成视频读取控制,VGA时序模块负责产生VGA时序,他有两个作用,一是控制图像缓存架构从DDR4中读出缓存的视频,二是将同步后的VGA视频送入下一级模块,在HDMI输出方式下VGA时序模块的像素时钟由用户提供;在SDI输出方式下VGA时序模块的像素时钟由紫光同创Titan2系列FPGA特有的12G-SDI IP核的发送用户时钟提供,在不同的SDI模式下像素时钟不同,比如在3G-SDI模式下像素时钟为148.5M,在HD-SDI的720P@60Hz模式下像素时钟为74.25M;HDMI输出方式下的VGA时序模块代码架构如下:

SDI输出方式下的VGA时序模块代码架构如下:

HDMI输出

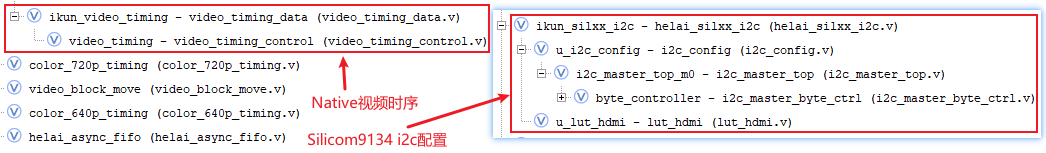

在HDMI输出方式下,HDMI输出包括Native视频时序和HDMI编码,Native视频时序的作用是产生传统VGA的、RGB的视频流;HDMI编码采用Silicom9134芯片编码方式,FPGA仅需输出RGB视频流即可;HDMI输出代码架构如下:

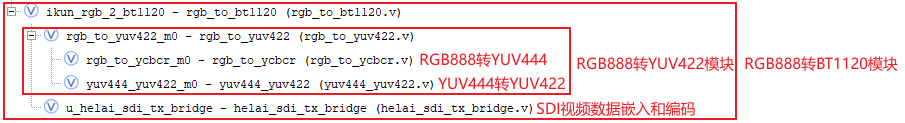

RGB转BT1120

在SDI输出方式下需要使用该模块;RGB转BT1200模块的作用是将用户侧的RGB视频转换为BT1200视频输出给SMPTE SD/HD/3G SDI IP核;RGB转BT1120模块由RGB888转YUV444模块、YUV444转YUV422模块、SDI视频编码模块、数据嵌入模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

Gv8500 驱动器

Gv8500芯片实现差分转单端和增强驱动的功能,这里选用Gv8500是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8500驱动器原理图如下:

SDI转HDMI盒子

在SDI输出方式下需要使用到SDI转HDMI盒子,因为我手里的显示器没有SDI接口,只有HDMI接口,为了显示SDI视频,只能这么做,当然,如果你的显示器有SDI接口,则可直接连接显示,我的SDI转HDMI盒子在某宝购买,不到100块;

工程源码架构

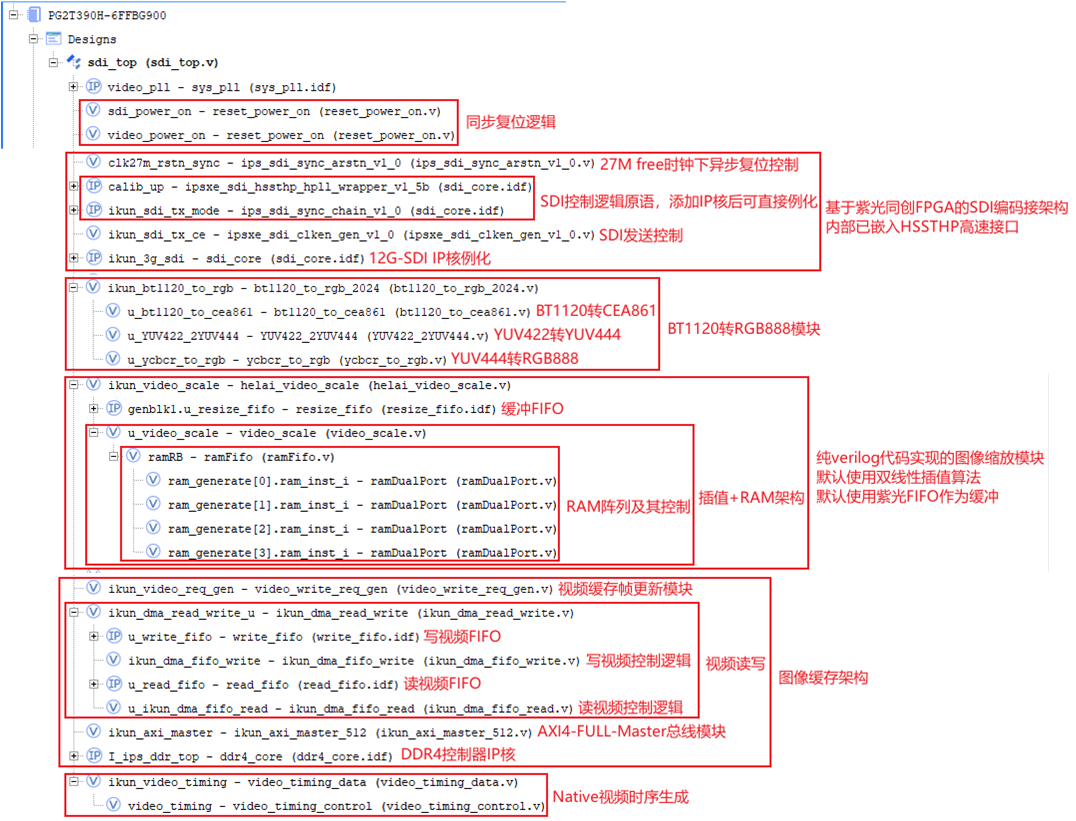

以工程源码1的SDI解码缩放转HDMI输出为例,工程源码架构如下,其他工程与之类似:

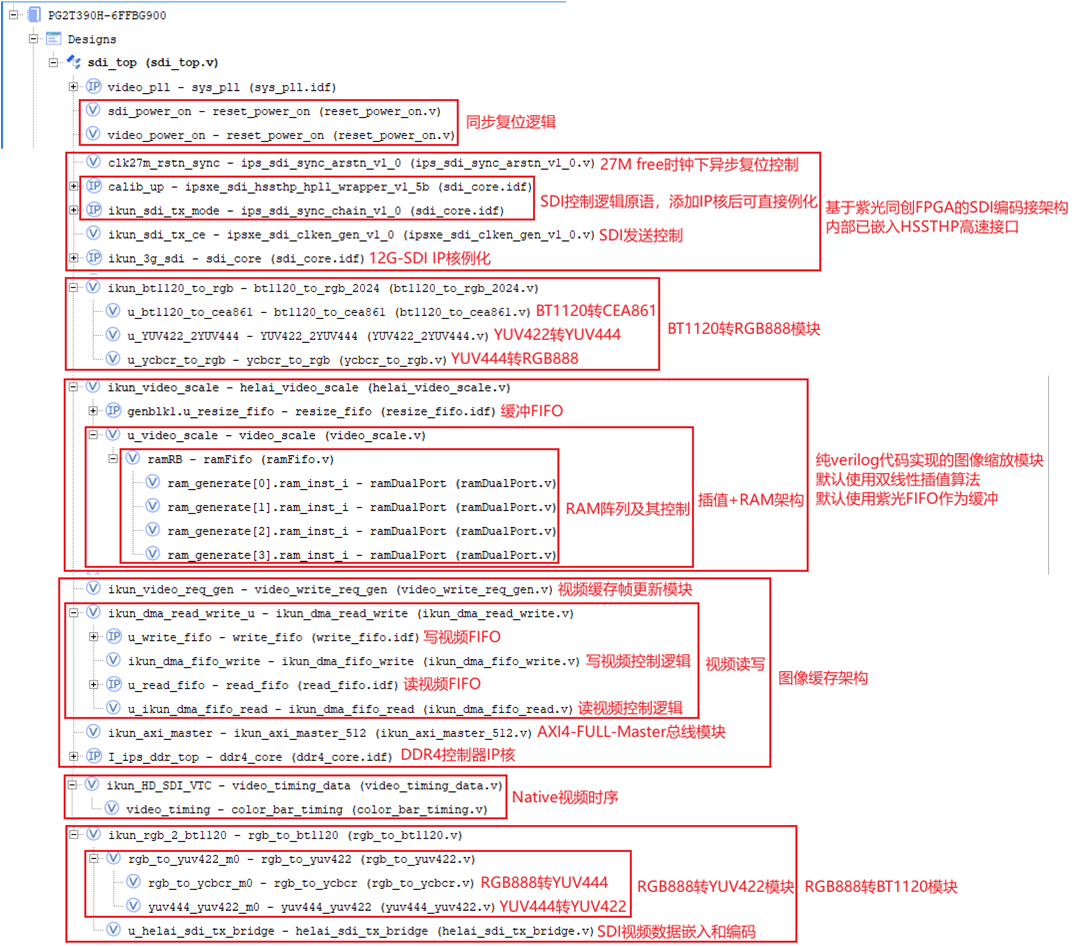

以工程源码2的3G-SDI解码缩放转HD-SDI输出为例,工程源码架构如下,其他工程与之类似:

4、工程源码1详解–>3G-SDI缩放转HDMI版本

开发板FPGA型号:紫光同创–PG2T390H-6FFBG900;;

开发环境:Pango Design Suite 2021.1

输入:3G-SDI相机或HDMI转SDI盒子,分辨率1920x1080@60Hz;

输出:HDMI,Silicom9134芯片编码,1920x1080黑色背景下叠加显示缩放后的图像;

SDI视频解串方案:紫光-HSSTHP高速接口解串;

SDI视频解码方案:紫光-12G-SDI解码;

图像缩放方案:纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720,其他分辨率缩放可自行修改;

图像缓存方案:纯Verilog图像缓存,4帧缓存,DDR4颗粒;

工程说明:全国产FPGA实现SDI解码缓存后转HDMI输出方案;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现SDI视频编解码的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

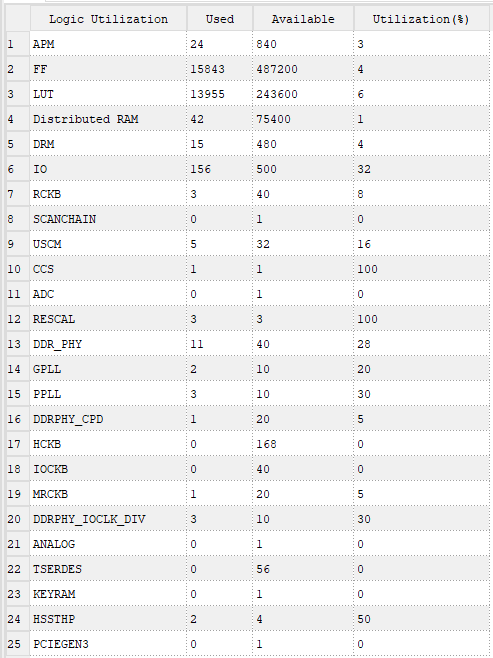

工程的资源消耗和功耗如下:

6、工程源码2详解–>3G-SDI缩放转HD-SDI版本

开发板FPGA型号:紫光同创–PG2T390H-6FFBG900;;

开发环境:Pango Design Suite 2021.1

输入:3G-SDI相机或HDMI转SDI盒子,分辨率1920x1080@60Hz;

输出:HD-SDI,分辨率1280x720@60Hz;

SDI视频解串方案:紫光-HSSTHP高速接口解串;

SDI视频解码方案:紫光-12G-SDI解码;

图像缩放方案:纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720,其他分辨率缩放可自行修改;

图像缓存方案:纯Verilog图像缓存,4帧缓存,DDR4颗粒;

工程说明:全国产FPGA实现SDI解码缓存后转SDI输出方案;

工程作用:此工程目的是让读者掌握紫光同创FPGA实现SDI视频编解码的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

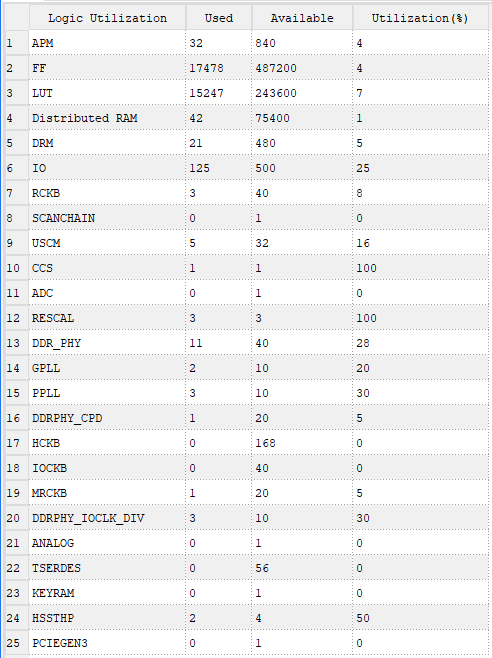

工程的资源消耗和功耗如下:

7、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头或HDMI转SDI盒子;

SDI转HDMI盒子;

HDMI显示器;

我的开发板了连接如下:

紫光同创FPGA SDI视频解码输出演示

紫光同创FPGA SDI视频解码输出演示如下:

紫光-SDI-缩放

9、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

国产紫光同创FPGA实现SDI视频编解码+图像缩放,基于HSSTHP高速接口,提供2套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目本博已有的 SDI 编解码方案本方案在Xilinx--Artix7系列FPGA上的应用本方案在Xilinx--Kintex系列FPGA上的应用本方案在Xilinx--Zynq系列FPGA上的应用本方案在Xilinx--U…...

25.4.22学习总结

如何通过好友列表对聊天框的切换 首先,我们知道,你的好友列表是用ListView组件实现的,那么,接下来,我们将开始讲解如何实现切换。 一、改造数据结构 如果你是跟着我的上一篇文章做的话,应该需要修改一些的…...

Agent智能体ReAct机制深度解读:推理与行动的完美闭环

一、从Chain-of-Thought到ReAct的范式演进 1.1 传统决策机制的局限 #mermaid-svg-Jf3ygvgHcGciJvX8 {font-family:"trebuchet ms",verdana,arial,sans-serif;font-size:16px;fill:#333;}#mermaid-svg-Jf3ygvgHcGciJvX8 .error-icon{fill:#552222;}#mermaid-svg-Jf3y…...

)

UnityDots学习(四)

官方案例HelloCube和Tank学习研究: HelloCube: 通用部分: 使用Authoring根据Inspector的勾选添加为Entity添加不同Component。然后每个System会根据实体添加的Component运行不同的System逻辑。 1. MainThread 简单构造System 先看System接口定义&am…...

Debian 12.10 root 登录失败,两步解决!

大家好,这里是 DBA学习之路,专注于提升数据库运维效率。 前言 今天看到 debian 正式发布 12.10,安装完成后发现无法登录 root 用户: 这里我一开始怀疑是 root 密码错了,所以改了一下 root 密码,忘记 root …...

2.3 预训练自己的模型)

AI大模型:(二)2.3 预训练自己的模型

目录 1.预训练原理 2.预训练范式 1.未标注数据 2.标注数据 3.有正确答案、也有错误答案 3.手撕transform模型 3.1.transform模型代码 3.2.训练数据集 3.3.预训练 3.4.推理 4.如何选择模型 5.如何确定模型需要哪种训练 大模型预训练(Large-scale Pre-training…...

)

【C语言】初阶算法相关习题(一)

个人主页 文章目录 ⭐一、数字在升序数组中出现的次数🏠二、整数转换🚀三、至少是其他数字两倍的最大数🏝️四、字符个数的统计🎄五、自除数🎡六、除自身以外数组的乘积🎉七、两个数组的交集 ⭐一、数字在…...

WITH 临时表 SQL优化

在 SQL 优化中, 临时表(CTE,Common Table Expression,公共表表达式) 是一种强大的工具,它通过定义一个临时的结果集(可以理解为 “虚拟表”),让复杂查询更易读、更高效&a…...

Go语言中 defer 使用场景及深度注意事项指南

文章精选推荐 1 JetBrains Ai assistant 编程工具让你的工作效率翻倍 2 Extra Icons:JetBrains IDE的图标增强神器 3 IDEA插件推荐-SequenceDiagram,自动生成时序图 4 BashSupport Pro 这个ides插件主要是用来干嘛的 ? 5 IDEA必装的插件&…...

第33周JavaSpringCloud微服务 面试题

一、项目面试 面试中介绍项目的方法 在面试过程中,若被问及相关项目,为提升通过几率,应着重介绍项目的功能点和架构升级内容。确保将项目的亮点讲透讲精彩,这对获取 offer 至关重要。 1. 项目架构 项目整体架构概述 项目整体…...

鸿蒙开发:Swiper轮播图

鸿蒙Swiper组件详解 一、Swiper组件概述 Swiper是鸿蒙(HarmonyOS)系统中提供的一个滑动容器组件,它允许用户通过手指滑动来切换子组件(通常是页面或图片),实现轮播图、引导页、图片浏览器等常见UI效果。 说明 该组件从API versi…...

Go语言之sync包 WaitGroup的使用和底层实现

在 Go 语言里,sync 包中的 WaitGroup 是一个实用工具,用于等待一组 goroutine 完成任务。其核心原理是通过内部维护一个计数器,该计数器初始值为 0,每启动一个新的 goroutine 就将计数器加 1,每个 goroutine 完成任务后…...

7N60-ASEMI无人机专用功率器件7N60

编辑:LL 7N60-ASEMI无人机专用功率器件7N60 型号:7N60 品牌:ASEMI 封装:TO-220F 最大漏源电流:7A 漏源击穿电压:600V 批号:最新 RDS(ON)Max:1.20Ω …...

SystemV-消息队列与责任链模式

一、SystemV 消息队列 1. 消息队列API Ftok 函数定义: key_t ftok(const char *pathname, int proj_id);函数作用: 获取唯一的key值标识符,用于标识系统V消息队列。参数解释: pathname:有效的文件路径(需…...

Ubuntu与Linux的关系

Linux 是一个 操作系统内核。它是一个类 Unix 系统,免费、开源,许多不同的操作系统(叫“发行版”)都是基于 Linux 内核构建的。 Ubuntu 是一个 基于 Linux 内核的操作系统发行版。它是目前最流行、最易用的 Linux 发行版之一&…...

同时支持windows和Linux的NFC读写器web插件

一个网站集成了NFC读写器的功能,如何才能跨系统运行呢,既要在windows系统下正常运行,也需要在银河麒麟,统信UOS等信创系统下运行。 友我科技NFC读写器web插件很好的解决了这个问题,在客户端不仅支持windows系统&#x…...

突破AI检测边界:对抗技术与学术伦理的终极博弈

随着GPT-4、Claude等大模型的文本生成能力突破人类写作水平,AI检测工具与对抗技术的博弈已进入白热化阶段。本文深入解析基于对抗训练的文本风格混淆网络如何突破GPTZero最新防御体系,探讨OpenAI多模态内容溯源系统引发的技术升级,并针对学术…...

pg数据库删除自建表空间

1. tbs_sjzx已经创建(略) pg数据库删除自己创建表空间;--查看表空间相关表 SELECT * FROM pg_tablespace; SELECT relname FROM pg_class WHERE reltablespace (SELECT oid FROM pg_tablespace WHERE spcname tbs_sjzx); SELECT * FROM pg_tables WHE…...

C++ 学习指南

new 关键字 #include <iostream> using namespace std;int* func() {// 在堆区创建int* p new int(10); return p; }void test01(void) {int *p func();cout << *p << endl;cout << *p << endl;cout << *p << endl;delete p;// 这…...

Scribe: 一个非常方便的操作文档编写工具

在日常生活中,当我们需要指导别人使用一个软件/web应用时,我们常常需要按流程对工具进行操作,走一遍主要功能,然后针对每一步进行截图,并附上操作说明。往往这样一套流程走下来,就会花费很长的时间。那么有…...

数据结构与算法-顺序表应用

一.通讯录的创建 首先我们要理解的是通讯录本身就是以顺序表为底层的 只不过顺序表中的数组,这里我们是用结构体来替代,用来存储用户的信息 由于是通讯录的本质就是顺序表,所以顺序表的任何方法它都能套用 Contact.h: #pragma once #def…...

:助力数据分析)

DeepSeek系列(5):助力数据分析

数据解读与可视化建议 在数据驱动的商业环境中,有效解读数据并将其转化为直观可视化结果至关重要。DeepSeek作为强大的AI助手,可以帮助您从海量数据中提取洞见并提供专业的可视化建议。 DeepSeek在数据解读中的优势 DeepSeek可以通过以下方式帮助您更高效地解读数据: 上下…...

虚幻基础:动画k帧

文章目录 动画k帧:调整骨骼的变换达到自己想要的效果步骤打开动画原始文件选中骨骼调整到目标变换添加关键帧时间:自动添加到停留的那一帧数值:自动填写为调整后的数值 注释数值与骨骼细节面板上的数值并不对应,但是同样的效果为什…...

使用 LlamaIndex Workflows 与 Elasticsearch

作者:来自 Elastic Jeffrey Rengifo 在本文中,你将学习如何利用 LlamaIndex Workflows 与 Elasticsearch 快速构建一个使用 LLM 的自过滤搜索应用程序。 LlamaIndex Workflows 提出了一种不同的方式来处理将任务拆分给不同 agent 的问题,它引…...

相对论大师-记录型正负性质BFS/图论-链表/数据结构

看到这一题我的第一个思路就是双向bfs 起点是a,终点还是a,但是flag是相反的(“越”的方向) tip1.可以用字典vis来存储flag 刚开始初始化时vissta,visend一个对应0、1 要求两个队列相…...

代理设计模式:从底层原理到源代码的详细解释

代理设计模式(Proxy Pattern)是一种结构型设计模式,它通过创建一个代理对象来控制对目标对象的访问。代理对象充当客户端和目标对象之间的中介,允许在不修改目标对象的情况下添加额外的功能(如权限控制、日志记录、延迟…...

EasyRTC音视频实时通话:打造高清低延迟的远程会议新生态

一、项目背景 随着数字化办公的普及,远程会议成为企业、教育机构、政府部门等组织跨地域协作沟通的重要方式。传统远程会议系统在音视频质量、低延迟传输、多平台兼容性等方面存在不足,难以满足用户对高清、流畅、稳定会议体验的需求。EasyRTC作为一款…...

:图表选择困难症?常用可视化类型详解与应用场景指南)

零基础上手Python数据分析 (21):图表选择困难症?常用可视化类型详解与应用场景指南

写在前面 —— 告别盲目绘图,理解图表语言,为你的数据找到最佳“代言人” 在前面几篇博客中,我们已经学习了使用 Matplotlib 和 Seaborn 这两大 Python 可视化利器来绘制各种图表。我们掌握了创建折线图、柱状图、散点图、箱线图等常用图表的技术。然而,仅仅知道 如何 绘…...

HarmonyOS Next 编译之如何使用多目标产物不同包名应用

引言 在日常的开发中涉及到多签名和多产物构建输出时手动切换签名文件和包名在开发中是容易出错且费时的一个操作,鸿蒙提供了自定义hvigor插件和多目标产物构建,那我们可以通过hvigor插件来动态修改不同项目配置所需要的代码,保证一套代码在…...

白皮书阅读笔记)

Oracle Database Resident Connection Pooling (DRCP) 白皮书阅读笔记

本文为“Extreme Oracle Database Connection Scalability with Database Resident Connection Pooling (DRCP)”的中文翻译加阅读笔记。觉得是重点的就用粗体表示了。 白皮书版本为March 2025, Version 3.3,副标题为:Optimizing Oracle Database resou…...

Sharding-JDBC 系列专题 - 第七篇:Spring Boot 集成与 Sharding-Proxy 简介

Sharding-JDBC 系列专题 - 第七篇:Spring Boot 集成与 Sharding-Proxy 简介 本系列专题旨在帮助开发者全面掌握 Sharding-JDBC,一个轻量级的分布式数据库中间件。本篇作为系列的第七篇文章,将重点探讨 Sharding-JDBC 与 Spring Boot 的集成,以及 Sharding-Proxy 的基本概念…...

day30 学习笔记

文章目录 前言一、凸包特征检测1.穷举法2.QuickHull法 二、图像轮廓特征查找1.外接矩形2.最小外接矩形3.最小外接圆 前言 通过今天的学习,我掌握了OpenCV中有关凸包特征检测,图像轮廓特征查找的相关原理和操作 一、凸包特征检测 通俗的讲,凸…...

变更管理 Change Management

以下是关于项目管理中 变更管理 的深度解析,结合高项(如软考高级信息系统项目管理师)教材内容,系统阐述变更管理的理论框架、流程方法及实战应用: 一、变更管理的基本概念 1. 定义 变更管理是对项目范围、进度、成本、质量等基准的修改进行系统性控制的过程,旨在确保变…...

PaddlePaddle线性回归详解:从模型定义到加载,掌握深度学习基础

目录 前言一、paddlepaddle框架的线性回归1.1 paddlepaddle模型的定义方式1.1.1 使用序列的方式 nn.Sequential 组网1.1.2 使用类的方式 class nn.Layer组网1.2 数据加载 1.3 paddlepaddle模型的保存1.3.1 基础API保存1.3.2 高级API模型的保存1.3.2.1 训练fit进行保存1.3.2.2 …...

几种Word转换PDF的常用方法

使用 Word 内置功能 步骤:打开需要转换的 Word 文档,点击左上角的 “文件” 菜单,选择 “另存为”,选择保存位置,在 “保存类型” 下拉菜单中选择 “PDF”,点击 “保存” 按钮即可。适用场景:适…...

【美化vim】

美化vim 涉及文件一个例子 涉及文件 ~/.vimrc修改这个文件即可 一个例子 let mapleader ,set number " 显示行号"set relativenumber " 显示相对行号set incsearch " 实时开启搜索高亮set hlsearch " 搜索结果高亮set autoinden…...

【git】subtree拆分大的git库到多个独立git库

【git】subtree拆分大的git库到多个独立git库 一、拆分一个子目录为独立仓库 # 这就是那个大仓库 big-project git clone gitgithub.com:tom/big-project.git cd big-project# 把所有 eiyo 目录下的相关提交整理为一个新的分支 eiyo_code git subtree split -P eiyo -b eiyo_…...

Elasticsearch 使用reindex进行数据同步或索引重构

1、批量复制优化 POST _reindex {"source": {"index": "source","size": 5000},"dest": {"index": "dest"} }2、提高scroll的并行度优化 POST _reindex?slices5&refresh {"source": {…...

JDBC对数据的增删改查操作:从Statement到PrepareStatement

目录 一 . Statement简介 二. 通过Statement添加数据 1. 创建表 2. 通过Statement添加数据 a. 获取连接 b. 获取Statement对象 c. 定义SQL语句 d. 执行SQL语句 e. 关闭资源 3. 通过Statement修改数据 4. 通过Statement删除数据 三. PreparedStatement的使用(重点) …...

智体OS上线智体管家:对话式智体应用商店访问

DTNS.OS 更新公告 - 智体管家功能发布 🌟 2024年4月22日重要更新:智体管家正式上线 智体管家是智体OS推出的全新功能,旨在让用户通过自然对话轻松发现和使用智体节点上的所有智体应用,相当于为智体网络打造了一个智能化的应用商…...

vscode flutter 插件, vscode运行安卓项目,.gradle 路径配置

Flutter Flutter Widget Snippets Awesome Flutter Snippets i dart-import Dart Data Class Generator Json to Dart Model Dart Getters And Setter GetX Snippets GetX Generator GetX Generator for Flutter flutter-img-syncvscode运行安卓项目,.gradle 路径配…...

数据ETL)

dolphinscheduler实现(oracle-hdfs-doris)数据ETL

dolphinscheduler执行 完整脚本(自行替换相关变量)配置文件conf配置文件解析脚本转base64脚本 完整脚本(自行替换相关变量) user_olsh conf/getInfo.sh Oracle user conf/databases.conf password_olsh conf/getInfo.sh Oracle password conf/databases.conf dblink_olsh conf…...

ViewBS 的工作流程

ViewBS ViewBS 的工作流程 ViewBS 提供多个顶级命令,用于确定所需和最优参数。这些命令可分为两部分:甲基化报告和功能区域的数据可视化。 在甲基化报告部分中,提供多个顶级命令,可以生成关于读取覆盖度、甲基化水平分布、全局甲基化水平等报告。 在功能区域可视化部分…...

)

qt调用deepseek的API开发(附带源码)

今天讲的是使用qt做一个界面(负责接受deepseek返回的数据和客户发送数据的端口)会用流的方式接受数据提高用户体验 测试效果源码流程配置deepseek调用思路deepseek与qt联合开发界面思路 上一篇文章用的不是流开发,会让客户等待很久࿰…...

java中值传递的含义

Java 中的值传递(Pass by Value)详解 在 Java 中,所有参数的传递都是值传递(Pass by Value),但根据传递的数据类型不同(基本类型 vs 引用类型),表现行为会有所不同。 1.…...

【自然语言处理与大模型】如何知道自己部署的模型的最大并行访问数呢?

当你自己在服务器上部署好一个模型后,使用场景会有两种。第一种就是你自己去玩,结合自有的数据做RAG等等,这种情况下一般是不会考虑并发的问题。第二种是将部署好的服务给到别人来使用,这时候就必须知道我的服务到底支持多大的访问…...

单词助手网站)

基于PHP+MySQL实现(Web)单词助手网站

WordHelper 这是一个学习 PHP 的时候依照课程设计的要求,做的一个简单的单词助手。 系统通过 CDN 引入 Vue.js 和 ElementUI,并用 PHP 搭建了一个十分十分简易的后台。 一、设计要求 1、词汇录入与编辑。提供接口让用户录入英文单词、词义、发音、词…...

Java面试实战:谢飞机的求职记 - Spring Boot、Redis与微服务技术问答解析

场景描述 谢飞机,一位自称为“Java全栈大师”的程序员,参加了某互联网大厂的Java开发岗位面试。面试官严肃而专业,针对Spring Boot、Redis缓存以及微服务架构等核心技术展开提问。以下是谢飞机在面试中的表现。 第一轮提问(基础篇…...

【数字图像处理】立体视觉信息提取

双目立体视觉原理 设一个为参考平面,一个为目标平面。增加了一个摄像头后,P与Q在目标面T上有分别的成像点 双目立体视觉:从两个不同的位置观察同一物体,用三角测量原理计算摄像机到该物体的距离的 方法 原理:三角测量…...

解析芯片低功耗设计的底层逻辑与实现方法

芯片低功耗设计的必要性可以从实际需求和技术优化两方面来探讨: 从需求角度看,工艺进步和应用场景共同驱动低功耗设计。 随着CMOS制程持续微缩,晶体管密度和时钟频率提升导致静态功耗显著增加,漏电流问题在先进工艺中尤为明显。…...