【FPGA】——DDS信号发生器设计

目录

一 、IP核的使用

(1)RAM IP核

(2)FIFO IP核

二、DDS信号发生器设计

(1)代码

(2)仿真波形

一 、IP核的使用

IP核:ASIC或FPGA中预先设计好具有某种功能的电路模块,参数可修改,目的在于提高开发效率。

QuartusII软件下IP核调用方式:Mega Wizard插件管理器(常用)、SOPC构造器、DSP构造器、Qsys设计系统例化。

(1)RAM IP核

RAM的英文全称是Random Access Memory,即随机存取存储器,它可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据。其读写速度是由时钟频率决定的。RAM主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。其特点适合双向交换数据。

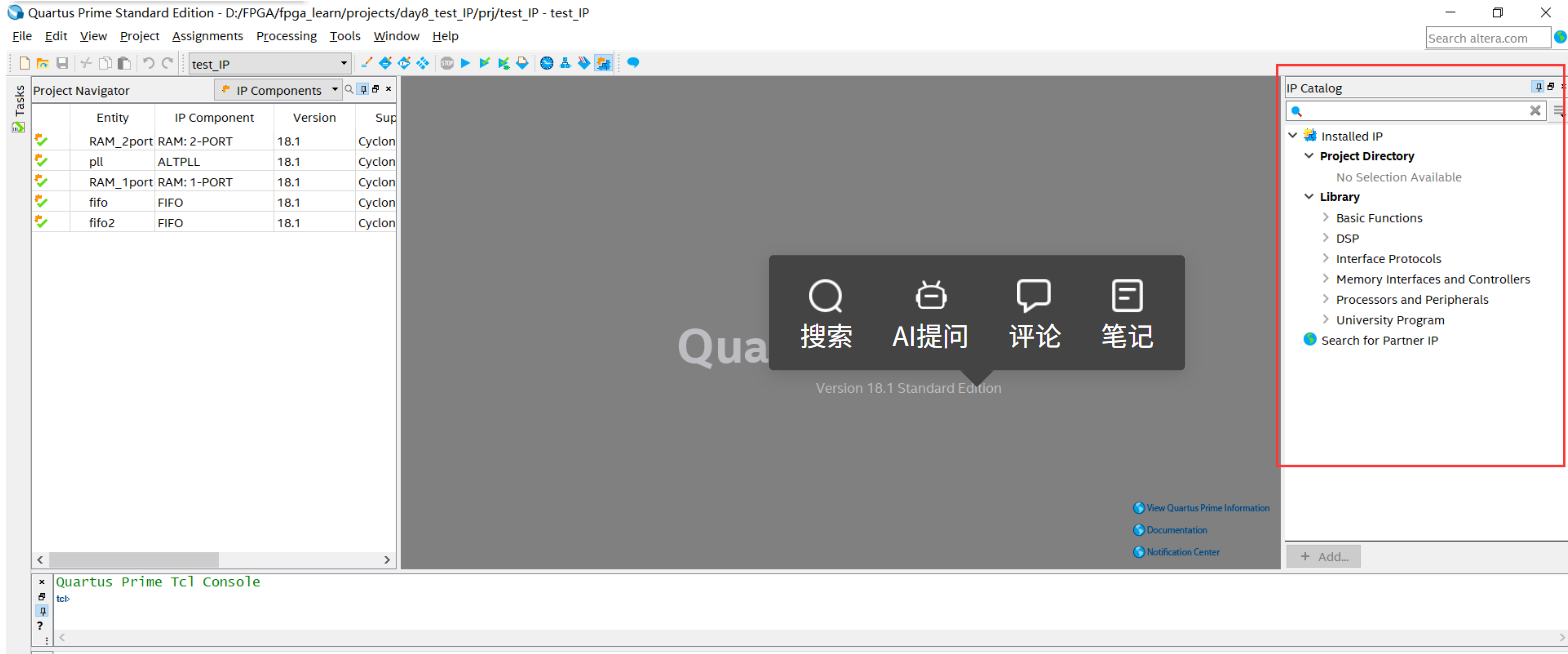

打开Quartus软件,新建一个项目后,在界面的最右侧,可以看见一个IP Catalog的栏目,在这里有很多的IP核可以供我们选择使用

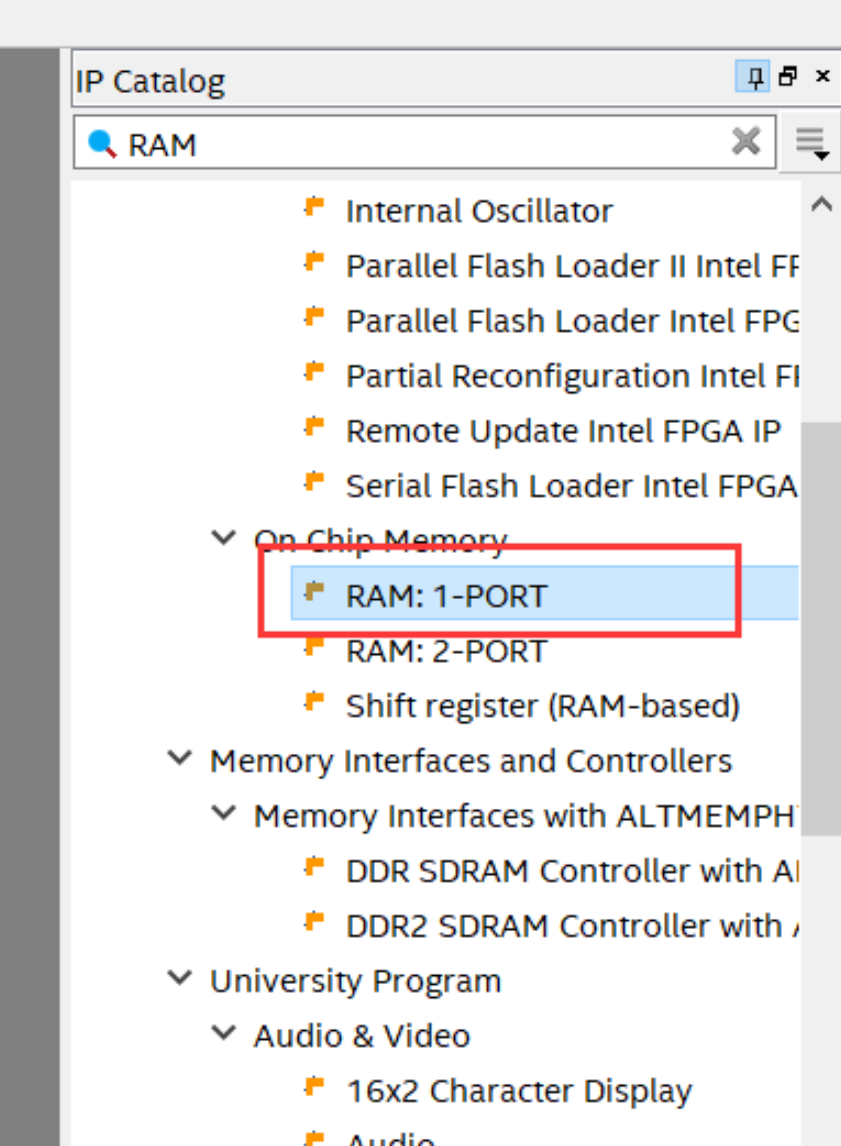

在IP Catalog中搜索RAM

双击选择RAM:1-PORT,保存在ip文件夹下,命名为RAM_1port.v

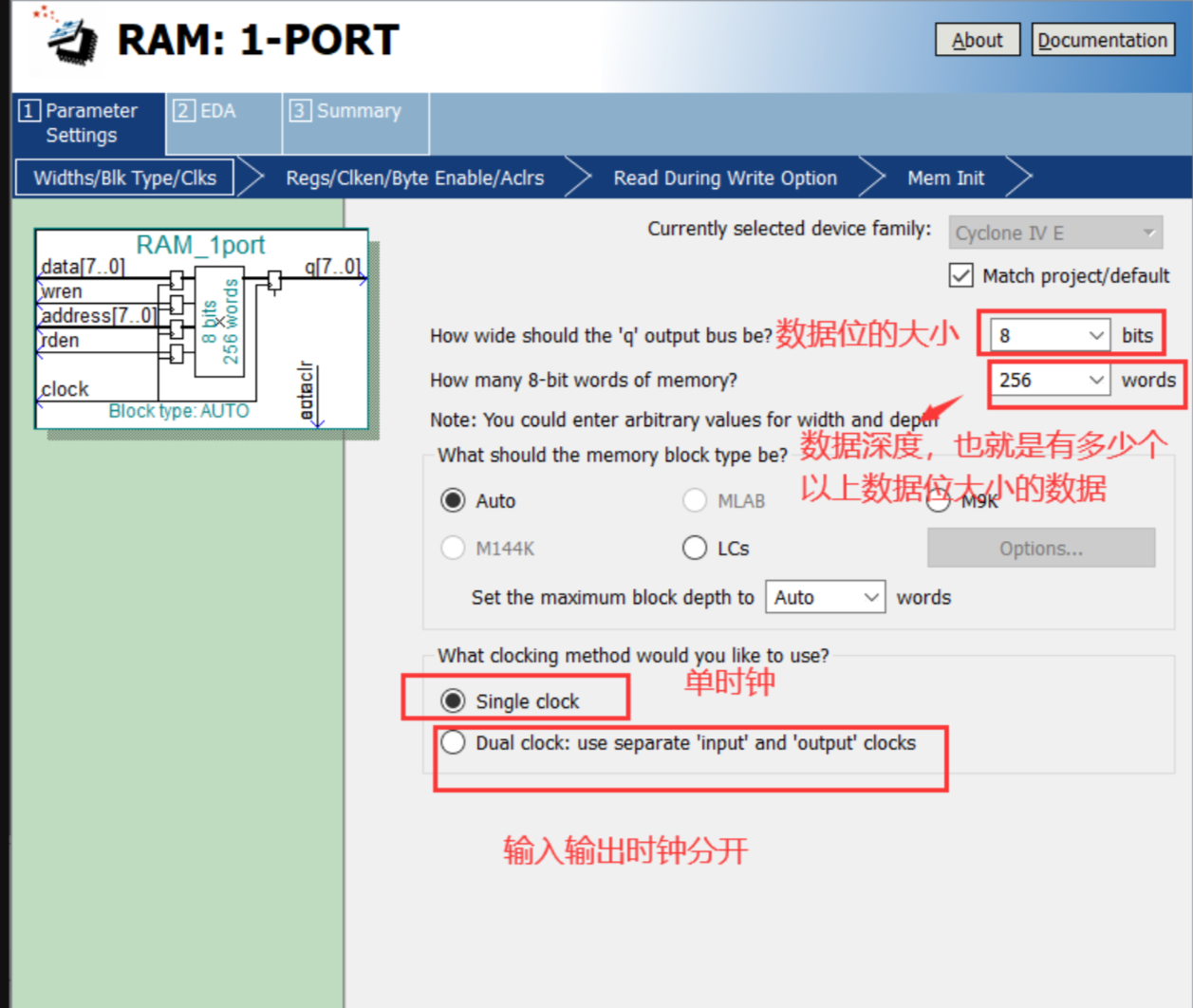

选择数据位大小,以及数据深度

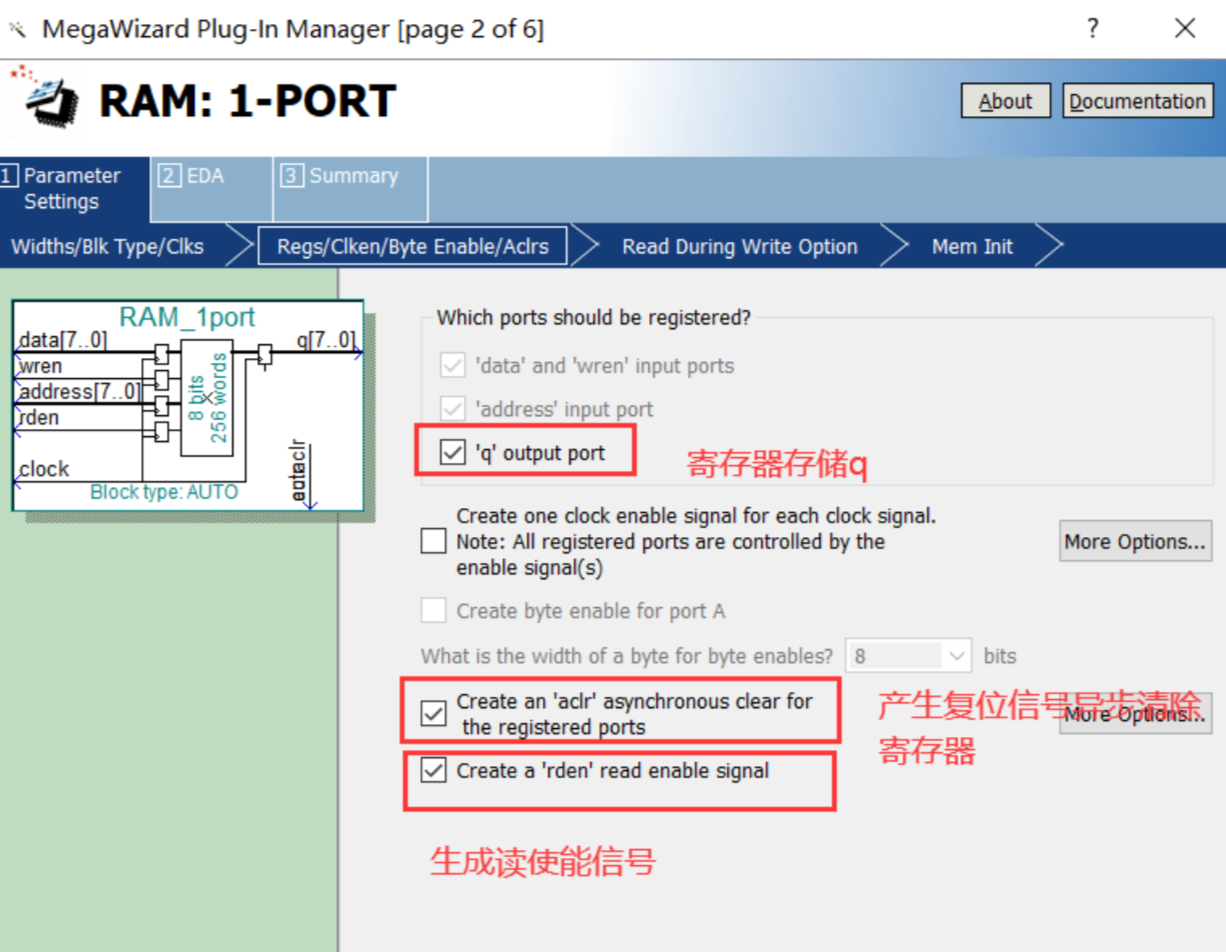

之后选择NEXT

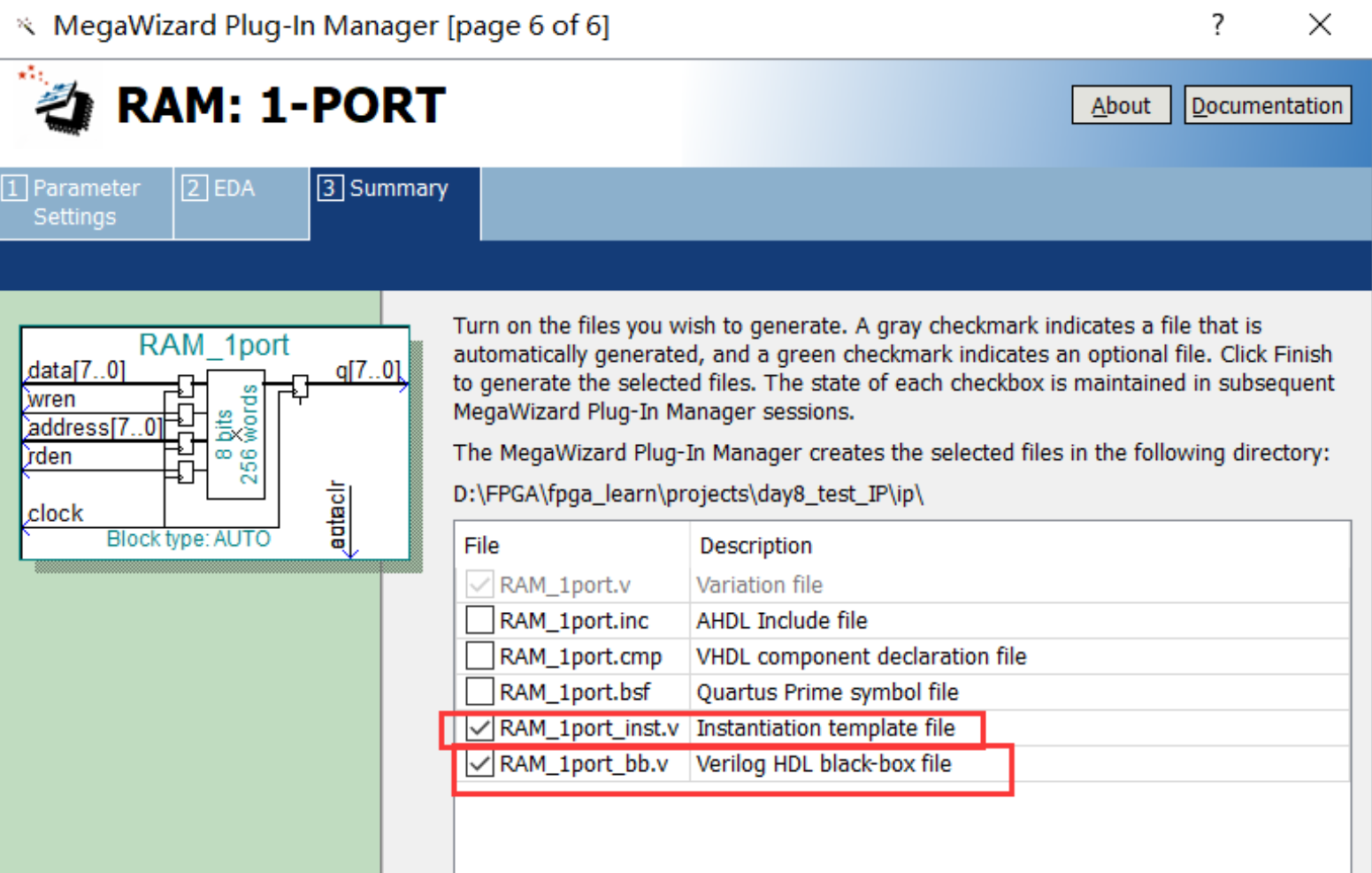

勾选RAM_1port_inst.v和RAM_1port_bb.v文件

(2)FIFO IP核

FPGA使用的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存或者高速异步数据的交互,也即所谓的跨时钟域信号传递。

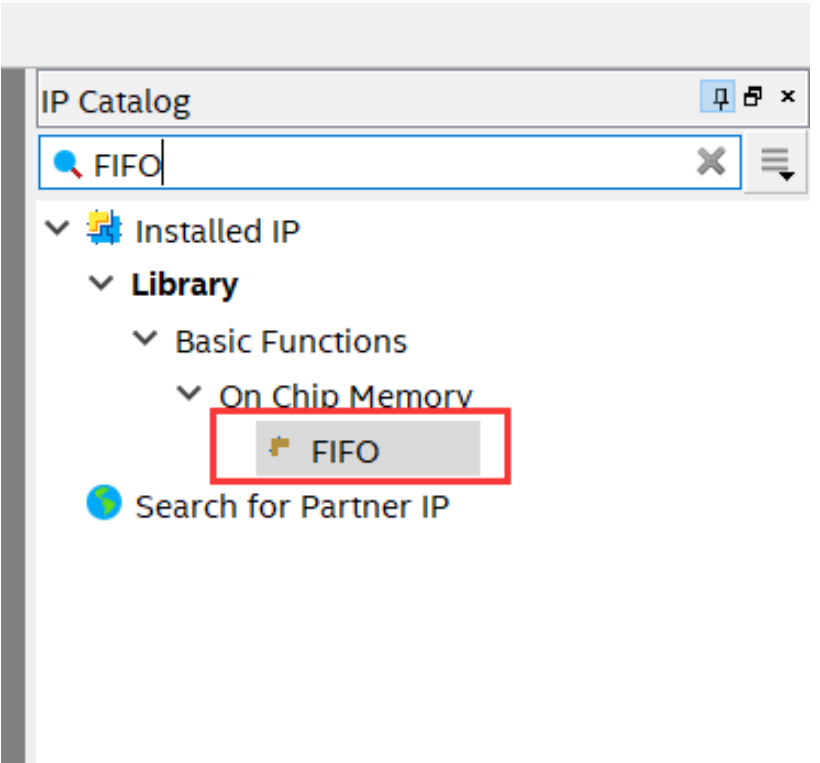

FIFO的IP核调用(读写共用时钟)

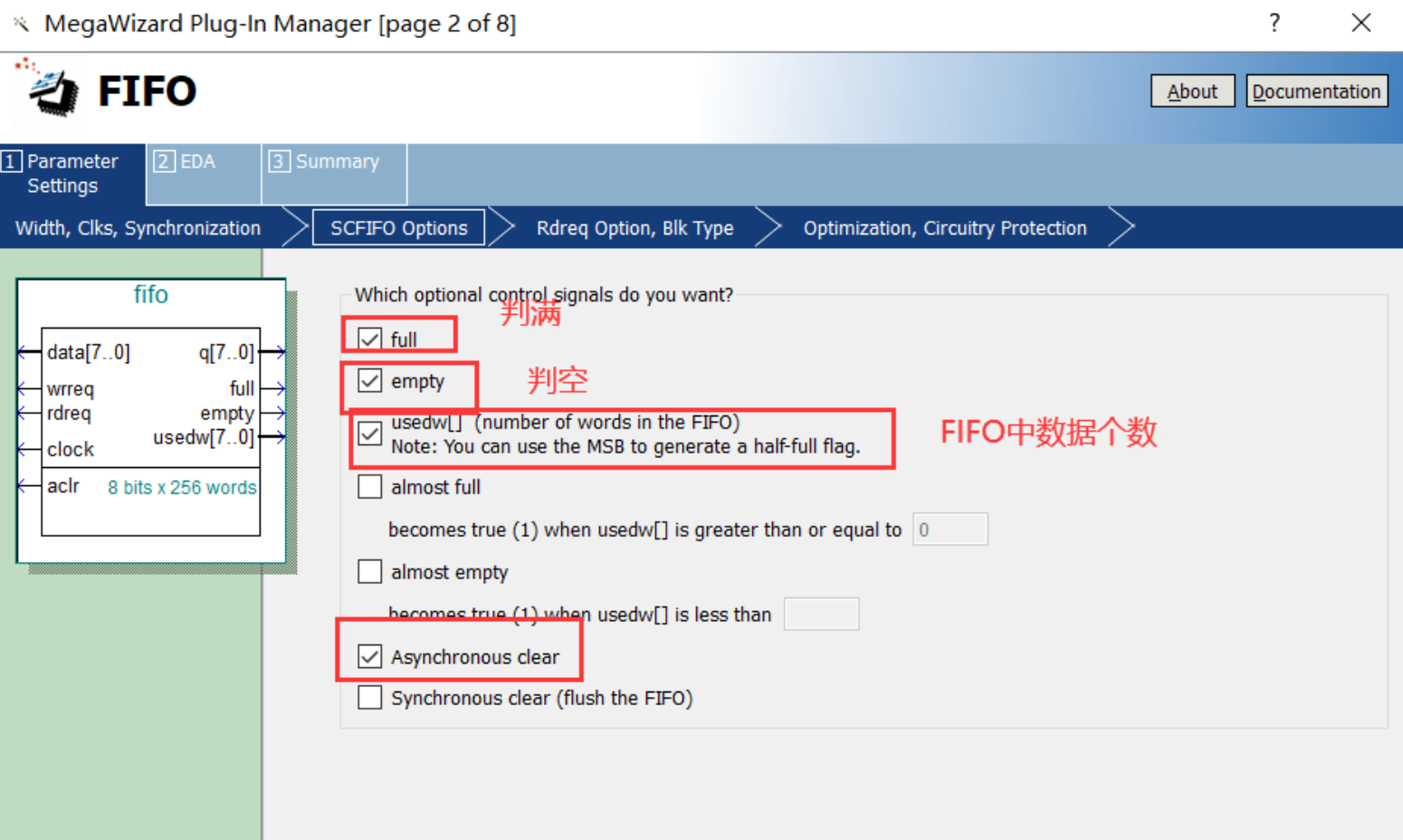

选择读写使用同一个时钟,勾选下面的信号

之后选择Next

二、DDS信号发生器设计

(1)代码

DDS技术的基本原理是利用相位累加器和波形查找表来合成所需频率的波形:

-

相位累加器:在每个时钟周期累加频率控制字(Frequency Control Word, FCW)

-

相位-幅度转换:通过查找表将相位信息转换为对应的幅度值

-

数模转换:将数字幅度值转换为模拟信号

输出频率计算公式:fout = (FCW × fclk) / 2^N,其中N为相位累加器位数。

顶层模块DDS_top .v

module DDS_top (input CLOCK_50,input [1:0] KEY, // KEY[0]-复位,KEY[1]-波形选择input [3:0] SW, // SW[0]-增频,SW[1]-减频output [7:0] LEDG, // 显示当前状态output [7:0] DAC_DATA, // 波形数据输出output DAC_CLK, // DAC时钟output DAC_CS,output DAC_MODE,// 用于SignalTap II监测的信号output [9:0] DEBUG_PHASE,output [7:0] DEBUG_WAVE

);wire reset_n = KEY[0];wire wave_select = KEY[1];wire [31:0] freq_word;wire [15:0] freq_display;// 频率控制模块frequency_control freq_ctrl (.clk_50MHz(CLOCK_50),.reset_n(reset_n),.key_in(SW[1:0]),.freq_word(freq_word),.freq_display(freq_display));// DDS核心模块enhanced_dds dds_core (.clk_50MHz(CLOCK_50),.reset_n(reset_n),.wave_select(wave_select),.freq_word(freq_word),.wave_out(DAC_DATA),.phase_out(DEBUG_PHASE));// DAC控制信号assign DAC_CLK = CLOCK_50;assign DAC_CS = 1'b0;assign DAC_MODE = 1'b1;// 调试信号连接assign DEBUG_WAVE = DAC_DATA;// LED显示assign LEDG = {wave_select, 3'b0, freq_display[15:12]};endmoduledebounce .v

module debounce (input clk,input button_in,output reg button_out

);reg [19:0] counter;reg button_state;always @(posedge clk) beginif (button_in != button_state) beginbutton_state <= button_in;counter <= 20'd0;endelse if (counter < 20'd1_000_000) begincounter <= counter + 1'b1;endelse beginbutton_out <= button_state;endendendmoduleenhanced_dds.v

module enhanced_dds (input clk_50MHz, // 50MHz系统时钟input reset_n, // 低电平复位input wave_select, // 0-正弦波,1-方波input [31:0] freq_word, // 频率控制字output reg [7:0] wave_out, // 波形输出output reg [9:0] phase_out // 相位输出(用于SignalTap)

);// 32位相位累加器reg [31:0] phase_accum;// 正弦波ROM(10位地址,8位数据)wire [9:0] rom_addr = phase_accum[31:22]; // 取高10位wire [7:0] sine_data;// 方波信号定义(修正位宽)wire [7:0] square_data = phase_accum[31] ? 8'hFF : 8'h00;// 相位累加always @(posedge clk_50MHz or negedge reset_n) beginif (!reset_n)phase_accum <= 32'd0;elsephase_accum <= phase_accum + freq_word;end// 正弦波ROM实例化sine_rom_1024 sine_rom (.address(rom_addr),.clock(clk_50MHz),.q(sine_data));// 波形选择always @(*) begincase (wave_select)1'b0: wave_out = sine_data;1'b1: wave_out = square_data;default: wave_out = sine_data;endcaseend// 相位输出用于SignalTap监测always @(posedge clk_50MHz) beginphase_out <= rom_addr;endendmodulefrequency_control.v

module frequency_control (input clk_50MHz,input reset_n,input [1:0] key_in, // 按键输入[0]-增,[1]-减output reg [31:0] freq_word,output reg [15:0] freq_display // 频率显示值(Hz)

);// 频率控制参数parameter MIN_FREQ = 10; // 10Hzparameter MAX_FREQ = 5_000_000; // 5MHzparameter STEP_1KHZ = 85899; // 1kHz对应的FCW// 按键消抖实例化wire [1:0] key_pressed;debounce deb0(.clk(clk_50MHz), .button_in(key_in[0]), .button_out(key_pressed[0]));debounce deb1(.clk(clk_50MHz), .button_in(key_in[1]), .button_out(key_pressed[1]));// 频率控制always @(posedge clk_50MHz or negedge reset_n) beginif (!reset_n) beginfreq_word <= 32'd85899; // 默认1kHzfreq_display <= 16'd1000;endelse beginif (key_pressed[0] && freq_display < MAX_FREQ) beginfreq_word <= freq_word + STEP_1KHZ;freq_display <= freq_display + 16'd1000;endelse if (key_pressed[1] && freq_display > MIN_FREQ) beginfreq_word <= freq_word - STEP_1KHZ;freq_display <= freq_display - 16'd1000;endendendendmodulesine_rom_1024 .v

module sine_rom_1024 (input [9:0] address,input clock,output reg [7:0] q

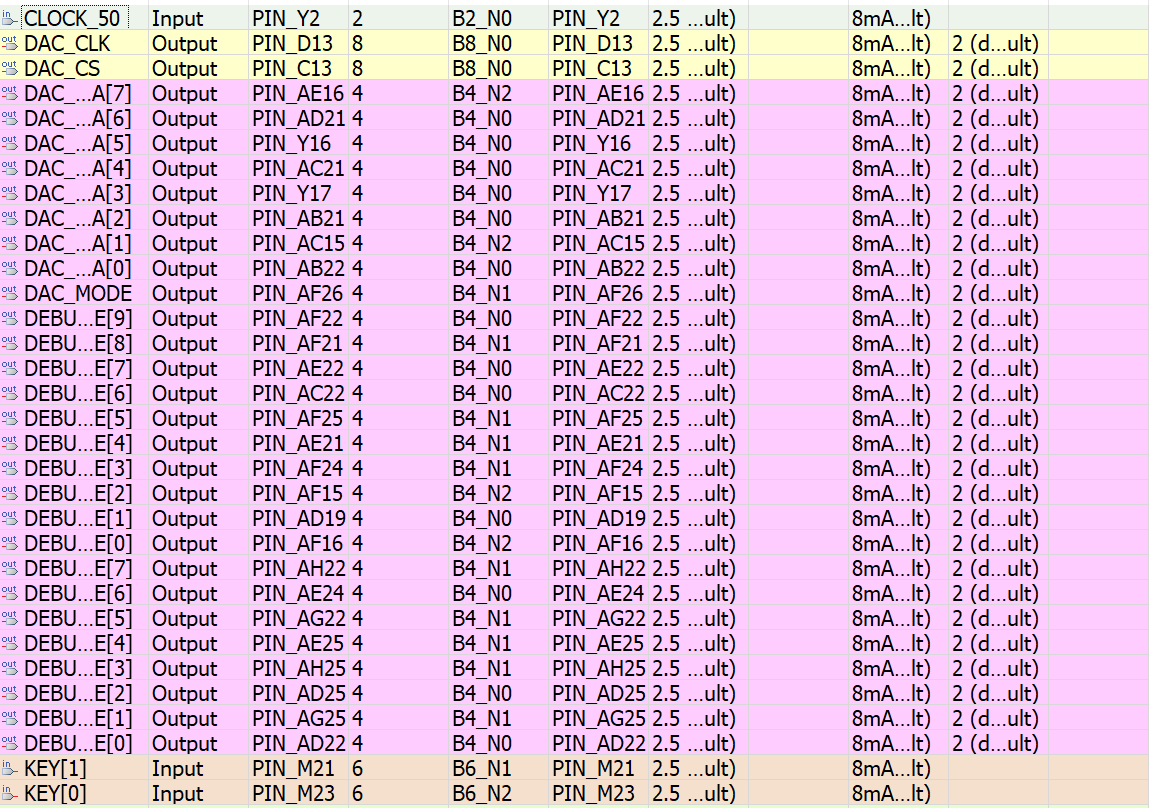

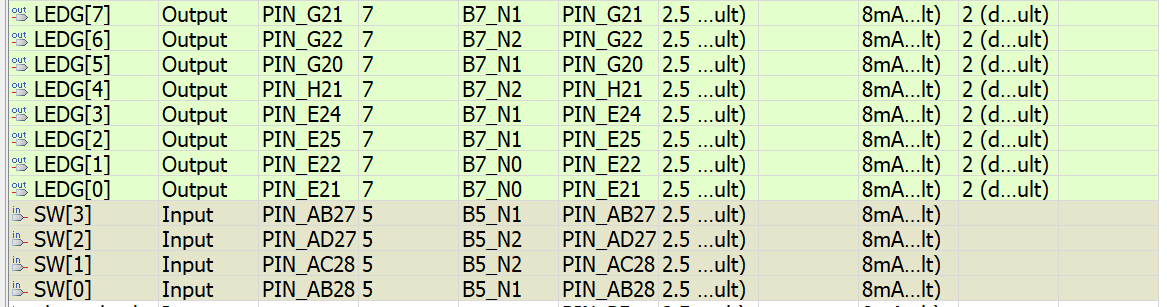

);reg [7:0] rom [0:1023];initial begin// 预计算的1024点正弦波表(8位有符号)rom[0] = 8'd128; rom[1] = 8'd131; rom[2] = 8'd134; rom[3] = 8'd137;rom[4] = 8'd140; rom[5] = 8'd143; rom[6] = 8'd146; rom[7] = 8'd149;rom[8] = 8'd152; rom[9] = 8'd155; rom[10] = 8'd158; rom[11] = 8'd162;rom[12] = 8'd165; rom[13] = 8'd168; rom[14] = 8'd171; rom[15] = 8'd174;// ... 填写完整的1024个点 ...rom[1020] = 8'd114; rom[1021] = 8'd117; rom[1022] = 8'd120; rom[1023] = 8'd123;endalways @(posedge clock) beginq <= rom[address];endendmodule引脚配置

(2)仿真波形

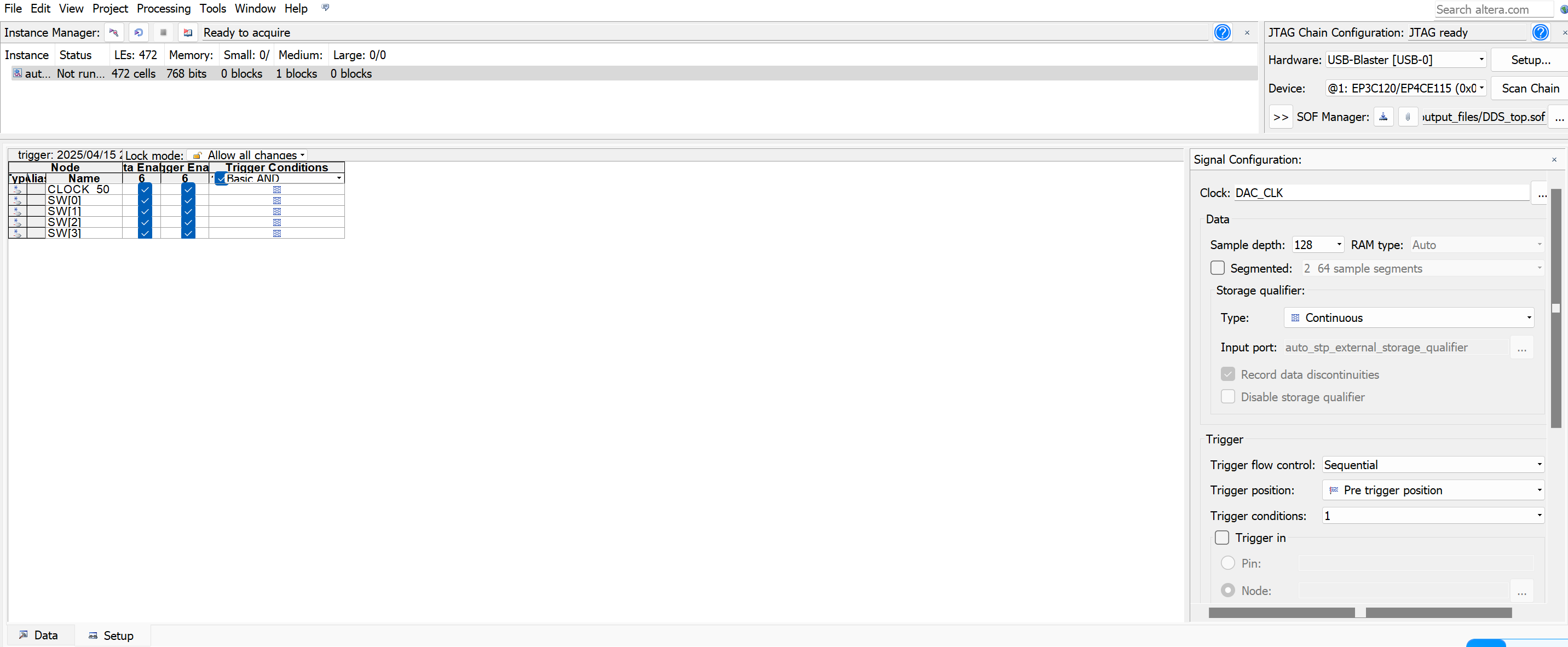

Tools-》SignalTap ll Logic Analyzer,查看波形

![]()

总结

IP核的运用是一个新接触的内容,第一次使用时需要借鉴不同资料,明白其道理。

相关文章:

【FPGA】——DDS信号发生器设计

目录 一 、IP核的使用 (1)RAM IP核 (2)FIFO IP核 二、DDS信号发生器设计 (1)代码 (2)仿真波形 一 、IP核的使用 IP核:ASIC或FPGA中预先设计好具有某种功能的电路模块,参数可修改…...

mysql按条件三表并联查询

下面为你呈现一个 MySQL 按条件三表并联查询的示例。假定有三个表:students、courses 和 enrollments,它们的结构和关联如下: students 表:包含学生的基本信息,有 student_id 和 student_name 等字段。courses 表&…...

centos 7 docker创建的postgres数据库状态检查

一 、打开finalshell 连接主机 二、检查docker状态,以下信息表示数据库准备好连接了 注意:当finalshell可以访问主机,但没有准备信息时,重启centos系统试试 docker logs postgres 三、如果是传统安装 基于 systemd 的系统(如 CentOS 7 及以上、Ubuntu 16.04 及以…...

基于EasyX库开发的球球大作战游戏

目录 球球大作战 一、开发环境 二、流程图预览 三、代码逻辑 1、初始化时间 2、设置开始界面大小 3、设置开始界面 4、让玩家选择速度 5、设置玩家小球、人机小球、食物的属性 6、一次性把图绘制到界面里 7、进入死循环 8、移动玩家小球 9、移动人机 10、食物刷新…...

ES和MySQL概念对比

基本概念 ES和MySQL都属于数据库,不过各有各的特性,大致使用方法与MySQL类似并无区别。 MySQL:擅长事务持有ACID的特性,确保数据的一致性和安全。 ES:持有倒排索引,适合海量数据搜索和分析。 ES和MySQL如何…...

Kotlin 与 Jetpack Compose 参数设计完全指南

作为 Kotlin 和 Jetpack Compose 开发者,合理的参数设计能显著提升代码的可读性和易用性。本文将系统整理各类参数规则,帮助您编写更优雅的 API。 一、基础参数规则 1. 方法参数 // 基础定义 fun 方法名(必需参数: 类型, 可选参数: 类型 默认值): 返…...

dea如何使用git

在 IntelliJ IDEA 中使用 Git 的详细步骤如下,分为配置、基础操作和高级功能,适合新手快速上手: 一、配置 Git 安装 Git 下载并安装 Git,安装时勾选“Add to PATH”。验证安装:终端输入 git --version 显示版本…...

,git介绍(对待数据的方式,本地执行,保证完整性,只添加数据,git文件/项目的三种状态,基本的工作流程))

git -- 版本控制介绍(分布式系统),git介绍(对待数据的方式,本地执行,保证完整性,只添加数据,git文件/项目的三种状态,基本的工作流程)

目录 版本控制 介绍 分布式版本控制系统 git 介绍 与多个远程仓库协作 对待数据的方式 本地执行操作 保证完整性 只添加数据 三种状态 工作区 暂存区 Git 目录 基本的git工作流程 版本控制 介绍 一种记录一个或多个文件内容变化的系统,它可以让你在未来…...

嵌入式软件OTA升级,有哪几种Flash划分方式?

第一次接触嵌入式软件OTA升级的时候,我整个人也是懵的。Flash划分?什么鬼?不是直接把新程序烧进去就完事了吗? 结果一上手才发现,这玩意没那么简单,尤其是Flash怎么分,如果Flash划分没弄好&…...

游戏引擎学习第226天

引言,计划 我们目前的目标是开始构建“元游戏”结构。所谓元游戏,指的是不直接属于核心玩法本身,但又是游戏体验不可或缺的一部分,比如主菜单、标题画面、存档选择、选项设置、过场动画等。我们正在慢慢将这些系统结构搭建起来。…...

通过python实现bilibili缓存视频转为mp4格式

需要提前下好ffmpeg import os import fnmatch import subprocess Bilibili缓存的视频,*280.m4s结尾的是音频文件,*050.m4s结尾的是视频,删除16进制下前9个0,即为正常音/视频 使用os.walk模块,遍历每一个目录…...

Windows 图形显示驱动开发-WDDM 1.2功能—无显示器系统支持

一、架构设计与启动流程 1.1无显示器系统启动与全流程 graph TDA[UEFI固件] -->|FADT.VGA_NOT_PRESENT1| B[Windows Boot Manager]B -->|加载winload.efi| C[内核初始化]C -->|检测显示设备| D{存在GPU?}D -->|是| E[加载WDDM驱动]D -->|否| F[激活MSBDD虚拟…...

低代码 Web 组态

低代码配置式 Web 组态是一种用于创建 Web 应用程序界面的技术,它允许用户通过图形化界面和少量的代码或无需编写大量代码来配置和定制 Web 页面的布局、外观和交互功能。 一、特点 1、低代码或无代码开发:大大降低了开发门槛,无需专业的编程…...

解决7穴连接器的信号完整性问题

在汽车发动机的系统设计中,信号传输是不可或缺的。在信号传输中起着重要作用的一个关键组件是 7 穴连接器,它提供许多重要功能。 但是,这些连接器可能会遇到一些制造商需要解决的问题,知道如何解决 7 腔连接器中的信号完整性问题…...

)

GDScript快速入门(适合有其它编程语言基础)

GDScript快速入门(适合有其它编程语言基础) 从零开始学 GDScript Godot 是一款开源、跨平台的游戏引擎,因其轻量、易用和强大的功能而受到广大开发者的喜爱。在 Godot 中,GDScript 是其专为游戏开发设计的脚本语言,具…...

WEB安全--蓝队日志--RCE数据包分析

一、分析数据包内容 攻击者通过URL请求POST传参的方式试图绕过IPS测试RCE漏洞的利用 URL请求中的内容进行urlcode解码后是这样的: http://资产IP/hello.world?-d allow_url_include1 -d auto_prepend_filephp://input 1. -d allow_url_include1: 使…...

springboot项目添加定时任务,用sftp推送zip包到目标服务器

用sftp推送zip包到目标服务器 任务类里面,主要功能是,定时采集三张表的数据,并把数据转换成csv,三份csv压缩成一个加密的zip包,通过sftp推送到指定的目录下 配置类 Data Configuration ConfigurationProperties(pre…...

Mobaxterm 突破 14个 session 限制

mobaxterm 可以说非常好用,但是免费版对会话有限制,对于有很多虚拟机会话需要存储的我来说确实太少了。 当Xterm会话数量到14个时,发现新增的会话没有保存下来,在左侧菜单无法新增保存会话session。 超过限制时,提示…...

:Quantifying the Impact of Data Encoding on DNN Fault Tolerance)

体系结构论文(七十一):Quantifying the Impact of Data Encoding on DNN Fault Tolerance

Quantifying the Impact of Data Encoding on DNN Fault Tolerance 研究动机 深度神经网络(DNN)在硬件运行时可能遇到位翻转(bit-flip)错误,特别是在能效和面积敏感的平台上(如边缘设备、移动端࿰…...

学习笔记十一——零基础搞懂 Rust 函数式编程

🧠 零基础搞懂 Rust 函数式编程:到底什么是 “函数式”? Rust 是一门多范式语言,既可以像 C/Java 那样写“命令式代码”,也支持“函数式编程”。但很多刚入门的小伙伴可能会有这些疑问: 函数不就是函数吗&…...

Spark-SQL2

利用IDEA开发Spark-SQL 自定义函数 UDF: UDAF(自定义聚合函数) 强类型的 Dataset 和弱类型的 DataFrame 都提供了相关的聚合函数, 如 count(),countDistinct(),avg(),max(),min()。…...

python实战案例:玩具销售数据分析

原创 IT小本本 IT小本本 2025年04月12日 22:45 北京 本文将通过一个玩具销售数据的分析案例,展示如何利用 Python 和数据可视化工具从原始数据中提取有价值的商业洞察。将从数据加载、预处理到可视化分析,逐步揭示玩具销售的规律和趋势。 数据准备与加…...

模拟浏览器指纹:生成与定制特定属性

在现代网络环境中,浏览器指纹是一种强大的标识技术,用于区分不同的浏览器实例。通过收集浏览器的各种属性(如用户代理、Canvas 指纹、WebGL 特性等),可以生成一个独特的指纹,用于跟踪用户行为或防止欺诈。本…...

vue+vite 减缓首屏加载压力和性能优化

vuevite 减缓首屏加载压力和性能优化 1、预加载项目必需的组件2、模块加载优化3、HMR 热更新优化4 、环境配置优化5、代码模式优化6、高级优化技巧7、架构级优化打包压缩配置 在vuevite构建的工程里面,性能优化分为开发环境和打包后的生产环境,作为开发首…...

狂神SQL学习笔记十三:Delete 和 Truncate 详解

1、删除 保留表的结构不变,清空表的数据 truncate重新设置 自增列 计数器会归零,如果用delete删除,则自增不会变,重新插入数据时自增会从原来的地方开始...

封装实用的时间选择器组件

<template><!-- 使用该时间选择器组件,重置搜索表单的时候,注意得使用async await让重置表单操作完成后再发起请求 --><div class"dateTimePickerSelectWrap"><el-date-pickerv-model"arr":type"dateType…...

关于Blade框架对数字类型的null值转为-1问题

关于Blade框架对数字类型的null值转为-1问题 问题:最近项目遇到了一个问题,SpringBoot项目后端Long类型的数据,如果是NULL的话,返回给前端的时候是-1。如下图: 分析 是由于使用了 blade 框架,项目启动的…...

如何安全地管理固定功能设备?

什么是固定功能设备? 固定功能设备是指具有特定、单一或有限功能的设备,其功能在设计和制造时就被固定下来,通常难以进行大规模的功能扩展或修改。固定功能设备只需要运行特定的应用程序。自动取款机、销售商家用机器、支付站点以及其他专门…...

AttributeError: ‘NoneType‘ object has no attribute ‘pydev_do_not_trace‘

目录 问题描述1. **IDE缓存损坏**(此办法帮我解决问题)2. **PyCharm版本过旧**3. **Python解释器配置问题**4. **第三方库或插件冲突**5. **重置调试配置**其他建议问题原因分析 问题描述 print(ok) Traceback (most recent call last):File "D:\pycharm\PyCharm Communi…...

协享云图分析--3用户模块

用户表 -- 用户表 create table if not exists user (id bigint auto_increment comment id primary key,userAccount varchar(256) not null comment 账号,userPassword varchar(512) not null comment 密码…...

visual studio 如何在 release 模式下调试

在 Visual Studio 中,在 Release 模式下进行调试, 以下是具体步骤: 一、修改项目属性: 右键点击解决方案资源管理器中的项目,选择“属性”。 在“生成”选项卡中,找到“定义 DEBUG 常量”和“定义 TRACE 常量”&…...

课堂总结。

第三章第六节 Spark-SQL核心编程(五)自定义函数:UDF:val sparkConf new SparkConf().setMaster("local[*]").setAppName("SQLDemo")//创建SparkSession对象val spark :SparkSession SparkSession.builder()…...

JDBC 初认识、速了解

目录 一. JDBC的简介 1. 数据的持久化 2. 什么是JDBC 二. JDBC中常用的类和接口 1. Driver 接口 2. DriverManager 类 3. Connection 接口 4. Statement 接口 5. PreparedStatement接口 6. ResultSet 接口 三. 总结 前言 从现在开始就来讲解JDBC的相关知识了 本文的…...

双指针算法

引入 双指针顾名思义,就是同时使用两个指针,在序列、链表结构上指向的是位置,在树、图结构中指向的是节点,通过或同向移动,或相向移动来维护、统计信息。 ——OI Wiki 接下来我们来看双指针的几个具体使用方法。 板子…...

关于TD算法的笔记【时间差分】

1. TD算法逻辑:TD算法即时间差分算法,结合了蒙特卡洛方法和动态规划思想,通过当前估计值和下一个时间步观测值更新状态价值估计,无需完整episode或环境完整信息。 2. 下一时刻估计值计算:下一时刻估计值为 r_{t 1}\g…...

计算斐波那契数列

1.对于斐波那契数列的理解: (1)常规 该数列由兔子繁衍的想法产生,故又“兔子数列” 其数值为:1、1、2、3、5、8、13、21、34 从数学定义上走:F(0)1,F(1)1, F(n)F(n - 1)F(n - 2)(n ≥ 2,n ∈…...

Oracle REGEXP_SUBSTR

在 Oracle 数据库中,REGEXP_SUBSTR 是一个基于正则表达式的字符串处理函数,用于从目标字符串中提取符合特定模式的子串。它比传统的 SUBSTR 函数更灵活,适用于复杂的模式匹配需求。以下是其核心原理、参数解析及实际案例详解: 一…...

无人机自主导航与路径规划技术要点!

一、自主导航与路径规划技术要点 1. 传感器融合 GPS/北斗定位:提供全局定位,但在室内或遮挡环境下易失效。 惯性测量单元(IMU)**:通过加速度计和陀螺仪实时追踪姿态,弥补GPS信号丢失时的定位空缺。 …...

DDS波形发生器仿真及技术原理

1. 引言 在现代数字信号处理、电路设计以及通信系统中,直接数字频率合成(DDS)技术因其高速、精细的频率分辨率以及连续相位输出等优点而得到广泛应用。本文主要探讨在DE2-115开发板平台上基于DDS技术实现波形发生器的设计与实践。通过该设计…...

Java使用ANTLR4解析IDL文件

文章目录 前言解析IDL文件准备两个IDL文件准备一个IDL Grammar文件maven配置生成Lexer Parser Listener Visitor代码新建实体类IDL解析遍历器单元测试 参考 前言 接着上篇:Java使用ANTLR4对Lua脚本语法校验,介绍了什么是ANTLR?/ 举了一个hel…...

04-Seata 深度解析:从分布式事务原理到 Seata 实战落地

Seata 深度解析:从分布式事务原理到 Seata 实战落地 一、分布式事务核心理论与挑战 1.1 分布式事务的本质难题 在微服务架构中,一次业务操作可能涉及多个服务的数据库操作,传统单体事务(ACID)无法跨越服务边界&…...

2025企业增长新引擎:AI Agent驱动人效跃迁|白皮书2.0发布

2025年伊始,一款名为DeepSeek-R1的国产AI大模型以其高性能、低成本等核心优势成功霸榜热搜,在全国乃至全球掀起一场以AI为核心的技术革新与管理变革。 面对这样极具颠覆性的革新命题,易路人力资源科技王天扬先生自2022年起就率团队持续专注于…...

IJCV-2025 | 深圳大学记忆增强的具身导航!ESceme:基于情景记忆的视觉语言导航

作者:Qi Zheng 1 , 2 ^{1,2} 1,2, Daqing Liu 3 ^{3} 3, Chaoyue Wang 3 ^{3} 3, Jing Zhang 2 ^{2} 2, Dadong Wang 4 ^{4} 4, Dacheng Tao 2 ^{2} 2单位: 1 ^{1} 1深圳大学电子与信息工程学院, 2 ^{2} 2悉尼大学计算机科学学院,…...

[第十六届蓝桥杯 JavaB 组] 真题 + 经验分享

A:逃离高塔(AC) 这题就是简单的签到题,按照题意枚举即可。需要注意的是不要忘记用long,用int的话会爆。 📖 代码示例: import java.io.*; import java.util.*; public class Main {public static PrintWriter pr ne…...

《分布式软总线:网络抖动下的数据传输“定海神针”》

在当下,智能设备之间的互联互通已成为生活与工作的刚需。分布式软总线作为实现这一愿景的关键技术,正日益凸显其重要性。然而,网络环境的复杂性,尤其是网络抖动频繁的情况,给分布式软总线的数据传输带来了严峻挑战。如…...

C++函数

函数 为什么要使用函数 已经有main函数,为什么还要自定义函数?:“避免重复制造轮子”,提高开发效率 函数的定义 函数的设计方法:先确定函数的功能、确定函数的参数、是否需要参数,参数的个数,…...

·空闲任务与阻塞延时的实现)

FreeRTOS菜鸟入门(五)·空闲任务与阻塞延时的实现

目录 1. 实现空闲任务 1.1 定义空闲任务的栈 1.2 定义空闲任务的任务控制块 1.3 创建空闲任务 2. 实现阻塞延时 2.1 vTaskDelay()函数 2.2 修改 vTaskSwitchContext()函数 3. SysTick 中断服务函数 4. SysTick 初始化函数 通过之前我们了解知道,任…...

)

PCIe 学习笔记(一)

系列文章目录 【PCIe】链路测试,数字工程师也要会看高速信号眼图! 【PCIe】链路训练状态机(LTSSM) - PCIe链路建立过程概述 【PCIe】PCIe设备的BDF与系统枚举过程 文章目录 系列文章目录PCIe LTSSM**1. 链路训练状态(Training States&#…...

【正点原子STM32MP257连载】第四章 ATK-DLMP257B功能测试——LED、按键测试

1)实验平台:正点原子ATK-DLMP257B开发板 2)浏览产品:https://www.alientek.com/Product_Details/135.html 3)全套实验源码手册视频下载:正点原子资料下载中心 文章目录 第四章 ATK-DLMP257B功能测试4.1 LED…...

深度为16,位宽8bit的单端口SRAM——学习记录

链接: 【Verilog HDL 训练】第 13 天(存储器、SRAM)-云社区-华为云 module sram #(parameter ADDR_BITS4)(input clk,input [ 7:0] addr,input [ 7:0] din,input ce,input we,output reg [ 7:0] dout);localparam MEM_DEPTH 1<<ADDR_…...