【ALINX 实战笔记】FPGA 大神 Adam Taylor 使用 ChipScope 调试 AMD Versal 设计

本篇文章来自 FPGA 大神、Ardiuvo & Hackster.IO 知名博主 Adam Taylor。在这里感谢 Adam Taylor 对 ALINX 产品的关注与使用。为了让文章更易阅读,我们在原文的基础上作了一些灵活的调整。原文链接已贴在文章底部,欢迎大家在评论区友好互动。

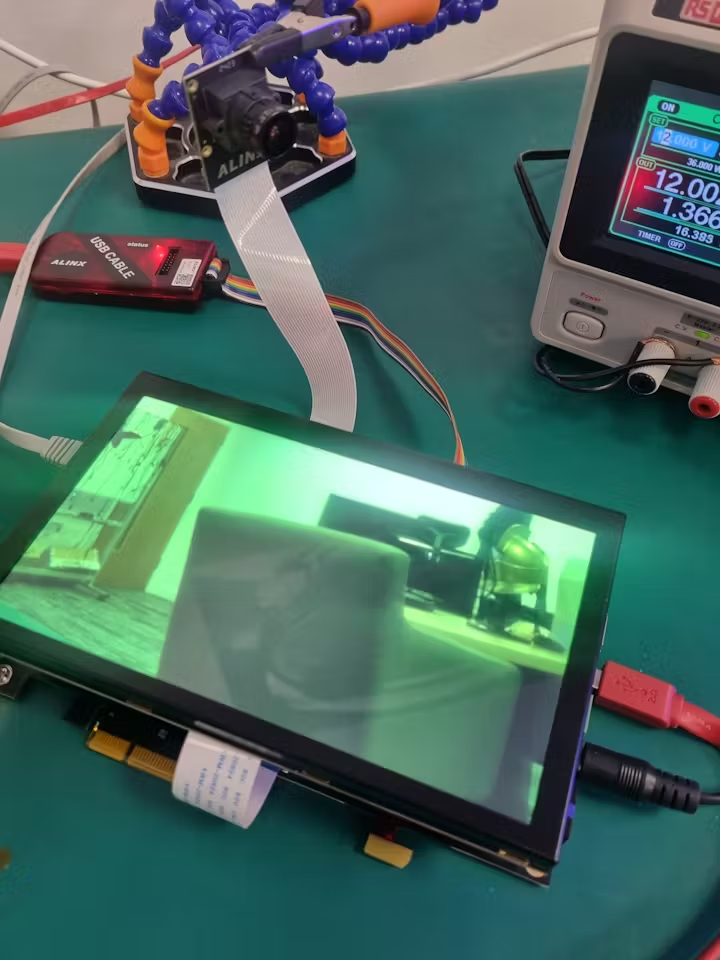

在上篇文章中,我们已经通过测试图案生成器,成功验证了 ALINX VD100 的图像显示链路。

这次终于要接入 MIPI 摄像头,进行真正的图像处理了!

在这个过程中,集成逻辑分析仪(ILA)将作为我们的调试“透视眼”,帮助我们逐步验证每一阶段的运行效果。

本项目规模不小,从图像采集到处理再到输出,每一环都可能出现问题——做好调试准备了吗?

那就让我们开始吧!

项目工具清单

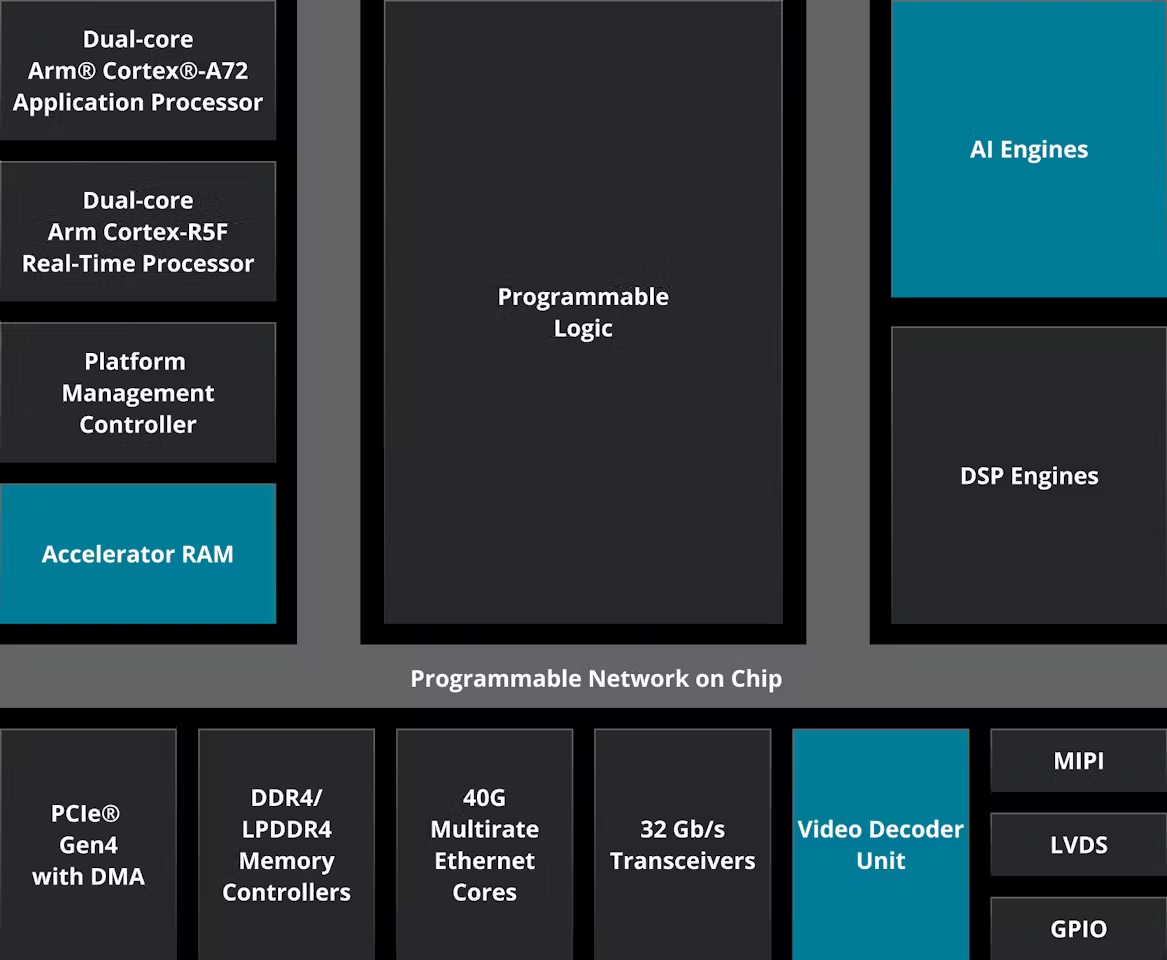

本次开发平台基于 AMD Versal AI Edge 芯片,开发板采用 ALINX 的 VD100。

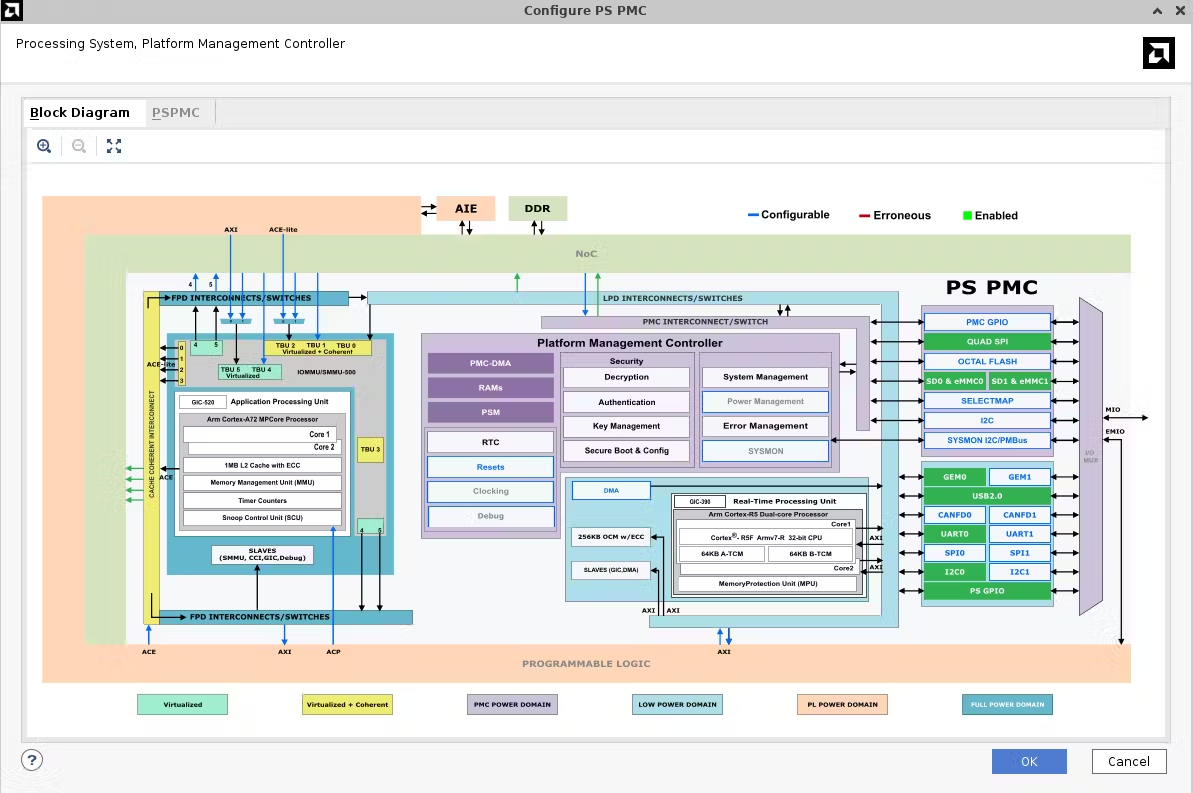

Versal AI Edge 系列是 AMD 推出的系统级异构芯片(SoC),专为边缘端 AI 应用优化,集成了 Arm Cortex-A72 应用处理器、Cortex-R5F 实时处理器、可编程逻辑(PL)以及 AI 引擎专用加速模块等多种处理单元。这些模块通过片上网络(NoC)实现高效互联,形成强大灵活的计算平台,非常适合本地化部署卷积神经网络(CNN)等 AI 推理任务。

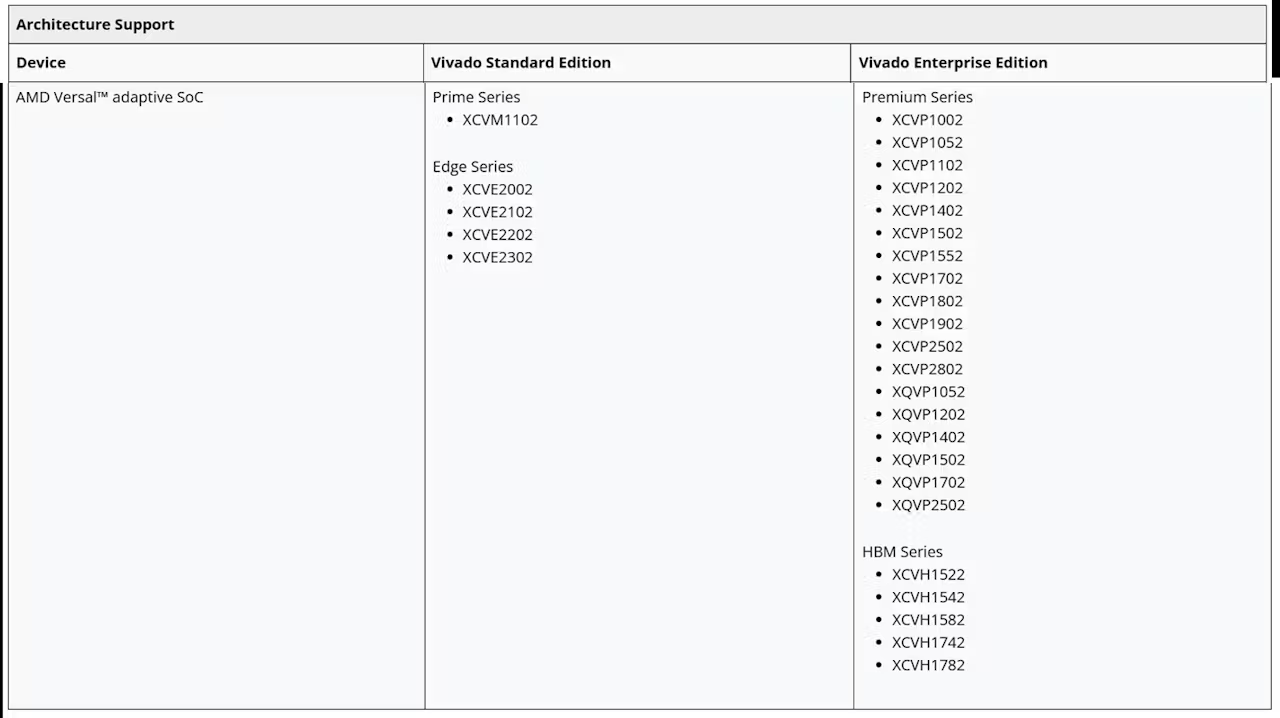

ALINX VD100 开发板配备了 2 个 4 通道的 MIPI 摄像头输入接口,以及一个 LVDS LCD 显示输出,并且支持 Vivado免费版开发环境,对原型验证和早期开发者极其友好。

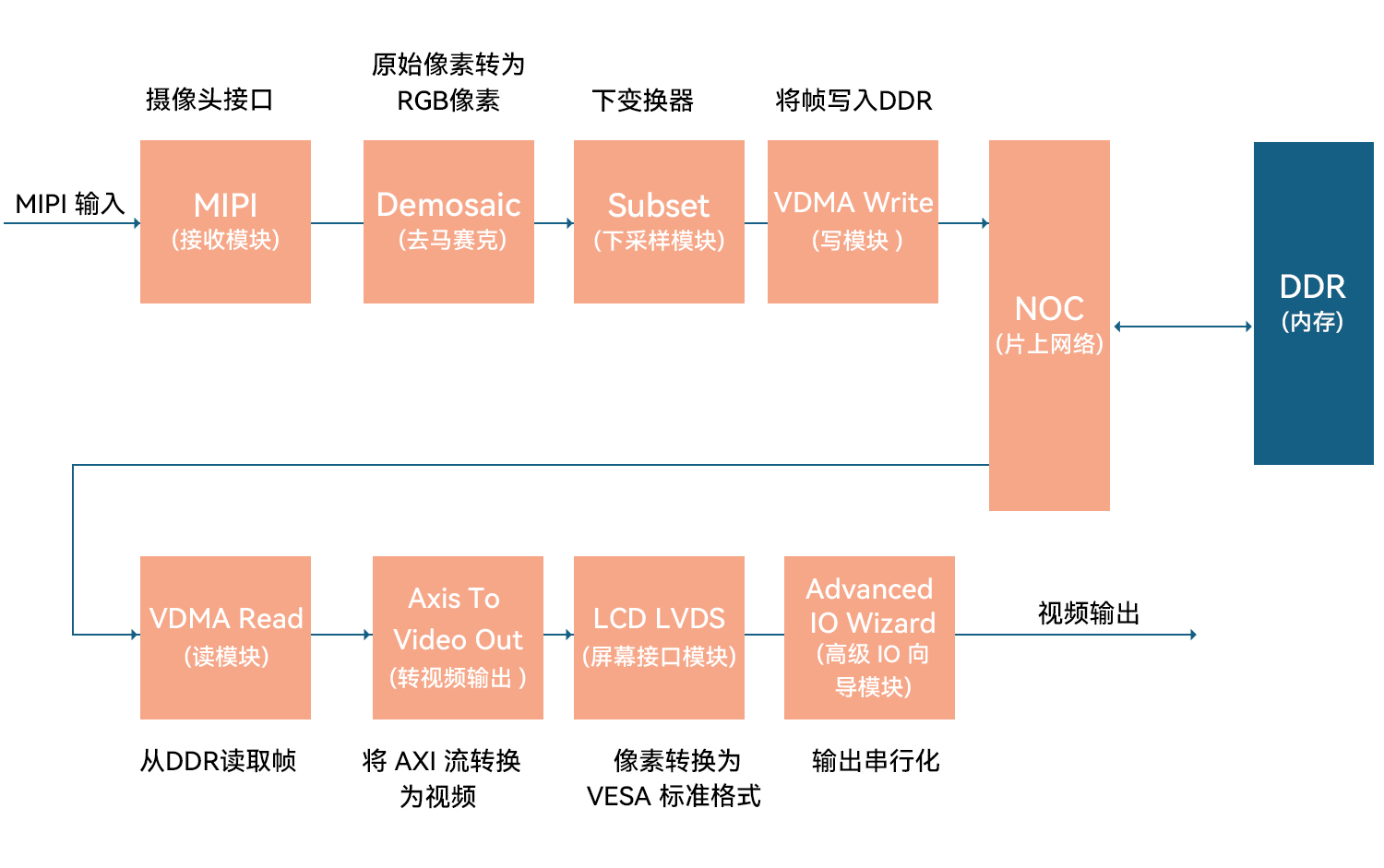

在进入 AI 阶段前,我们需要打好基础——构建一条稳定的图像处理通路。基本流程如下:

1. 图像采集(MIPI 摄像头)

2. 预处理(去马赛克、颜色空间转换、图像增强)

3. 缓存存储(VDMA + DDR)

4. 图像显示(LVDS LCD 输出)

一个可靠的图像通路必须满足三个条件:

1. 摄像头正常采集

2. 数据通路不丢包

3. 显示输出无错帧

通过早期验证这些关键环节,可确保 I/O 分配、时钟策略和图像处理流程的正确性,降低在集成上层 AI 逻辑或应用功能时的开发风险。只有基础打牢,后续的开发迭代才能更高效,项目推进也更有把握。

Versal 调试机制

虽然 Versal 器件的应用调试与 7 系列、UltraScale 及 UltraScale+ 系列大体相似(均可使用 ChipScope 工具),但在使用方式上也发生了一些变化:

| _ | 旧平台(7/US/US+等) | Versal 平台 |

| Debug hub 连接方式 | 通过 JTAG 接口 | 通过 CIPS 中的 AXI4 接口 |

| Debug hub 插入方式 | 自动插入 | 自动/手动 (涉及 DFX 必须手动) |

| Debug Core 接口协议 | 专有接口 | 标准 AXI4-Stream |

| AXI-Stream ILA 特性 | 集成标准ILA+System ILA 支持 BRAM/URAM存储介质选择 | 标准 ILA 与 System ILA 分立 存储介质固定 |

Versal 的调试架构更加现代化,也更加灵活,但也意味着你在设计之初就必须考虑调试资源的布局,尤其是 CIPS 模块和 AXI 调试路径 的预留。

调试方法论

FPGA 开发是一个需要多次迭代的过程,只有遵循逻辑推理的方法,才能更高效地解决问题,不至于造成资源浪费。我在调试时遵循以下原则帮助我更快速地排查问题:

1. 问题拆解:将复杂问题拆解为更小的部分

2. 控制变量:减少变量与干扰项

3. 假设验证:做出合理预测,并验证预测结果

4. 前瞻规划:在设计初期就规划好调试方案与观测点位置

ILA 插桩策略

集成逻辑分析仪(ILA)使用起来非常占用逻辑和 BRAM 资源,且采样深度、监控信号的宽度也会直接影响 BRAM 的使用量——探针越宽、采样窗口越长,占用的内存越多,资源也越快耗尽。

在真实项目中使用 ILA 进行调试时,必须合理选择插桩位置,以平衡调试可视性与 FPGA 资源的使用。我的建议是,在遵循前述调试方法论的条件下:

1. 优先监控控制信号、复位线、状态/错误标志等关键位置。这些信号通常可以第一时间反映系统行为,帮助我们在调试早期就定位问题。

2. 逐步拓展至一些关键的 AXI 总线,尤其是连接 Versal 的片上网络(NoC)与处理系统(PS)的部分,这些接口是可编程逻辑(PL)、NoC 与 PS 之间的数据主通道,能揭示系统集成与数据传输过程中的一些微妙问题。

因此,在调试初期,我们可以从一组合理的控制信号、复位、状态/错误信息以及关键 AXI 接口信号入手,采用中等采样深度。

这样既能获得系统层面的良好可视性,又能为后续迭代调试保留资源空间。

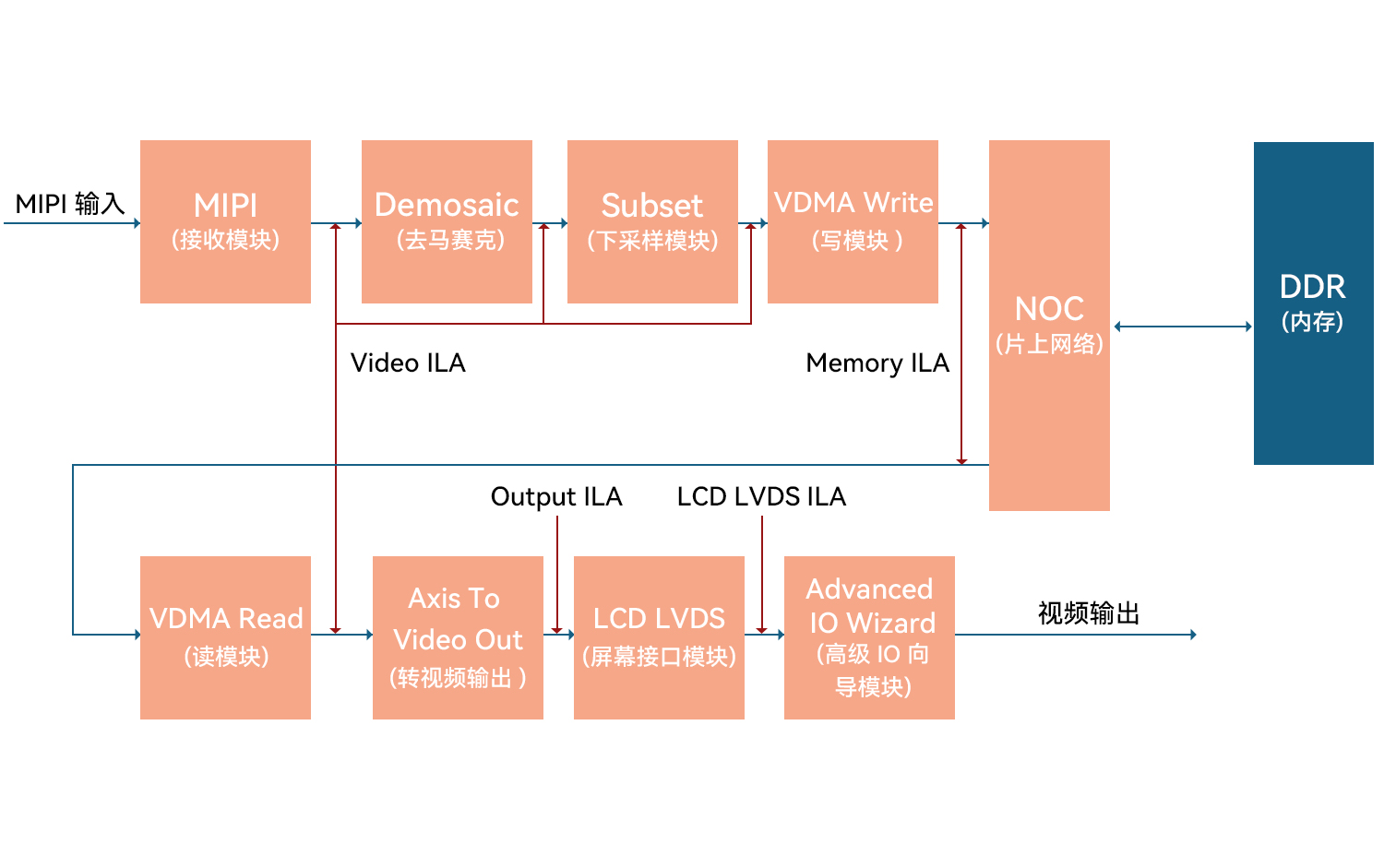

Vivado 设计架构

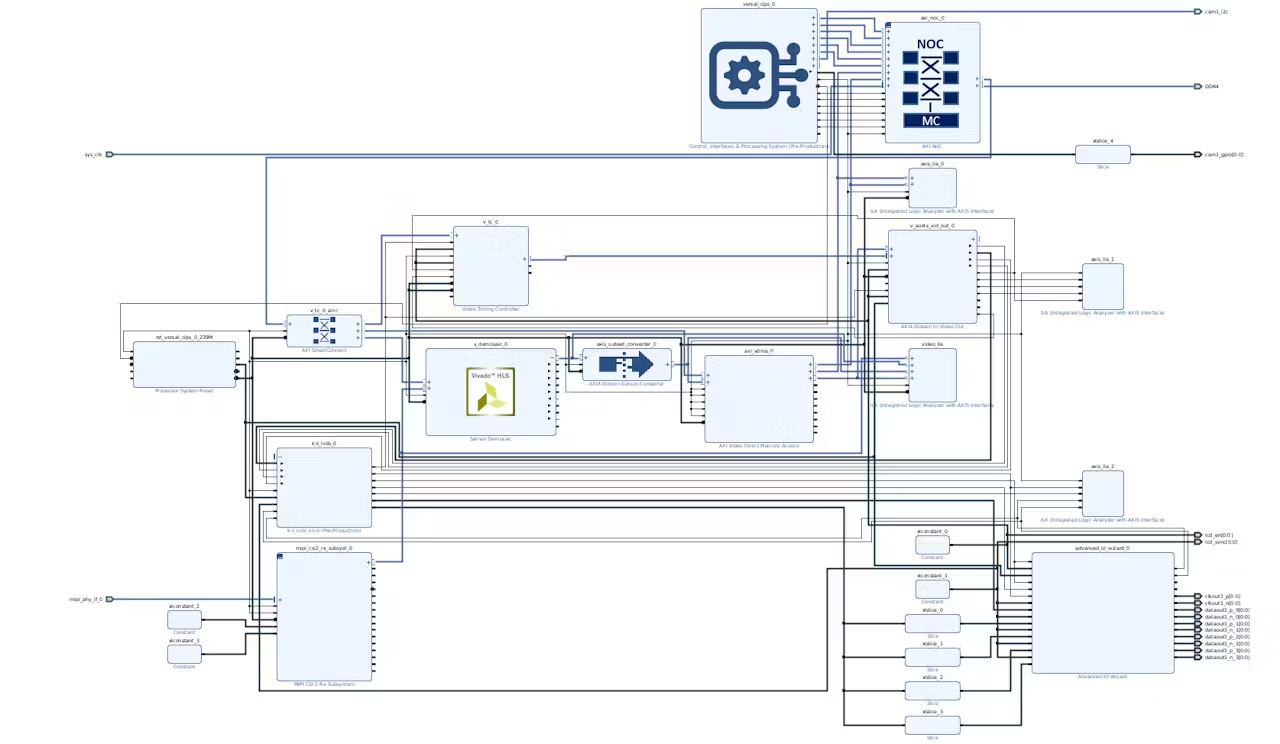

基于 Versal AI Edge 的图像处理流水线,核心架构通过 CIPS 模块实现全局控制;图像帧通过一系列 IP 模块被采集与处理;应用程序、DDR 内存访问以及 CIPS 与可编程逻辑(PL)之间的通信,通过片上网络(NoC)实现高速互联。

系统的整体结构如下图所示:

具体使用的 IP 核取决于应用需求,但核心流水线一般包括:传感器接口、去马赛克(Demosaic)、颜色空间转换、图像增强、视频时序控制模块,以及 AXI Stream 的互联与控制逻辑。

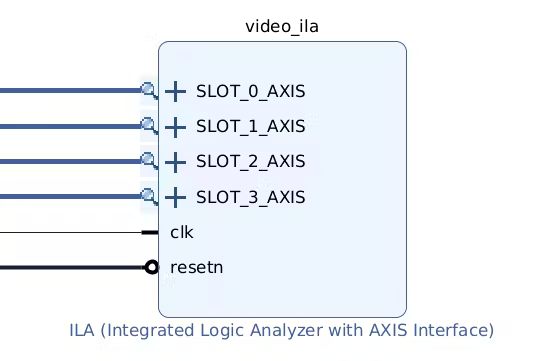

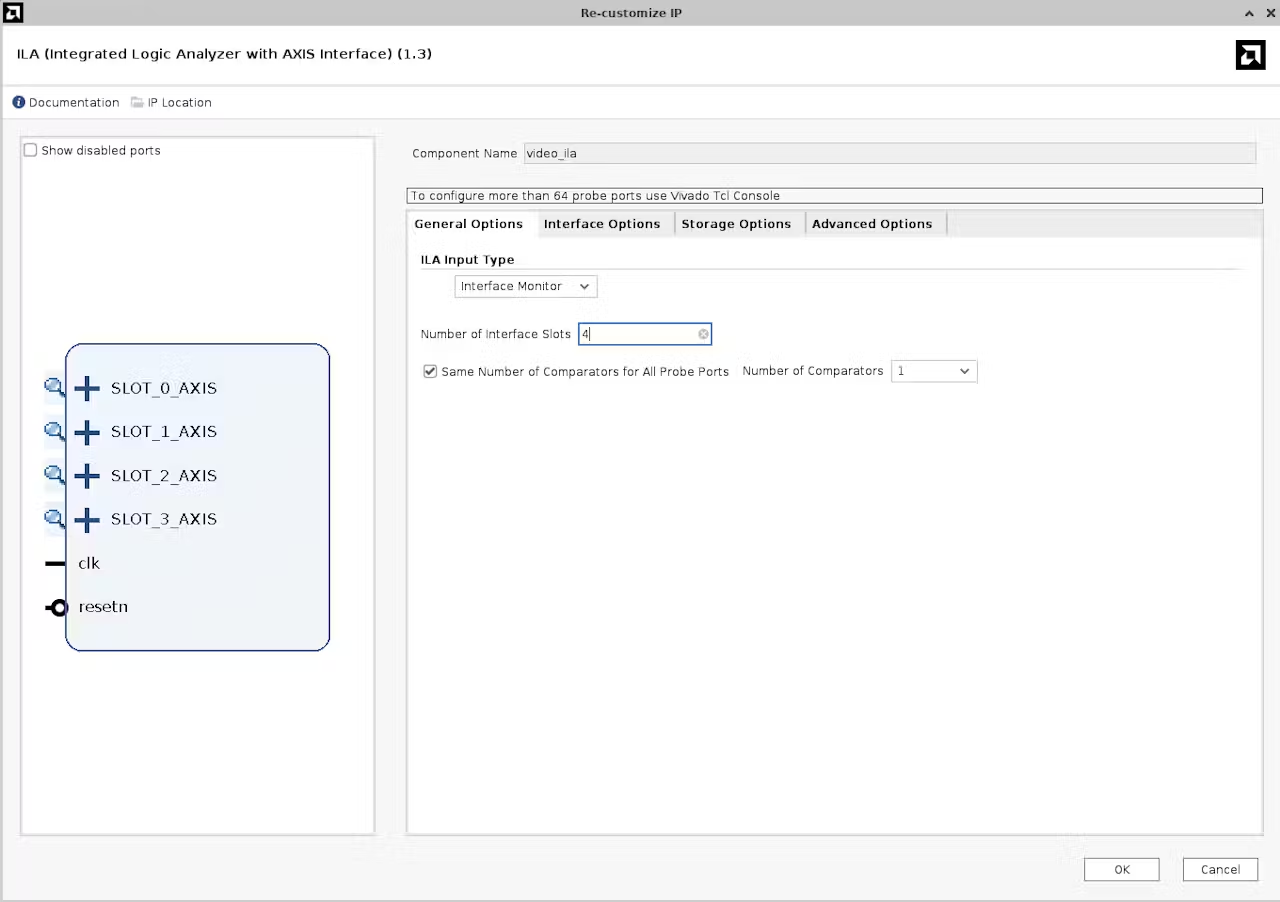

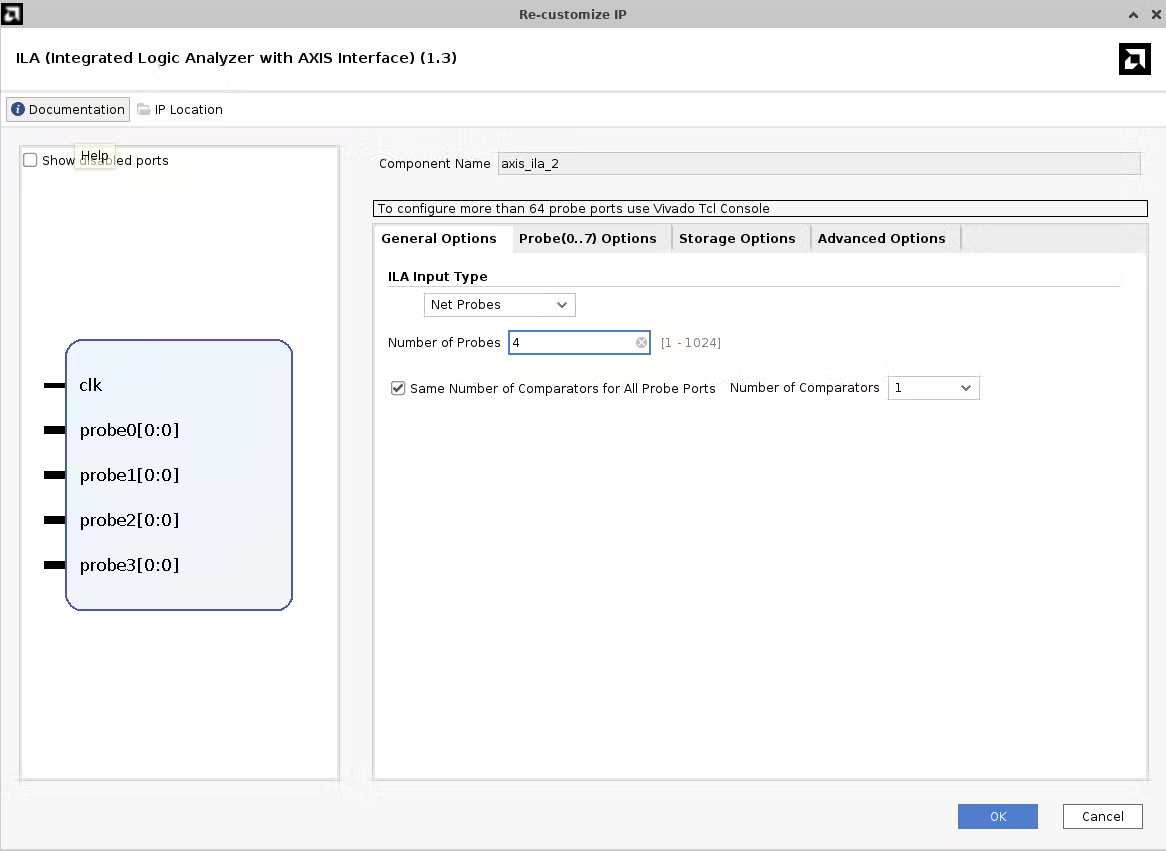

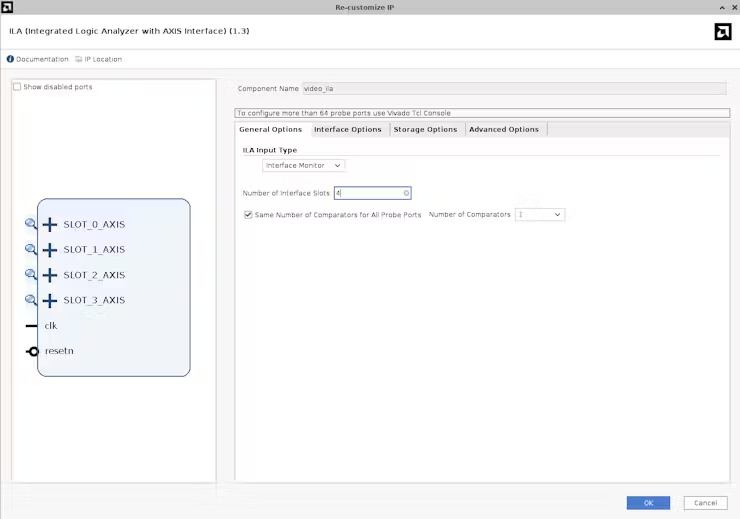

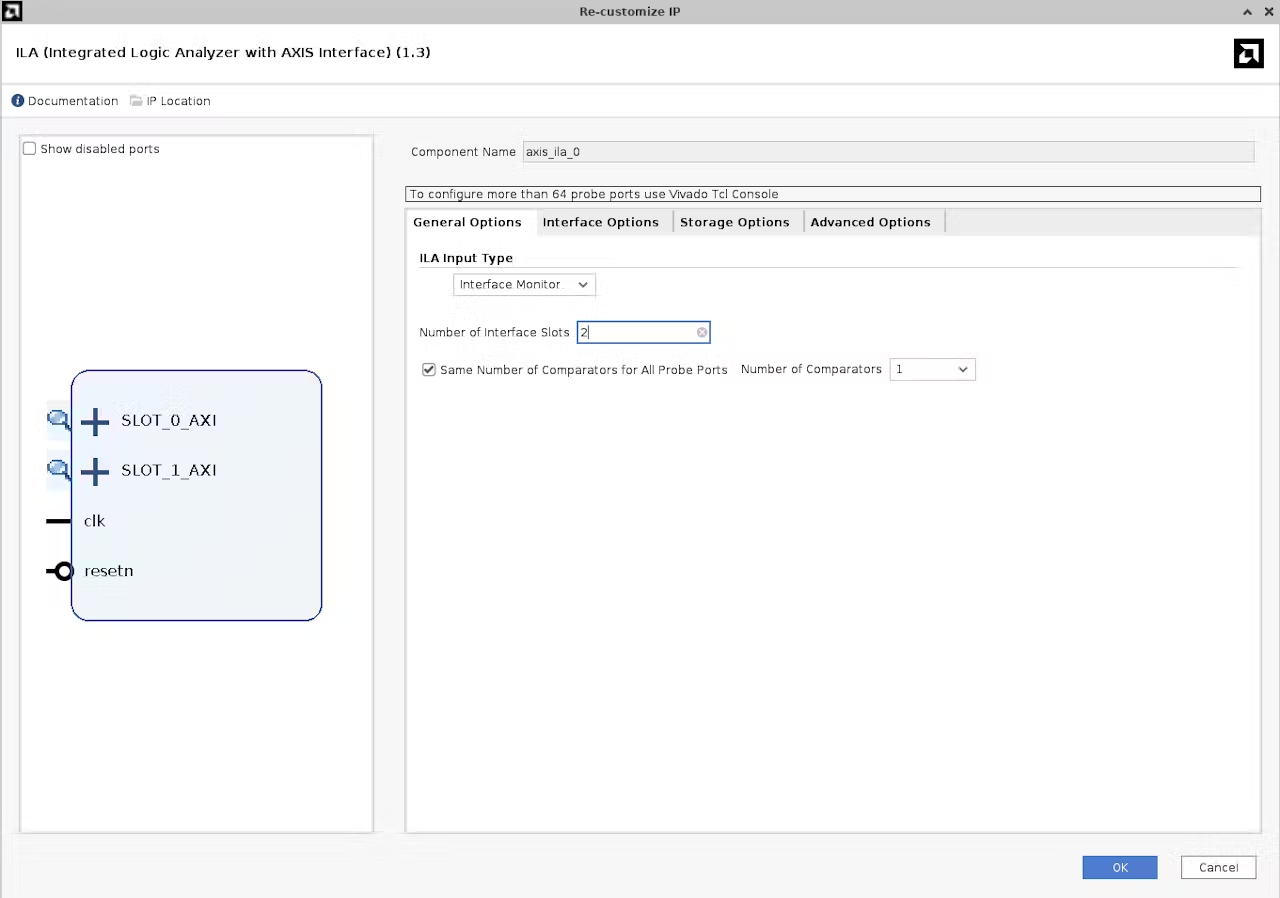

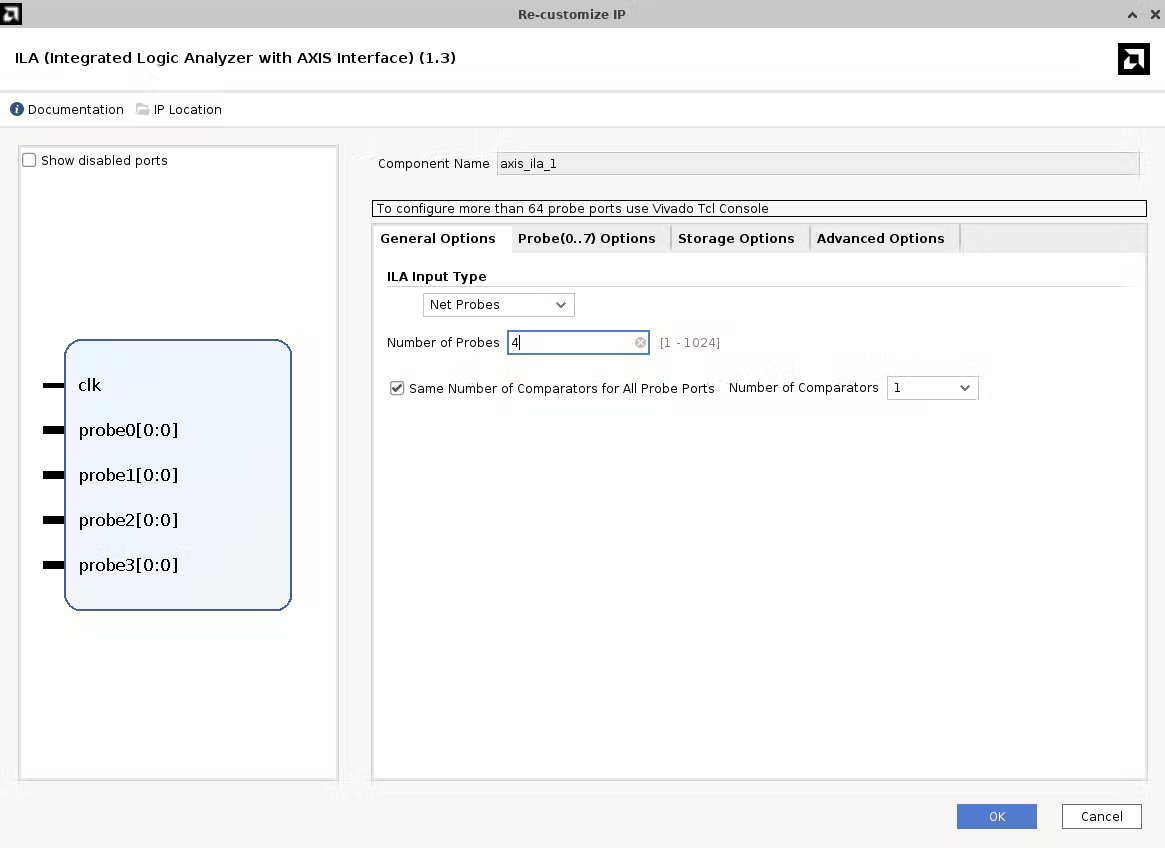

ILA 模块

ILA_LCD_LVDS

→ 监控 LCD / LVDS 接口,观察状态与错误信号。

Video ILA

→ 使用四个通道,监控图像处理流程中的 AXI-Stream 视频信号,包括 MIPI 原始输出、去马赛克后的 RGB 流、24 位像素转换输出与 VDMA 输出流。

Memory ILA

→ 监控通过 NoC 访问 DDR 的 AXI4 总线,确保 DDR 的读写操作正常进行。

Output ILA

→ 监控 AXI-Stream 到视频输出的状态信息,如视频输出同步信号诊断(HSync/VSync 相位对齐监测)

IP 模块

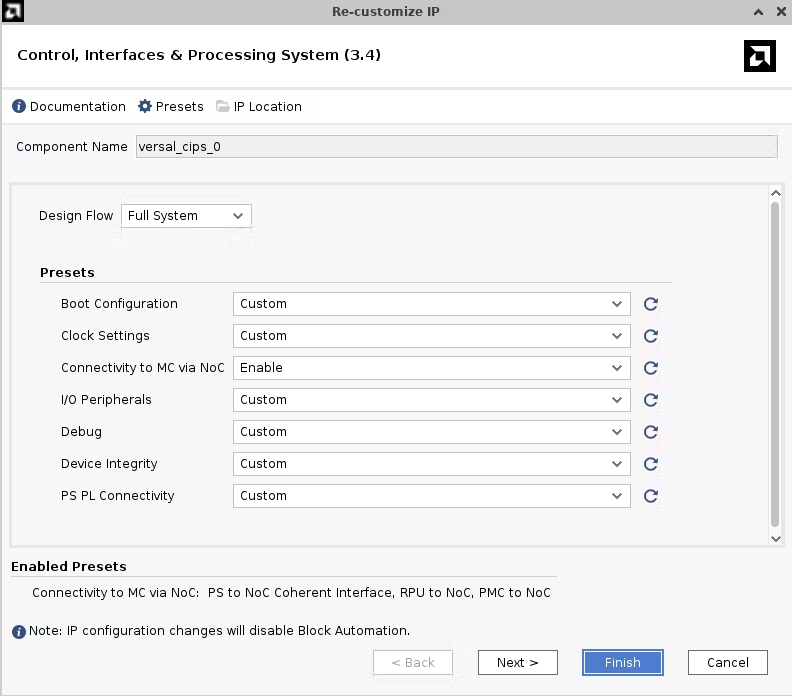

CIPS

→ 配置处理系统(PS)、平台初始化,提供外设访问。

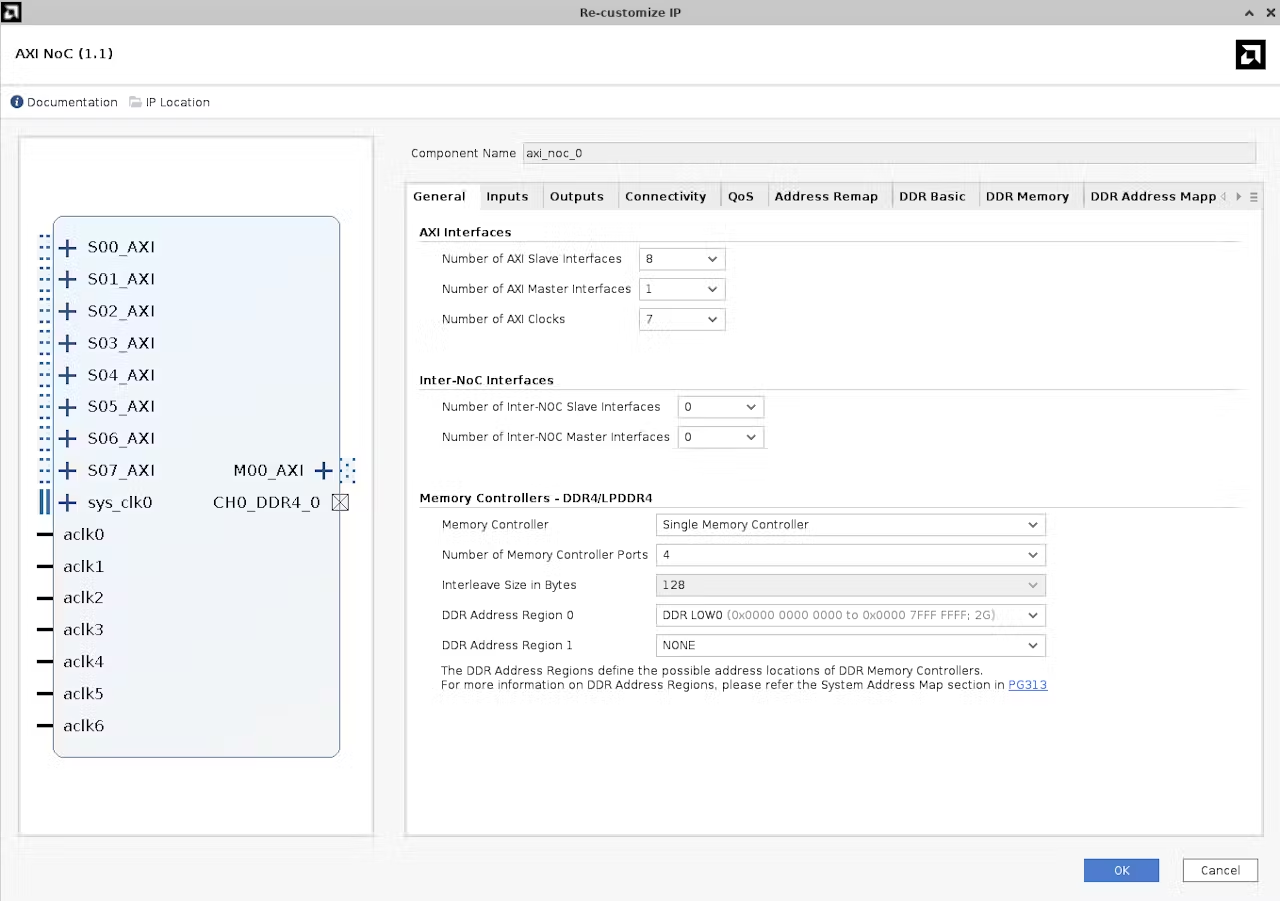

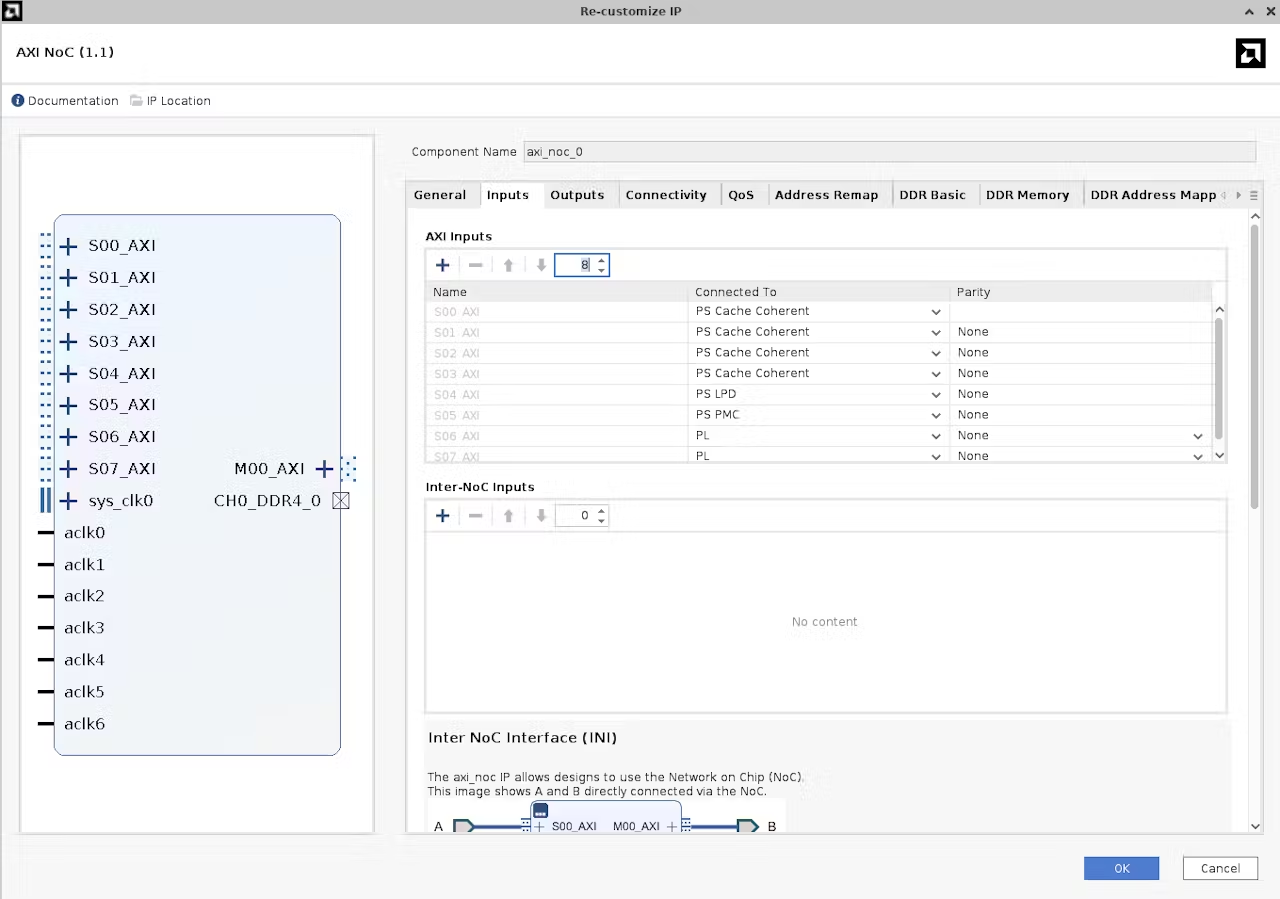

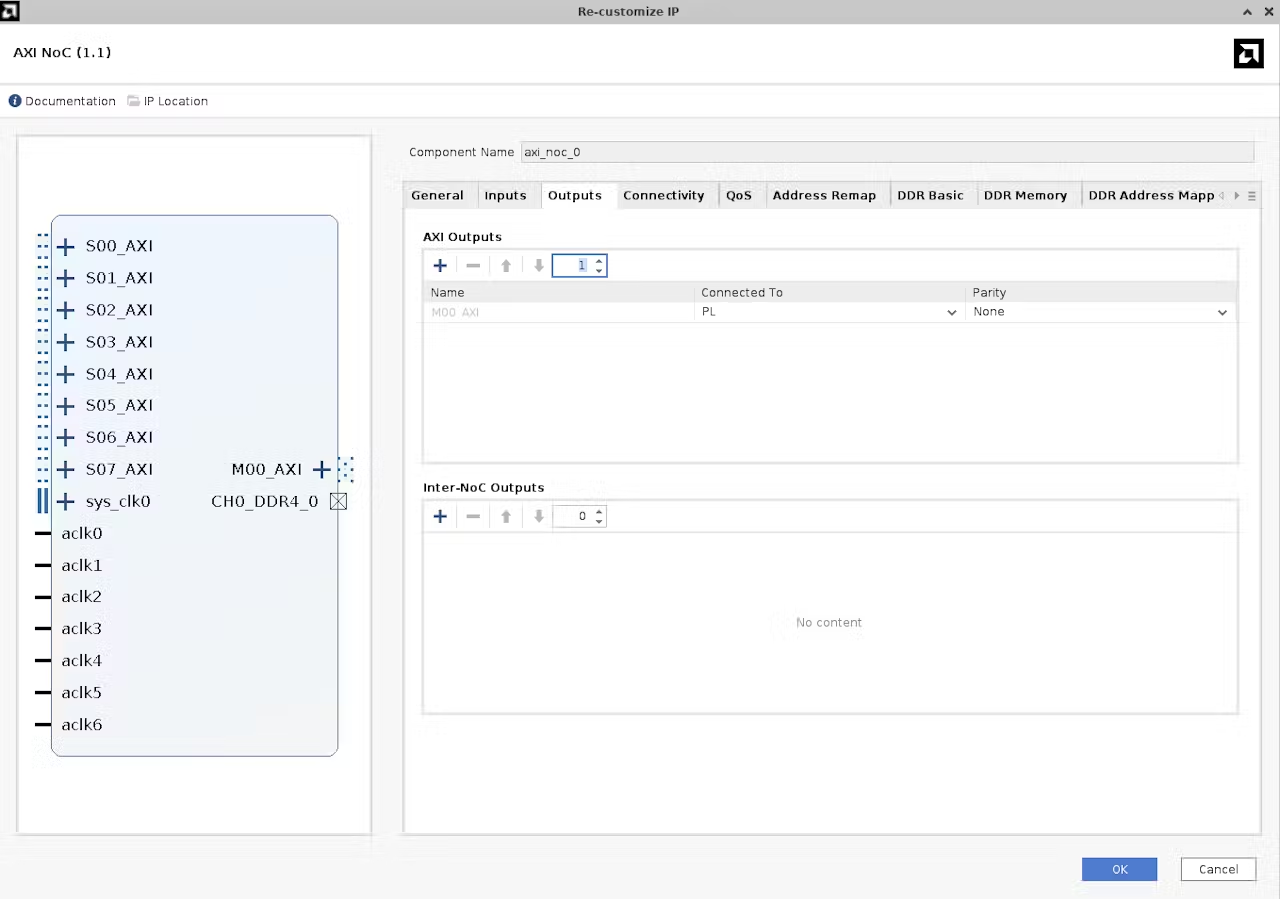

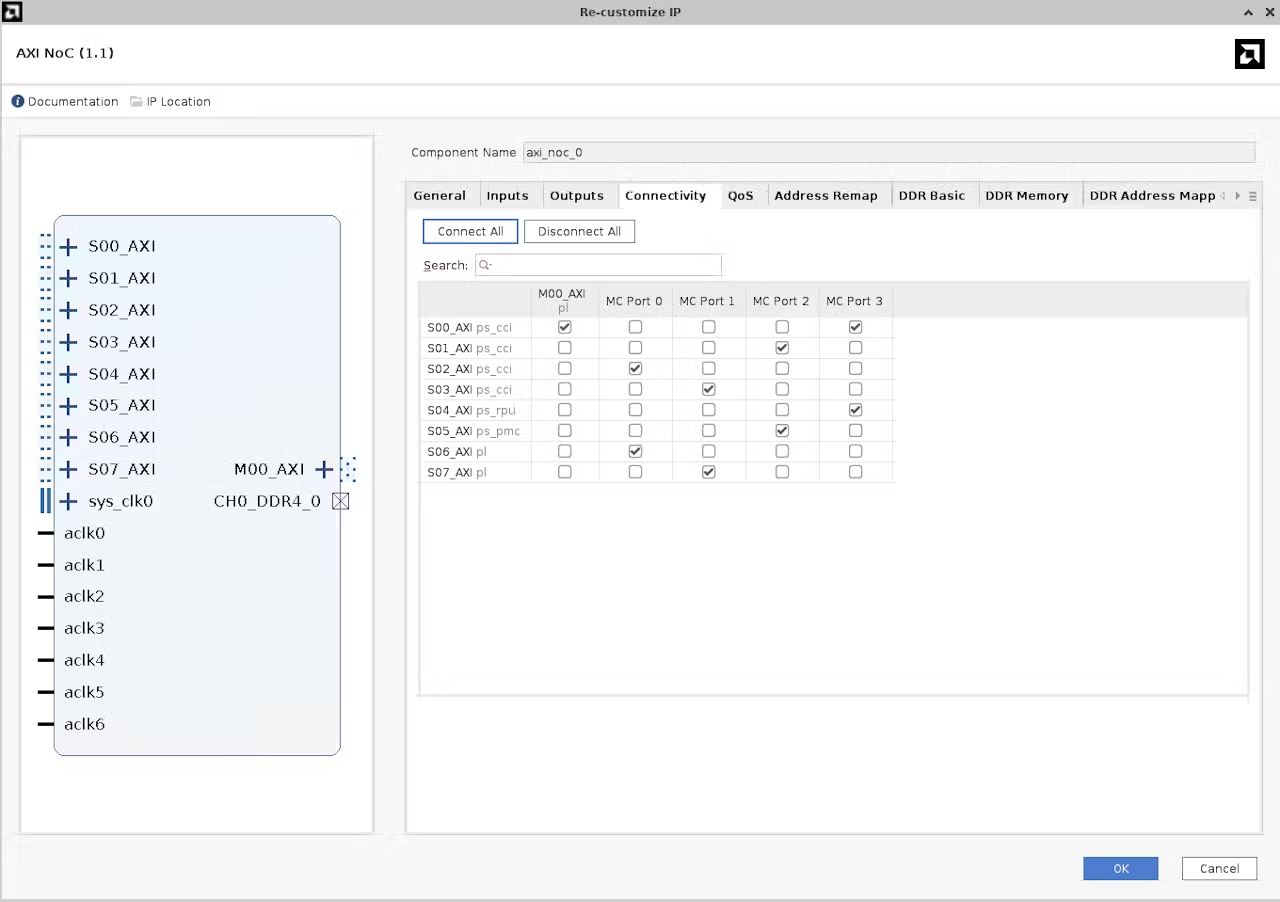

NoC

→ 提供高带宽的数据流通通道,连接多个互联节点,并集成 DDR 控制器用于外部内存访问。

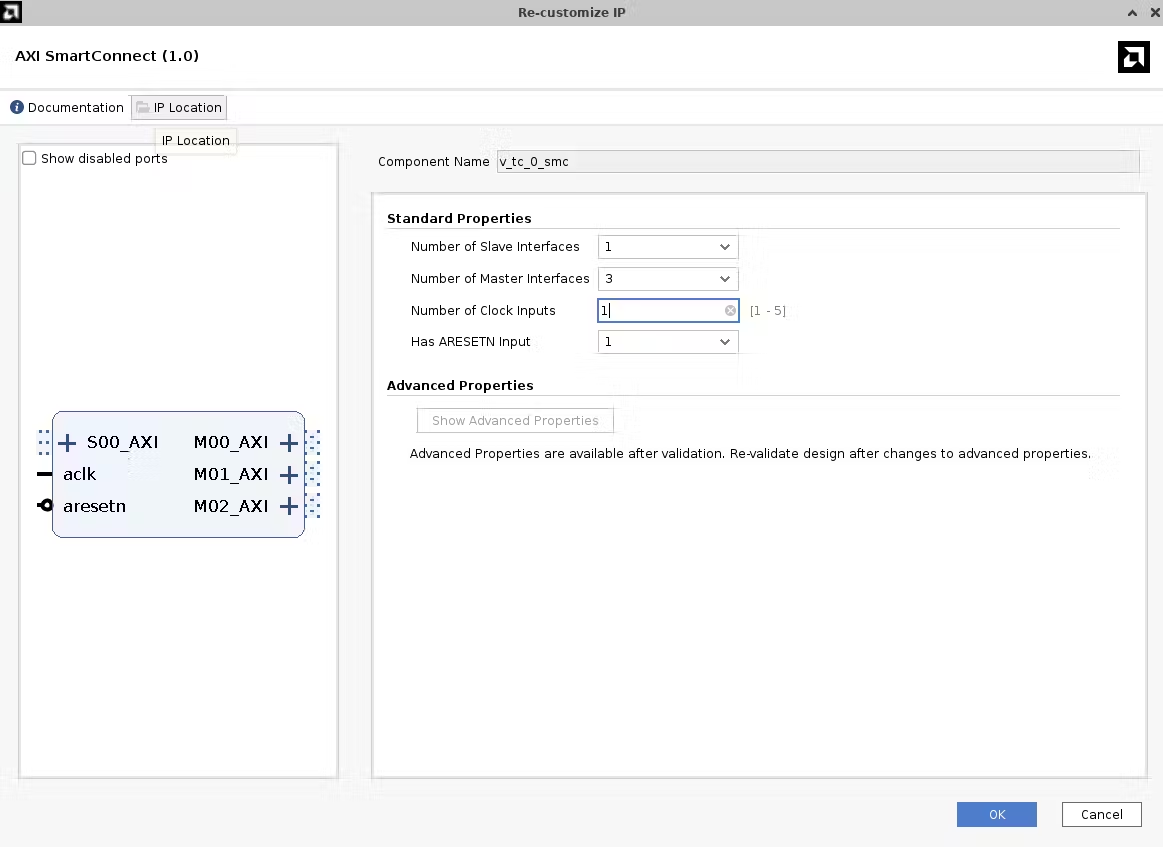

SmartConnect

→ 连接各 IP 模块的 AXI-Lite 寄存器接口,使处理系统可以对其进行控制与配置。

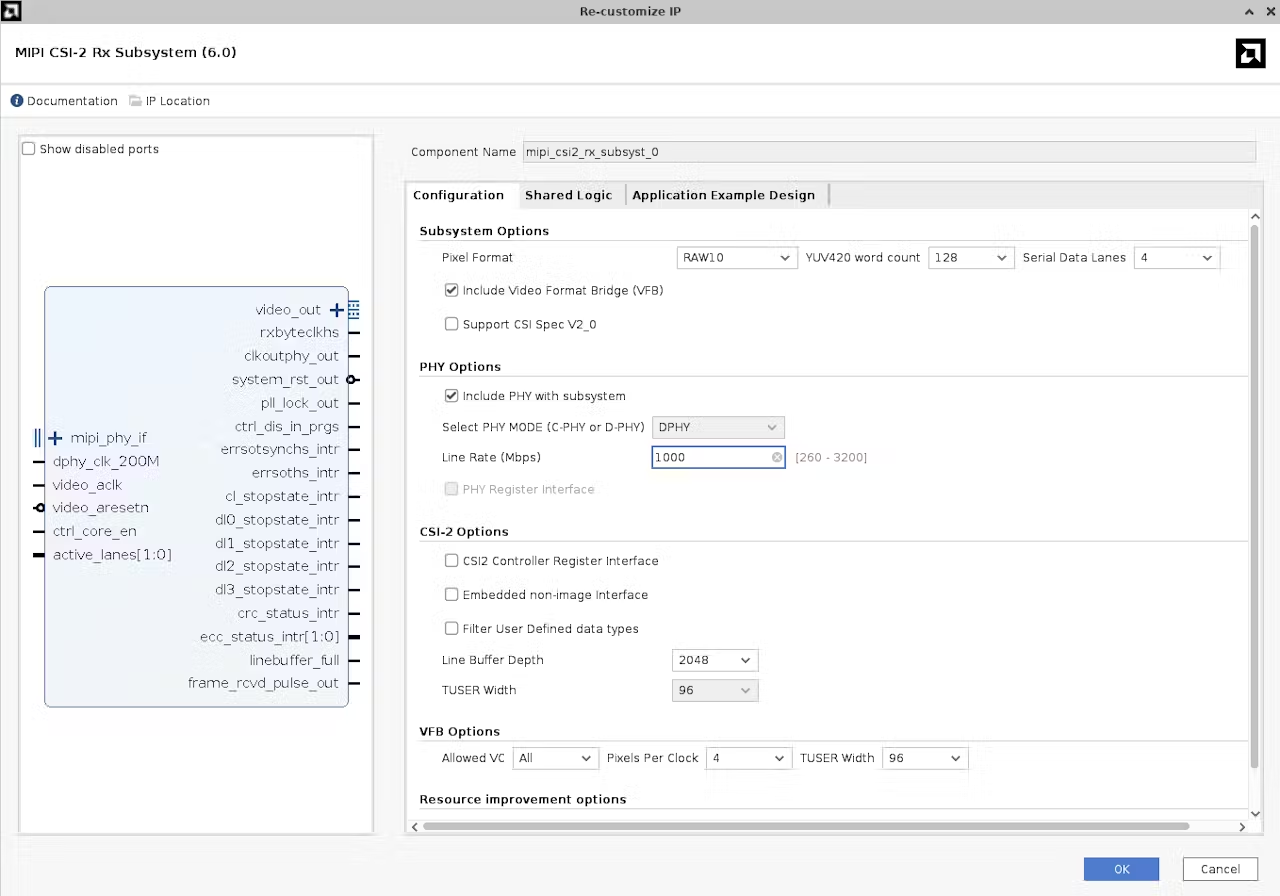

MIPI CSI-2 RX

→ 支持 4 通道,每通道 1000 Mbps 的高速图像采集。

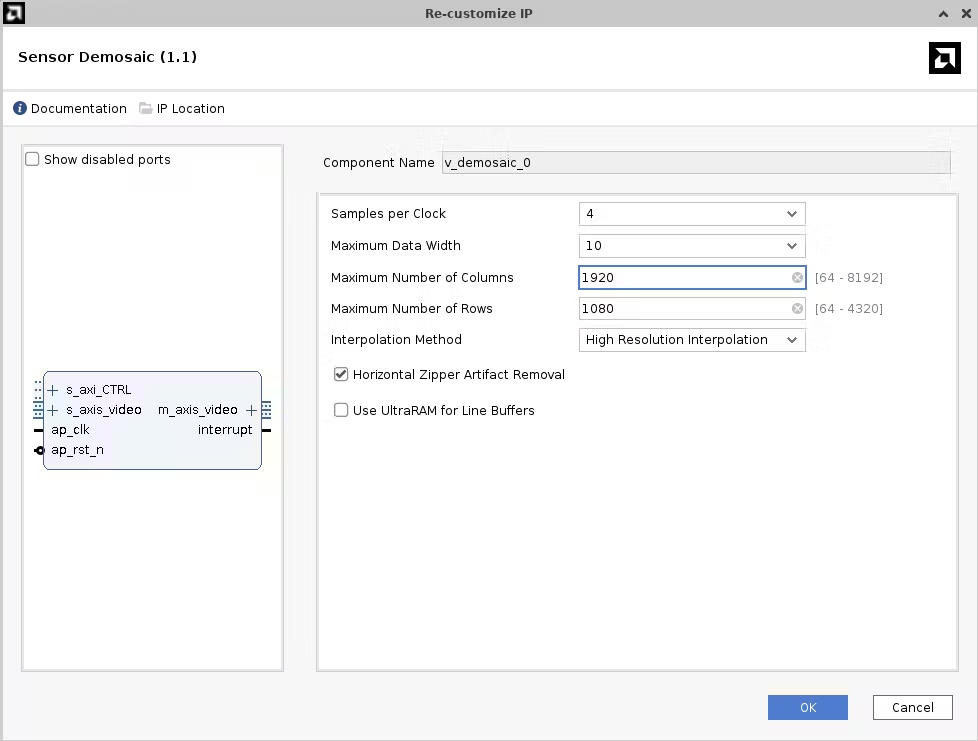

Demosaic(去马赛克)

→ 将图像传感器输出的 Bayer 模式像素数据转换为完整 RGB 图像,重建每个像素的颜色信息。

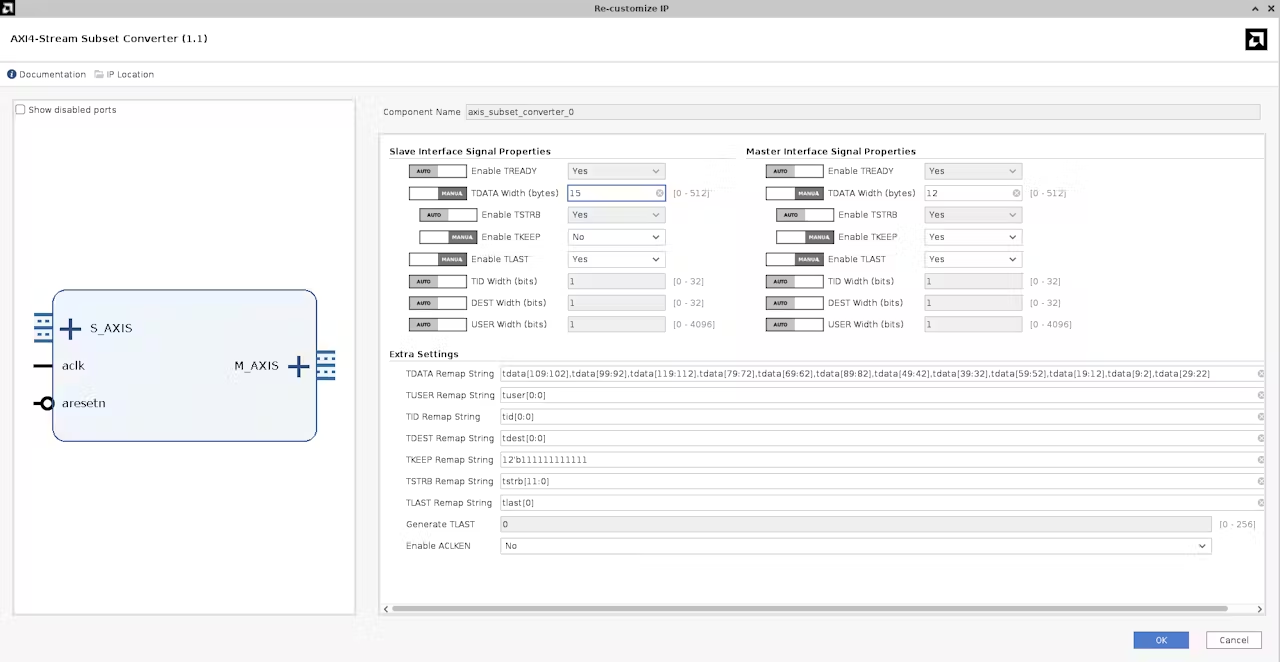

AXI Subset Converter

→ 将 40 位像素数据(每个 RGB 通道 10 位)转换为 24 位格式(每通道 8 位),每时钟周期保持 4 像素吞吐。

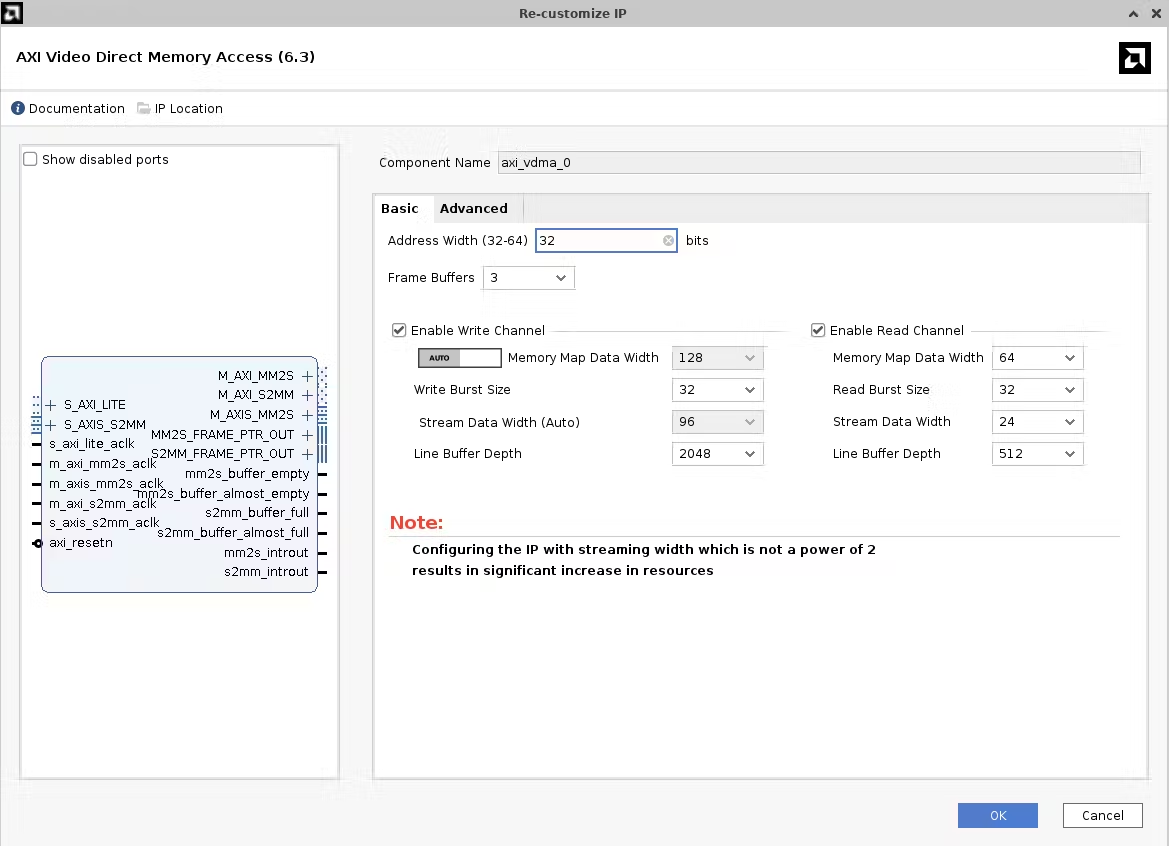

VDMA

→ 桥接 AXI4-Stream 与 AXI4 存储接口,在 NoC 上实现 DDR 帧存的存取,同时为处理阶段提供高效的缓存机制。

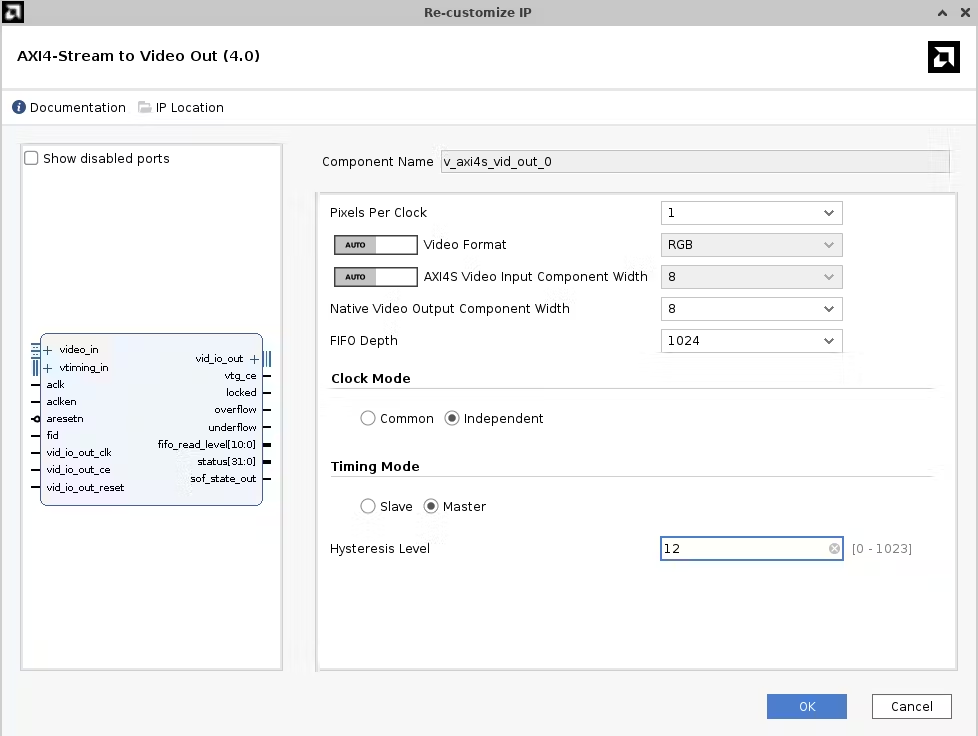

AXI4-Stream to Video Out

→ 将 AXI4-Stream 视频流转换为标准视频输出格式,生成 HSync、VSync 等同步信号以驱动显示设备。

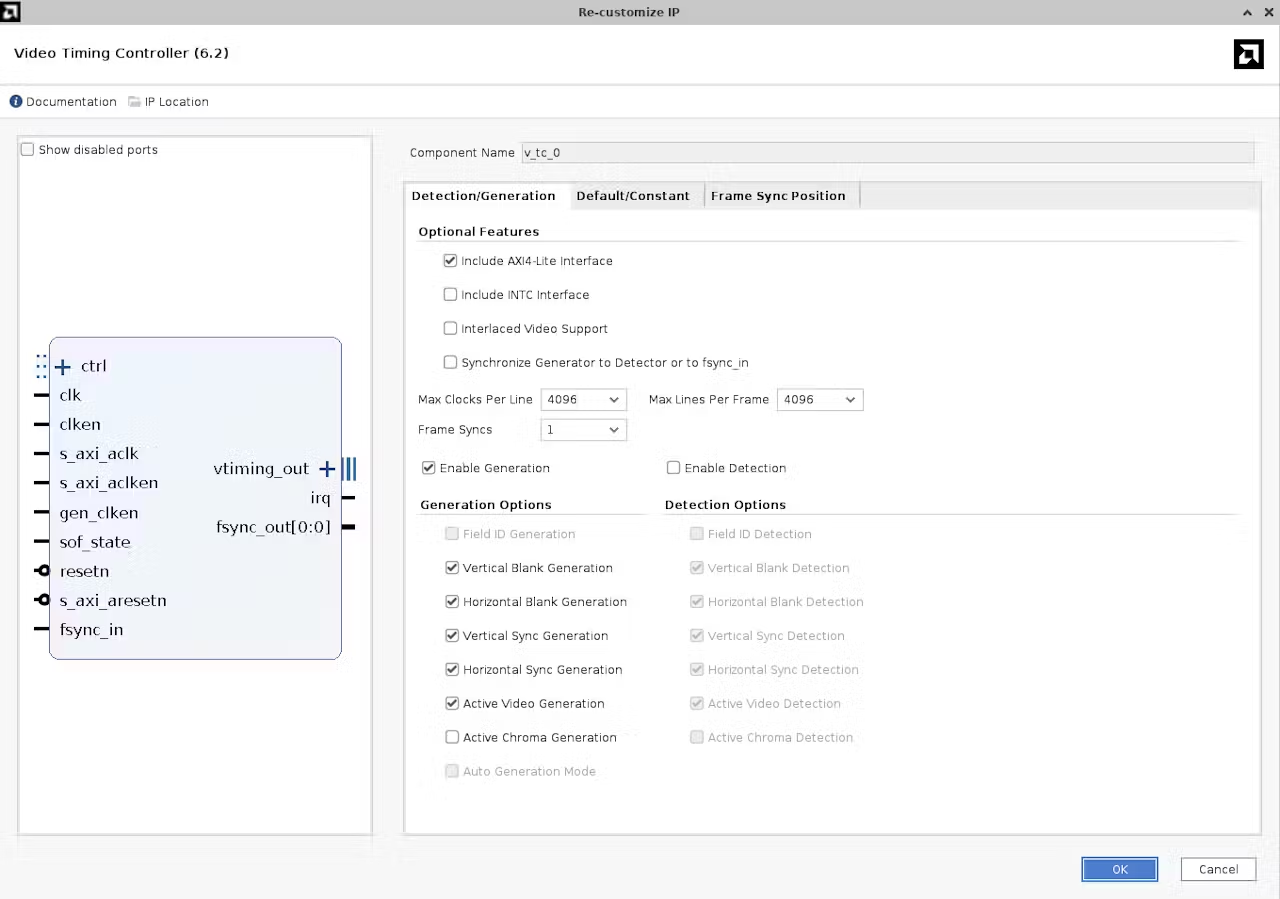

VTC

→ 生成 HSync、VSync、有效视频等信号,并与AXI4-Stream to Video Out模块同步,确保显示时序正确。

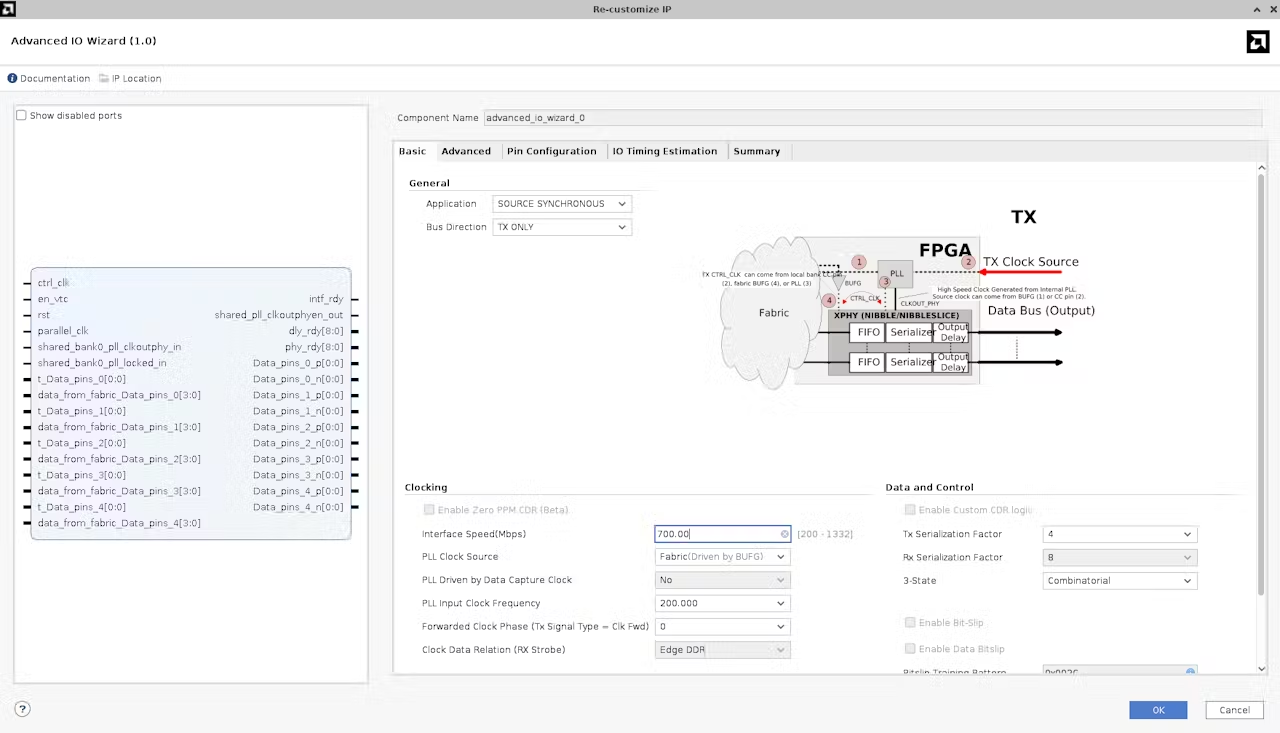

LCD LVDS 接口

→ 将标准并行视频输出信号转换为串行 VESA LVDS 格式,适配基于 LVDS 的 LCD 显示屏。

Advanced IO Wizard

→ 配置 Versal 设备中的 XPIO,将 LVDS 输出数据串行化,满足 VESA LVDS 显示标准。

通过这些 ILA,我们能够同时观察静态的状态信号与动态的高带宽数据流,全面掌控图像处理系统的运行状态。

完整设计如图所示,可通过本项目所附的 TCL 脚本复现该设计。

在生成比特流时,必须定义 XDC I/O 约束文件,明确所有外部接口的物理引脚位置与电气标准。

关键接口的引脚配置如下:

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property DIFF_TERM_ADV TERM_100 [get_ports sys_clk_p]

set_property PACKAGE_PIN A23 [get_ports {clkout1_p[0]}]

set_property IOSTANDARD LVDS15 [get_ports {clkout1_p[0]}]

set_property PACKAGE_PIN F22 [get_ports {dataout1_p_0[0]}]

set_property PACKAGE_PIN A20 [get_ports {dataout1_p_1[0]}]

set_property PACKAGE_PIN C22 [get_ports {dataout1_p_2[0]}]

set_property PACKAGE_PIN A25 [get_ports {dataout1_p_3[0]}]

set_property IOSTANDARD LVDS15 [get_ports {dataout1_p_*[0]}]

set_property PACKAGE_PIN E24 [get_ports {lcd_en}]

set_property IOSTANDARD LVCMOS15 [get_ports {lcd_en}]

set_property PACKAGE_PIN D24 [get_ports {lcd_sync}]

set_property IOSTANDARD LVCMOS15 [get_ports {lcd_sync}]

set_property PACKAGE_PIN AC11 [get_ports {DDR4_act_n[0]}]

set_property PACKAGE_PIN AB12 [get_ports {DDR4_adr[0]}]

set_property PACKAGE_PIN AB17 [get_ports {DDR4_adr[10]}]

set_property PACKAGE_PIN AE13 [get_ports {DDR4_adr[11]}]

set_property PACKAGE_PIN AH12 [get_ports {DDR4_adr[12]}]

set_property PACKAGE_PIN AD15 [get_ports {DDR4_adr[13]}]

set_property PACKAGE_PIN AD21 [get_ports {DDR4_adr[14]}]

set_property PACKAGE_PIN AD17 [get_ports {DDR4_adr[15]}]

set_property PACKAGE_PIN AC13 [get_ports {DDR4_adr[16]}]

set_property PACKAGE_PIN AE22 [get_ports {DDR4_adr[1]}]

set_property PACKAGE_PIN AD22 [get_ports {DDR4_adr[2]}]

set_property PACKAGE_PIN AB15 [get_ports {DDR4_adr[3]}]

set_property PACKAGE_PIN AD12 [get_ports {DDR4_adr[4]}]

set_property PACKAGE_PIN AE17 [get_ports {DDR4_adr[5]}]

set_property PACKAGE_PIN AD16 [get_ports {DDR4_adr[6]}]

set_property PACKAGE_PIN AG11 [get_ports {DDR4_adr[7]}]

set_property PACKAGE_PIN AE14 [get_ports {DDR4_adr[8]}]

set_property PACKAGE_PIN AB14 [get_ports {DDR4_adr[9]}]

set_property PACKAGE_PIN AC16 [get_ports {DDR4_ba[0]}]

set_property PACKAGE_PIN AD11 [get_ports {DDR4_ba[1]}]

set_property PACKAGE_PIN AB18 [get_ports {DDR4_bg[0]}]

set_property PACKAGE_PIN AC19 [get_ports {DDR4_ck_t[0]}]

set_property PACKAGE_PIN AD19 [get_ports {DDR4_ck_c[0]}]

set_property PACKAGE_PIN AB21 [get_ports {DDR4_cke[0]}]

set_property PACKAGE_PIN AC17 [get_ports {DDR4_cs_n[0]}]

set_property PACKAGE_PIN AG12 [get_ports {DDR4_dm_n[0]}]

set_property PACKAGE_PIN AH13 [get_ports {DDR4_dm_n[1]}]

set_property PACKAGE_PIN AE28 [get_ports {DDR4_dm_n[2]}]

set_property PACKAGE_PIN AD24 [get_ports {DDR4_dm_n[3]}]

set_property PACKAGE_PIN V22 [get_ports {DDR4_dm_n[4]}]

set_property PACKAGE_PIN V28 [get_ports {DDR4_dm_n[5]}]

set_property PACKAGE_PIN N28 [get_ports {DDR4_dm_n[6]}]

set_property PACKAGE_PIN U25 [get_ports {DDR4_dm_n[7]}]

set_property PACKAGE_PIN AF14 [get_ports {DDR4_dq[0]}]

set_property PACKAGE_PIN AH18 [get_ports {DDR4_dq[10]}]

set_property PACKAGE_PIN AH20 [get_ports {DDR4_dq[11]}]

set_property PACKAGE_PIN AH14 [get_ports {DDR4_dq[12]}]

set_property PACKAGE_PIN AH22 [get_ports {DDR4_dq[13]}]

set_property PACKAGE_PIN AH15 [get_ports {DDR4_dq[14]}]

set_property PACKAGE_PIN AG22 [get_ports {DDR4_dq[15]}]

set_property PACKAGE_PIN AF26 [get_ports {DDR4_dq[16]}]

set_property PACKAGE_PIN AE26 [get_ports {DDR4_dq[17]}]

set_property PACKAGE_PIN AH27 [get_ports {DDR4_dq[18]}]

set_property PACKAGE_PIN AE27 [get_ports {DDR4_dq[19]}]

set_property PACKAGE_PIN AG18 [get_ports {DDR4_dq[1]}]

set_property PACKAGE_PIN AG27 [get_ports {DDR4_dq[20]}]

set_property PACKAGE_PIN AD26 [get_ports {DDR4_dq[21]}]

set_property PACKAGE_PIN AG26 [get_ports {DDR4_dq[22]}]

set_property PACKAGE_PIN AG28 [get_ports {DDR4_dq[23]}]

set_property PACKAGE_PIN AE24 [get_ports {DDR4_dq[24]}]

set_property PACKAGE_PIN AD25 [get_ports {DDR4_dq[25]}]

set_property PACKAGE_PIN AH24 [get_ports {DDR4_dq[26]}]

set_property PACKAGE_PIN AF25 [get_ports {DDR4_dq[27]}]

set_property PACKAGE_PIN AG23 [get_ports {DDR4_dq[28]}]

set_property PACKAGE_PIN AG25 [get_ports {DDR4_dq[29]}]

set_property PACKAGE_PIN AG15 [get_ports {DDR4_dq[2]}]

set_property PACKAGE_PIN AH23 [get_ports {DDR4_dq[30]}]

set_property PACKAGE_PIN AH25 [get_ports {DDR4_dq[31]}]

set_property PACKAGE_PIN Y22 [get_ports {DDR4_dq[32]}]

set_property PACKAGE_PIN V23 [get_ports {DDR4_dq[33]}]

set_property PACKAGE_PIN Y23 [get_ports {DDR4_dq[34]}]

set_property PACKAGE_PIN W24 [get_ports {DDR4_dq[35]}]

set_property PACKAGE_PIN AA22 [get_ports {DDR4_dq[36]}]

set_property PACKAGE_PIN V24 [get_ports {DDR4_dq[37]}]

set_property PACKAGE_PIN AA21 [get_ports {DDR4_dq[38]}]

set_property PACKAGE_PIN W25 [get_ports {DDR4_dq[39]}]

set_property PACKAGE_PIN AF18 [get_ports {DDR4_dq[3]}]

set_property PACKAGE_PIN V25 [get_ports {DDR4_dq[40]}]

set_property PACKAGE_PIN W27 [get_ports {DDR4_dq[41]}]

set_property PACKAGE_PIN AA28 [get_ports {DDR4_dq[42]}]

set_property PACKAGE_PIN W26 [get_ports {DDR4_dq[43]}]

set_property PACKAGE_PIN Y26 [get_ports {DDR4_dq[44]}]

set_property PACKAGE_PIN AA26 [get_ports {DDR4_dq[45]}]

set_property PACKAGE_PIN AB28 [get_ports {DDR4_dq[46]}]

set_property PACKAGE_PIN AB26 [get_ports {DDR4_dq[47]}]

set_property PACKAGE_PIN P27 [get_ports {DDR4_dq[48]}]

set_property PACKAGE_PIN K27 [get_ports {DDR4_dq[49]}]

set_property PACKAGE_PIN AF13 [get_ports {DDR4_dq[4]}]

set_property PACKAGE_PIN R28 [get_ports {DDR4_dq[50]}]

set_property PACKAGE_PIN L28 [get_ports {DDR4_dq[51]}]

set_property PACKAGE_PIN R27 [get_ports {DDR4_dq[52]}]

set_property PACKAGE_PIN K28 [get_ports {DDR4_dq[53]}]

set_property PACKAGE_PIN T28 [get_ports {DDR4_dq[54]}]

set_property PACKAGE_PIN M27 [get_ports {DDR4_dq[55]}]

set_property PACKAGE_PIN P25 [get_ports {DDR4_dq[56]}]

set_property PACKAGE_PIN L26 [get_ports {DDR4_dq[57]}]

set_property PACKAGE_PIN R26 [get_ports {DDR4_dq[58]}]

set_property PACKAGE_PIN M26 [get_ports {DDR4_dq[59]}]

set_property PACKAGE_PIN AF19 [get_ports {DDR4_dq[5]}]

set_property PACKAGE_PIN T25 [get_ports {DDR4_dq[60]}]

set_property PACKAGE_PIN K26 [get_ports {DDR4_dq[61]}]

set_property PACKAGE_PIN T26 [get_ports {DDR4_dq[62]}]

set_property PACKAGE_PIN J25 [get_ports {DDR4_dq[63]}]

set_property PACKAGE_PIN AG13 [get_ports {DDR4_dq[6]}]

set_property PACKAGE_PIN AE19 [get_ports {DDR4_dq[7]}]

set_property PACKAGE_PIN AH17 [get_ports {DDR4_dq[8]}]

set_property PACKAGE_PIN AG21 [get_ports {DDR4_dq[9]}]

set_property PACKAGE_PIN AG17 [get_ports {DDR4_dqs_t[0]}]

set_property PACKAGE_PIN AG16 [get_ports {DDR4_dqs_c[0]}]

set_property PACKAGE_PIN AG20 [get_ports {DDR4_dqs_t[1]}]

set_property PACKAGE_PIN AH19 [get_ports {DDR4_dqs_c[1]}]

set_property PACKAGE_PIN AC28 [get_ports {DDR4_dqs_t[2]}]

set_property PACKAGE_PIN AD27 [get_ports {DDR4_dqs_c[2]}]

set_property PACKAGE_PIN AF24 [get_ports {DDR4_dqs_t[3]}]

set_property PACKAGE_PIN AF23 [get_ports {DDR4_dqs_c[3]}]

set_property PACKAGE_PIN Y24 [get_ports {DDR4_dqs_t[4]}]

set_property PACKAGE_PIN AA23 [get_ports {DDR4_dqs_c[4]}]

set_property PACKAGE_PIN Y28 [get_ports {DDR4_dqs_t[5]}]

set_property PACKAGE_PIN Y27 [get_ports {DDR4_dqs_c[5]}]

set_property PACKAGE_PIN U27 [get_ports {DDR4_dqs_t[6]}]

set_property PACKAGE_PIN U28 [get_ports {DDR4_dqs_c[6]}]

set_property PACKAGE_PIN P26 [get_ports {DDR4_dqs_t[7]}]

set_property PACKAGE_PIN N27 [get_ports {DDR4_dqs_c[7]}]

set_property PACKAGE_PIN AC22 [get_ports {DDR4_odt[0]}]

set_property PACKAGE_PIN AC24 [get_ports {DDR4_reset_n[0]}]

set_property PACKAGE_PIN AB23 [get_ports {sys_clk_clk_p[0]}]

set_property PACKAGE_PIN AC23 [get_ports {sys_clk_clk_n[0]}]

set_property IOSTANDARD LVDS15 [get_ports {sys_clk_clk_n[0]}]

set_property IOSTANDARD LVDS15 [get_ports {sys_clk_clk_p[0]}]

create_clock -period 5.000 -name sys_clk -waveform {0.000 2.500} [get_ports {sys_clk_clk_p[0]}]

set_property PACKAGE_PIN G26 [get_ports {cam1_gpio[0]}]

set_property IOSTANDARD LVCMOS15 [get_ports {cam1_gpio[0]}]

set_property PULLUP true [get_ports {cam1_gpio[0]}]

set_property PACKAGE_PIN G27 [get_ports cam1_i2c_scl_io]

set_property PACKAGE_PIN F28 [get_ports cam1_i2c_sda_io]

set_property IOSTANDARD LVCMOS15 [get_ports cam1_i2c_scl_io]

set_property IOSTANDARD LVCMOS15 [get_ports cam1_i2c_sda_io]

set_property PULLUP true [get_ports cam1_i2c_scl_io]

set_property PULLUP true [get_ports cam1_i2c_sda_io]

set_property PACKAGE_PIN U23 [get_ports mipi_phy_if_0_clk_p]

set_property PACKAGE_PIN T23 [get_ports mipi_phy_if_0_data_p[0]]

set_property PACKAGE_PIN R23 [get_ports mipi_phy_if_0_data_p[1]]

set_property PACKAGE_PIN L23 [get_ports mipi_phy_if_0_data_p[2]]

set_property PACKAGE_PIN M22 [get_ports mipi_phy_if_0_data_p[3]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_clk_p]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_clk_n]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_p[0]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_n[0]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_p[1]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_n[1]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_p[2]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_n[2]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_p[3]]

set_property IOSTANDARD MIPI_DPHY [get_ports mipi_phy_if_0_data_n[3]]

set_property CLOCK_REGION X3Y0 [get_cells -hier -filter {name =~ *mipi_csi2_rx_subsyst_1/inst/phy/inst/inst/rxbyteclkhs_buf}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets -hier -filter {name =~ *mipi_csi2_rx_subsyst_0/inst/phy/inst/inst/*/inst/BANK_WRAPPER_INST0/fifo_wr_clk[0]}]应用软件配置

应用软件将基于 Vitis 统一软件平台进行开发,负责执行以下关键任务:

-

配置摄像头(借助 ALINX 提供的初始化文件)。

-

配置视频时序控制器(VTC),输出 720p 所需的同步信号。

-

配置 Demosaic IP,实现正确的颜色重建。

-

通过 GPIO 控制信号启动摄像头。

-

配置 VDMA 与 DDR 进行高效读写。

完整软件项目已上传至我的 GitHub,可供参考与复用。

#include <stdio.h>

#include "math.h"

#include <ctype.h>

#include <stdlib.h>

#include "xil_types.h"

#include "xil_cache.h"

#include "xparameters.h"

#include "xiicps.h"

#include "i2c/PS_i2c.h"

#include "demosaic/demosaic.h"

#include "cam_config.h"

#include "config.h"

#include "sleep.h"#include "xil_cache.h"#include "xgpiops.h"

#include "xscugic.h"

#include "vtc.h"

#include "xaxivdma.h"

#include "xaxivdma_i.h"//#include "ff.h"

/* ------------------------------------------------------------ */

/* Global Variables */

/* ------------------------------------------------------------ */#define LED_MIO 25

#define CAM1_EMIO 26

#define CAM2_EMIO 27XAxiVdma vdma;

XAxiVdma_DmaSetup vdmaDMA;

XAxiVdma_Config *vdmaConfig;XVtc Vtc_inst;//static int WriteError;int wr_index=0;

int rd_index=0;XIicPs ps_i2c0;

XIicPs ps_i2c1;

XGpioPs GPIO_PTR ;int PsGpioSetup() ;/** Framebuffers for video data*/u8 frameBuf0[1][DEMO_MAX_FRAME] __attribute__ ((aligned(4096)));

u8 *pFrames0; void InitVideoFmt(XIicPs *IicInstance,int w, int h)

{i2c_reg16_write(IicInstance, 0x36, 0x3808, (w>>8)&0xff);i2c_reg16_write(IicInstance, 0x36, 0x3809, (w>>0)&0xff);i2c_reg16_write(IicInstance, 0x36, 0x380a, (h>>8)&0xff);i2c_reg16_write(IicInstance, 0x36, 0x380b, (h>>0)&0xff);}void InitDisplay()

{Vtc_init(&Vtc_inst,VMODE_1280x720);}int main(void)

{int i;int Status;PsGpioSetup() ;for (i = 0; i < 1; i++) {pFrames0 = frameBuf0[i];}demosaic_init(XPAR_V_DEMOSAIC_0_BASEADDR,VIDEO_COLUMNS,VIDEO_ROWS);i2c_init(&ps_i2c0,100000);XGpioPs_WritePin(&GPIO_PTR, CAM1_EMIO, 1) ;usleep(500000);XGpioPs_WritePin(&GPIO_PTR, CAM1_EMIO, 0) ;usleep(500000);XGpioPs_WritePin(&GPIO_PTR, CAM1_EMIO, 1) ;usleep(500000);sensor_init(&ps_i2c0);InitVideoFmt(&ps_i2c0,VIDEO_COLUMNS,VIDEO_ROWS);InitDisplay();xil_printf("config done!\r\n");vdmaConfig = XAxiVdma_LookupConfig(XPAR_AXI_VDMA_0_BASEADDR);XAxiVdma_CfgInitialize(&vdma, vdmaConfig, vdmaConfig->BaseAddress);//video = VMODE_1280x720;vdmaDMA.FrameDelay = 0;vdmaDMA.EnableCircularBuf = 1;vdmaDMA.EnableSync = 0;vdmaDMA.PointNum = 0;vdmaDMA.EnableFrameCounter = 0;vdmaDMA.VertSizeInput = 720;vdmaDMA.HoriSizeInput = (1280)*3;vdmaDMA.FixedFrameStoreAddr = 0;vdmaDMA.FrameStoreStartAddr[0] = (u32) pFrames0[0];vdmaDMA.Stride = (1280)*3;XAxiVdma_DmaConfig(&vdma, XAXIVDMA_WRITE, &(vdmaDMA));XAxiVdma_DmaSetBufferAddr(&vdma, XAXIVDMA_WRITE,vdmaDMA.FrameStoreStartAddr);XAxiVdma_DmaConfig(&vdma, XAXIVDMA_READ, &(vdmaDMA));XAxiVdma_DmaSetBufferAddr(&vdma, XAXIVDMA_READ,vdmaDMA.FrameStoreStartAddr);XAxiVdma_DmaStart(&vdma, XAXIVDMA_WRITE);//Status = XAxiVdma_StartParking(&vdma, 0, XAXIVDMA_WRITE);XAxiVdma_DmaStart(&vdma, XAXIVDMA_READ);//XAxiVdma_StartParking(&vdma, 0, XAXIVDMA_READ);while(1){XGpioPs_WritePin(&GPIO_PTR, LED_MIO, 0) ;usleep(500000);XGpioPs_WritePin(&GPIO_PTR, LED_MIO, 1) ;usleep(500000);}return 0;

}int PsGpioSetup()

{XGpioPs_Config *GPIO_CONFIG ;int Status ;GPIO_CONFIG = XGpioPs_LookupConfig(XPAR_XGPIOPS_0_DEVICE_ID) ;Status = XGpioPs_CfgInitialize(&GPIO_PTR, GPIO_CONFIG, GPIO_CONFIG->BaseAddr) ;if (Status != XST_SUCCESS){return XST_FAILURE ;}XGpioPs_SetDirectionPin(&GPIO_PTR, LED_MIO, 1) ;XGpioPs_SetOutputEnablePin(&GPIO_PTR, LED_MIO, 1) ;return XST_SUCCESS ;

}ILA 验证

当系统软件运行时,我们可以借助 ILA 来验证图像处理流水线是否按预期工作。

这些 ILA 在系统优化与调试过程中也发挥着关键作用。

在 Vivado 硬件管理器中,每个 ILA 会被映射为一个数字编号,映射关系如下:

-

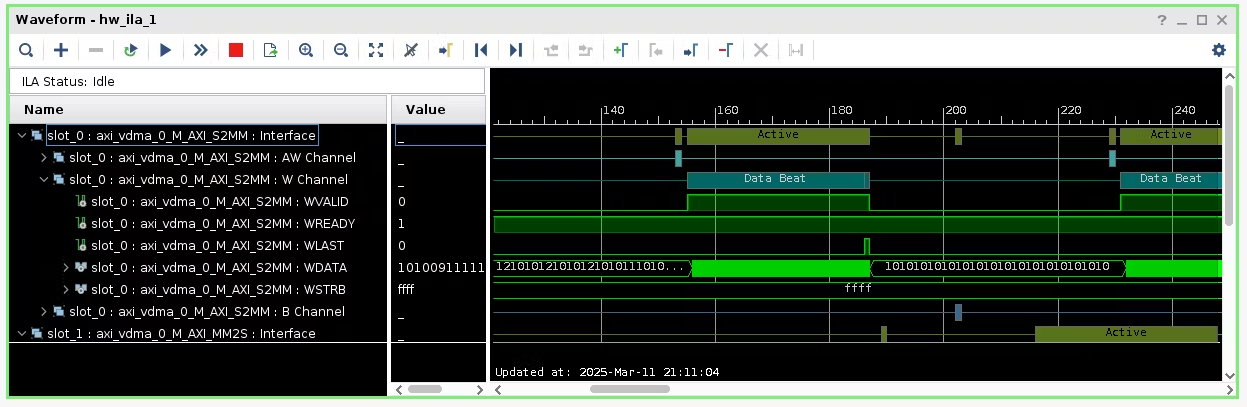

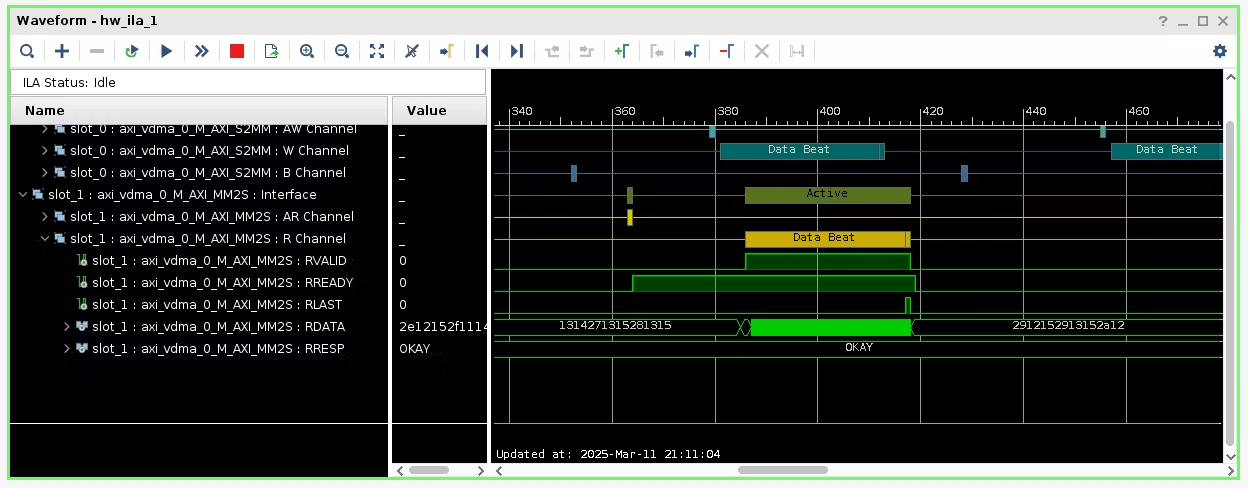

ILA1:Memory ILA

-

ILA2:Output ILA

-

ILA3:LCD LVDS ILA

-

ILA4:Video ILA

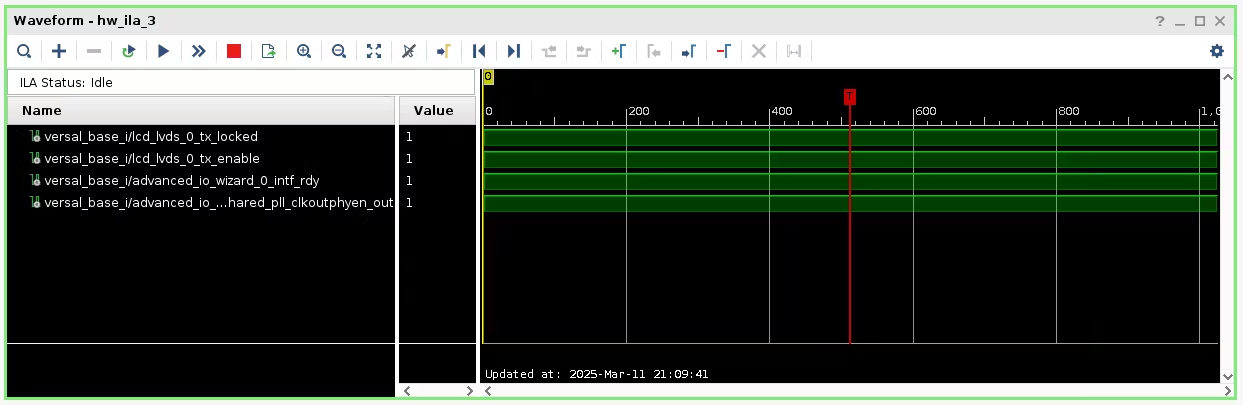

验证的第一步是监控 AXI4-Stream to Video Out 模块的状态信号。

该 IP 会输出多个指示信号,用于表征 AXI 视频流与视频时序信号是否同步。

如果输入的视频时序存在不匹配或不稳定的情况,该模块将无法锁定,导致视频无法输出。

由于该模块内部包含 FIFO 存储器,我们可以通过 ILA 观察其上溢和下溢状态信号。这些信号对于诊断流水线中的数据不足(data starvation)或背压(backpressure)等性能问题尤为重要,能够指导我们改进存储带宽或缓冲策略。

在 ILA1(即 Output ILA)上观察这些信号,可以看到包含视频数据的 AXI Stream 信号与视频时序控制器生成的时序信号已经保持同步。如果 AXI Stream 信号格式不匹配(例如视频格式不符),AXI4 Stream to Video Out 模块将无法完成同步锁定。

验证过程的下一步是检查 LCD LVDS 输出接口。该阶段的关键状态指示可以确认内部时钟是否锁定,以及接口是否成功启用向显示屏传输数据。监控这些信号,有助于确保序列化视频流被正确生成并传输至 LCD 面板,若出现时钟错误或链路未启用等问题,也能迅速定位。

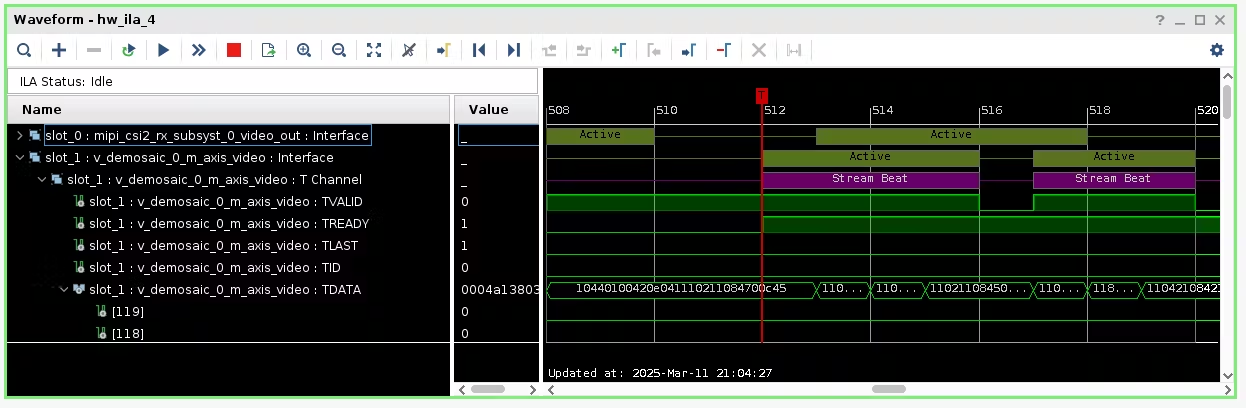

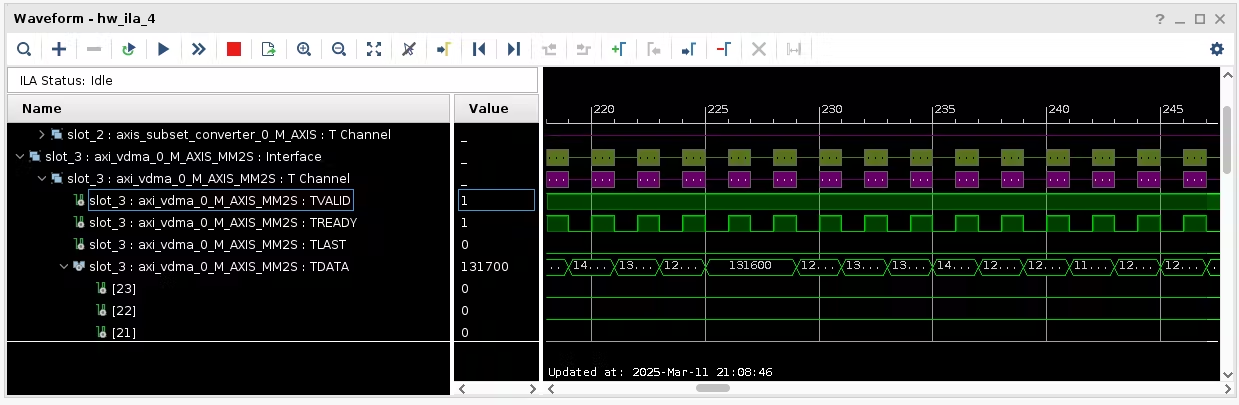

在验证图像处理通路本身时,首先要检查的是MIPI CSI-2 RX 子系统的视频输出。

在此阶段,我们应该观察到每个时钟周期输出 4 像素的 10 bit 原始数据。如果相机配置或 MIPI 接口存在问题,通常会在此处显现为无视频输出或格式异常。验证此输出有助于确认相机初始化是否正确以及 MIPI 链路是否正常建立。

MIPI CSI-2 RX 子系统的输出会送入Demosaic去马赛克模块,它会将 Bayer 格式的 10 位原始像素转换为 30 位 RGB 格式(每个颜色通道 10 位)。由于流水线保持每个时钟处理 4 像素的吞吐量,去马赛克模块输出的 AXI4-Stream 数据总宽度为 120 位(4 像素×30 位),在维持高吞吐量的同时提供完整重构的色彩数据。

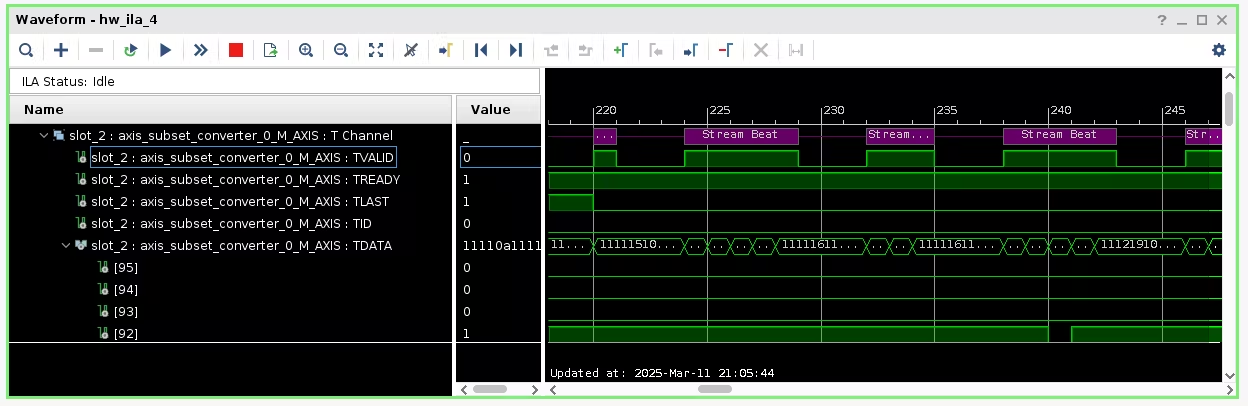

LCD 显示屏需要 24 位 RGB 像素(每个颜色通道 8 位)。为满足这一要求,AXI 子集转换器将每像素深度从 30 位压缩至 24 位。系统继续保持每个时钟处理 4 像素的速率,因此转换器输出总线宽度为 96 位(4 像素×24 位),与下游视频输出路径的格式要求完全匹配。

在写入路径上,我们可以观察到 AXI4 总线将处理后的视频帧写入 DDR 存储器的过程。这些传输由 VDMA 发起,它作为 AXI4-Stream 视频流水线与 AXI4 存储器映射接口的桥梁,通过片上网络(NoC)实现帧数据的高效存储。监控这一过程可确保帧缓冲正确写入存储器,供后续读取显示。

读取路径始于 VDMA 通过 NoC 发起 AXI4 读操作,从 DDR 存储器中获取视频帧。这些操作将存储的帧数据重新送回 AXI4-Stream 域,使其能在流水线中继续流向显示端。观察这些 AXI4 读操作可以确认存储器访问功能正常,且帧数据的获取与视频输出时序保持同步。

图像处理流水线的最后环节是 VDMA 输出的 AXI4-Stream 信号,该接口每个时钟周期传输 1 个像素。该数据流输入 AXI4-Stream to Video Out 模块,与时序信号同步后输出至显示端。这一环节标志着系统从基于内存的缓冲机制向实时视频输出的转换,至此,整个图像处理流程闭环完成。

通过观测上述所有 ILA 信号,我们能够深入了解图像处理流水线的内部运行状态,有效排查和定位可能出现的各类问题。

通常这些问题可追溯至软件配置错误或单个 IP 核模块参数设置不当——在早期系统搭建和集成阶段尤为常见。

当然,判断系统是否正常工作的最直观方式仍然是——屏幕上成功显示出图像。但当遇到异常情况时,ILA 提供的深层信号可见性将成为故障诊断的关键工具。

总结

在本项目中,我们探讨了如何在 Versal AI Edge 器件上构建基础的图像处理流水线并验证其功能。

无论是图像识别、智能驾驶,还是工业检测,只要有图像数据的地方,就离不开这条看不见的流水线。而我们今天所做的,就是让它“可见”。

通过利用 ChipScope 及 ILA,我们能够观察并验证设计中的关键点,确保每个阶段都按预期运行。这种实时可视化功能使我们能够快速有效地识别在集成或应用阶段系统可能出现的问题及其根本原因,使后续的开发过程变得更加顺畅、可靠。

芯驿电子自 2012 年成立以来,旗下 AUMO 与 ALINX 两大品牌,在智能车载与 FPGA 行业解决方案领域持续深耕。

ALINX 提供完整的用户开发手册和工具链与全备的技术支持,帮助您缩短从原型到量产的周期。欢迎访问 ALINX 官网了解更多详情。

原文:Using ChipScope to Debug AMD Versal Designs - Hackster.io

相关文章:

【ALINX 实战笔记】FPGA 大神 Adam Taylor 使用 ChipScope 调试 AMD Versal 设计

本篇文章来自 FPGA 大神、Ardiuvo & Hackster.IO 知名博主 Adam Taylor。在这里感谢 Adam Taylor 对 ALINX 产品的关注与使用。为了让文章更易阅读,我们在原文的基础上作了一些灵活的调整。原文链接已贴在文章底部,欢迎大家在评论区友好互动。 在上篇…...

【数据结构入门训练DAY-35】棋盘问题

本次训练聚焦于使用深度优先搜索(DFS)算法解决棋盘上的棋子摆放问题。题目要求在一个可能不规则的nn棋盘上摆放k个棋子,且任意两个棋子不能位于同一行或同一列。输入包括棋盘大小n和棋子数k,以及棋盘的形状(用#表示可放…...

深度学习中的损失函数优化技巧)

张 提示词优化(相似计算模式)深度学习中的损失函数优化技巧

失函数的解释 损失函数代码解析 loss = -F.log_softmax(logits[...

Elasticsearch 常用语法手册

🧰 Elasticsearch 常用语法手册 📚 目录 索引操作文档操作查询操作聚合查询健康与状态查看常见问题与注意事项 🔹 索引操作 查询全部索引 GET _search创建索引 PUT /es_db创建索引并设置分片数和副本数 PUT /es_db {"settings&quo…...

华宇TAS应用中间件与亿信华辰多款软件产品完成兼容互认证

近日,华宇TAS应用中间件与亿信华辰多款产品成功通过兼容互认证测试,双方产品在功能协同、性能优化及高可用性等维度实现全面适配,将为用户提供更加稳定、高效、安全的国产化解决方案。 此次认证也标志着华宇在国产化生态适配领域再添重要里程…...

AI大模型从0到1记录学习numpy pandas day24

第 1 章 环境搭建 1.1 Anaconda 1.1.1 什么是Anaconda Anaconda官网地址:https://www.anaconda.com/ 简单来说,Anaconda Python 包和环境管理器(Conda) 常用库 集成工具。它适合那些需要快速搭建数据科学或机器学习开发环境的用…...

开源GPU架构RISC-V VCIX的深度学习潜力测试:从RTL仿真到MNIST实战

点击 “AladdinEdu,同学们用得起的【H卡】算力平台”,H卡级别算力,按量计费,灵活弹性,顶级配置,学生专属优惠。 一、开篇:AI芯片架构演变的三重挑战 (引述TPUv4采用RISC-V的行业案…...

VirtualiSurg使用SenseGlove触觉手套开发XR手术培训体验

虚拟现实和虚拟现实触觉 作为一个领先的培训平台,VirtualiSurg自2017年以来一直利用扩展现实(XR)和触觉技术,为全球医疗保健行业提供个性化的数据驱动学习解决方案。它们使医疗专业人员能够协作学习和培训,提高他们的技能,让他们…...

AbstractErrorController简介-笔记

1. AbstractErrorController简介 org.springframework.boot.autoconfigure.web.servlet.error.AbstractErrorController 是 Spring Boot 提供的一个用于处理 HTTP 错误(如 404、500 等)的抽象类,用于自定义错误响应的逻辑。它是 Spring Boot…...

next.js实现项目搭建

一、创建 Next.js 项目的步骤 1、安装 npx create-next-applatest # 或 yarn create next-app # 或 pnpm create next-app 按照交互式提示配置你的项目: 输入项目名称 选择是否使用 TypeScript 选择是否启用 ESLint 选择是否启用 Tailwind CSS 选择是否使用 s…...

使用GoLang版MySQLDiff对比表结构

概述 下载地址: https://github.com/camry/mysqldiff/ 编译安装 git clone https://github.com/camry/mysqldiff.git go env -w GOPROXYhttps://goproxy.cn,direct go env -w GOPRIVATE*.corp.example.com go build .\mysqldiff.go执行对比 ./mysqldiff --sourc…...

git工具使用详细教程-------命令行和图形化工具

下载 git下载地址:https://git-scm.com/downloads TortoiseGit(图形化工具)下载地址:https://tortoisegit.org/download/ 认识git结构 工作区:存放代码的地方 暂存区:临时存储,将工作区的代码…...

失控的产品

大部分程序员很难有机会做一个新的产品,绝大多时候去一家新公司也都是在旧产品上修修补补。 笔者还是很幸运得到了开发新品的机会,从2023年开始做,中间经历了许多磕磕碰碰。 有的小伙伴从中离开,偶尔又加入1~2个人,但…...

区块链blog1__合作与信任

🍂我们的世界 🌿不是孤立的,而是网络化的 如果是单独孤立的系统,无需共识,而我们的社会是网络结构,即结点间不是孤立的 🌿网络化的原因 而目前并未发现这样的理想孤立系统,即现实中…...

)

ES常识9:如何实现同义词映射(搜索)

在 Elasticsearch(ES)中实现同义词映射(如“美丽”和“漂亮”),核心是通过 同义词过滤器(Synonym Token Filter) 在分词阶段将同义词扩展或替换为统一词项,从而让搜索时输入任意一个…...

aws 实践创建policy + Role

今天Cyber 通过image 来创建EC2 的时候,要添加policy, 虽然是administrator 的role, 参考Cyber 提供的link: Imageshttps://docs.cyberark.com/pam-self-hosted/14.2/en/content/pas%20cloud/images.htm#Bring 1 Step1:...

兰亭妙微B端UI设计:融合多元风格,点亮品牌魅力

在B端产品市场,独特的品牌形象是企业脱颖而出的关键。兰亭妙微专注于B端UI设计,通过融合多元风格,为企业点亮品牌魅力,助力品牌价值提升。 兰亭妙微主创团队源自清华,历经多年沉淀,积累了丰富的设计经验。…...

高项-逻辑数据模型

逻辑数据模型的核心理解 1. 定义与特点 逻辑数据模型(Logical Data Model, LDM): 是一种抽象的数据结构设计,用于描述业务实体(如客户、订单)及其关系(如“客户下单”),…...

Aquatone安装与使用

前言:aquatone工具获取网页截图,在资产收集的时候,对于网站可以起到快速浏览 michenriksen/aquatone: A Tool for Domain Flyovershttps://github.com/michenriksen/aquatone 任务一 安装chromium sudo apt install chromiumchromium -h 任务二 下载aquatone Relea…...

解读RTOS 第八篇 · 内核源码解读:以 FreeRTOS 为例

1. 引言 FreeRTOS 作为最流行的嵌入式实时操作系统之一,其内核源码简洁且功能完善。通过剖析其关键模块(任务管理、调度器、队列、内存管理和移植层),不仅能够更深入地理解 RTOS 的运行机制,还能掌握根据项目需求进行内核定制与优化的能力。本章将带你以 FreeRTOS 10.x 版…...

6、登录功能后端开发

6、登录功能后端开发 https://xiaoxueblog.com/ai/%E7%99%BB%E5%BD%95%E5%8A%9F%E8%83%BD%E5%90%8E%E7%AB%AF%E5%BC%80%E5%8F%91.html 1、新建用户表SQL脚本 -- CREATE DATABASE aicloud CHARACTER SET utf8mb4 COLLATE utf8mb4_general_ci;-- 创建用户表 drop table if exi…...

「彻底卸载 Quay 容器仓库」:干净移除服务、镜像与配置的全流程指南

文章目录 🧹 第一步:停止并禁用 systemd 服务🚮 第二步:移除 Podman 容器与相关资源1. 删除 quay-app 容器2. 删除镜像(如果你想彻底清理)3. 删除挂载卷(比如 SQLite 存储) …...

String(上)介绍STL与String的关系,为什么有string类,String有什么用)

C++从入门到实战(十五)String(上)介绍STL与String的关系,为什么有string类,String有什么用

C从入门到实战(十五)String(上) 前言一、STL与String的关系1. STL 是什么?2. String 是什么?3. String 与 STL 的关系 二、为什么有string类,有什么用1. 为什么需要 string 类?2. st…...

【Python 正则表达式】

Python 正则表达式通过 re 模块实现模式匹配,是文本处理的核心工具。以下是系统化指南,包含语法详解和实战案例: 一、正则基础语法 1. 元字符速查表 符号含义示例匹配结果.任意字符(除换行符)r"a.c"“abc”…...

数据库设计)

【MySQL】第四弹——表的CRUD进阶(二)数据库设计

文章目录 🌟范式🌟表的设计💫第一范式 1NF🪐反例🪐正例 💫第二范式 2NF🪐反例🪐正例 💫第三范式 3NF🪐反例🪐正例 💫表的设计方法&…...

核心系统——音效系统)

Unity基础学习(十五)核心系统——音效系统

目录 一、关于音频文件的导入相关 二、音频源组件Audio Source 三、Audio Listener的介绍 四、关于播放音乐的方式 五、麦克风输入相关 Microphone 类方法与属性总览 1. Start 方法 2. End 方法 3. IsRecording 方法 4. GetPosition 方法 5. devic…...

计算机视觉----常见卷积汇总

普通卷积 普通卷积大家应该都比较熟悉了,如果不熟悉的话,可以参考我之前的博客,或者去网上自行百度。这里主要想补充两个知识点。一:卷积核参数量怎么算? 二:如何高效的并行运算卷积滑窗? …...

【人工智能-agent】--Dify+Mysql+Echarts搭建了一个能“听懂”人话的数据可视化助手!

Echarts官网:https://echarts.apache.org/zh/index.html ECharts 是一个由百度团队开发的、基于 JavaScript 的开源可视化图表库,它提供了丰富的图表类型和强大的交互功能,能够帮助开发者轻松创建专业级的数据可视化应用。 核心特点 丰富的图…...

【专栏启动】开篇:为什么是 Django + Vue3?测试平台的技术选型与架构蓝图

【专栏启动】开篇:为什么是 Django Vue3?测试平台的技术选型与架构蓝图 前言一、为什么是 Django Vue3?二、测试平台的架构设计蓝图三、测试平台模块功能概述 结语 前言 一个高效、稳定、易用的测试平台,不仅能够帮助团队提升测…...

Rust 学习笔记:关于 Vector 的练习题

Rust 学习笔记:关于 Vector 的练习题 Rust 学习笔记:关于 Vector 的练习题哪个调用会报错?以下代码能否通过编译?若能,输出是?以下代码能否通过编译?若能,输出是?以下代码…...

Modbus TCP转Profinet网关:数字化工厂异构网络融合的核心枢纽

在现代工业生产中,随着智能制造和工业互联网的不断发展,数字化工厂成为了制造业升级的重要方向。数字化工厂的核心在于实现设备、数据和人的互联互通,而这其中,通信协议扮演着至关重要的角色。今天,我们就来探讨开疆智…...

:从客户访谈评分到市场规模估算——移情阶段的实战进阶)

精益数据分析(62/126):从客户访谈评分到市场规模估算——移情阶段的实战进阶

精益数据分析(62/126):从客户访谈评分到市场规模估算——移情阶段的实战进阶 在创业的移情阶段,科学评估用户需求与市场潜力是决定产品方向的关键。今天,我们结合Cloud9 IDE的实战经验与《精益数据分析》的方法论&…...

各类开发教程资料推荐,Java / python /golang /js等

更多资源在文末👇👇👇👇👇👇👇👇👇 1. 入门首选(易学且应用广) Python 特点:语法简洁、易读,社区资源丰富。 用途&#…...

现代健康养生小贴士

在忙碌的现代生活中,掌握一些简单实用的健康养生技巧,能轻松为身体 “充电”,提升生活质量。以下从饮食、运动、作息等方面,为你带来科学易执行的养生建议。 一、饮食:吃对食物,为健康加分 早餐要吃好&am…...

)

每日一道leetcode(新学数据结构版)

208. 实现 Trie (前缀树) - 力扣(LeetCode) 题目 Trie(发音类似 "try")或者说 前缀树 是一种树形数据结构,用于高效地存储和检索字符串数据集中的键。这一数据结构有相当多的应用情景,例如自动…...

ChromaDB 向量库优化技巧实战

chroma 一步步使用 安装 # 安装chromadb pip install chromadb,sentence_transformers# 不启动服务会出现sock.connect(sa)TimeoutError: timed out chroma run服务启动后,您将看到类似以下输出: 建立连接 部署完成后,需要建立与Chroma服…...

)

全国各地区经纬度数据(包含省、市、县)

全国各地区经纬度数据(包含省、市、县) 1、指标:行政区划代码、省份、城市、经度、纬度 2、来源:高德地图 3、用途:可用于空间相关研究 4、下载链接: 全国各地区经纬度数据(包含省、市、县…...

记录一下seata后端数据库由mariadb10切换到mysql8遇到的SQLException问题

文章目录 前言一、问题记录二、参考帖子三、记录store.db.driverClassName 前言 记录一下seata后端数据库由mariadb10切换到mysql8遇到的SQLException问题。 一、问题记录 17:39:23.709 ERROR --- [ionPool-Create-1134013833] com.alibaba.druid.pool.DruidDataSource : …...

【Python 面向对象】

Python 的面向对象编程(OOP)通过类(Class)和对象(Object)实现代码结构化,支持封装、继承和多态三大特性。以下是系统化指南: 一、类与对象基础 1. 定义类 class Dog:# 类属性&…...

软考软件评测师——计算机组成与体系结构

目录 计算机寻址方式详解与对比分析 一、立即寻址 二、直接寻址 三、间接寻址 四、寄存器寻址 五、寄存器间接寻址 六、变址寻址 七、基址寻址 八、相对寻址 九、综合对比分析 计算机寻址方式详解与对比分析 一、立即寻址 核心概念 指令操作码后直接携带操作数值&a…...

宝元LNC数控数据采集方式、跨平台采集通讯方案介绍

文章目录 采集效果图通讯方案介绍技术名词解释技术细节小结 采集效果图 通讯方案介绍 老版本宝元:必须走TCP通讯,如LNC568A系列 今天主要介绍新版本的宝元,如采用M6800控制器的5800系列系统等 新版本宝元通讯方式: ①sdk通讯&…...

ZFile与Cpolar技术结合实现远程数据实时访问与集中管理的可行性分析

文章目录 前言1.关于ZFile2.本地部署ZFile3.ZFile本地访问测试4.ZFile的配置5.cpolar内网穿透工具安装6.创建远程连接公网地址7.固定ZFile公网地址 前言 在信息爆炸的年代,每个现代人都在数字浪潮中扮演着独特的角色。不论是商务精英、影像创作者还是学术达人&…...

JS手写代码篇---手写 Object.create

JS手写代码篇 在做手写题的时候,我们要思考两个问题 这个代码的作用是什么能够实现的效果是什么样子 1. 手写 Object.create 思路:创造一个对象,类似于Object.create()方法>将obj作为原型 // 手写 Object.create function create (ob…...

homeassistant安装

这里写自定义目录标题 homeassistant安装(windows)安装virtual boxhaos下载haos安装docker镜像地址更换安装File editor安装hacs安装Xiaomi Miot Auto问题排查 homeassistant安装(windows) 安装virtual box 百度搜索virtual box…...

Pythonnet - 实现.NET Core和Python进行混合编程

1 安装Pythonnet包 2...

C++23 新特性:ranges::contains 与 ranges::contains_subrange

文章目录 ranges::containsranges::contains_subrange编译器支持总结 C23 标准带来了许多令人兴奋的新特性,其中就包括了 ranges::contains 和 ranges::contains_subrange 这两个算法。这两个算法由提案 P2302R4 提出,它们为 C 程序员提供了更加丰富和…...

超市管理系统 (正式版)(指针)(数据结构)(清屏操作)(文件读写))

(C语言)超市管理系统 (正式版)(指针)(数据结构)(清屏操作)(文件读写)

目录 前言: 源代码: product.h product.c fileio.h fileio.c main.c 代码解析: 一、程序结构概述 二、product.c 函数详解 1. 初始化商品列表 Init_products 2. 添加商品 add_product 3. 显示商品 display_products 4. 修改商品 mo…...

Framebuffer显示bmp图片

代码: /* 标准输入输出头文件,提供文件操作和输入输出函数(如printf)*/ #include <stdio.h>/* 文件控制操作头文件,提供文件打开模式(如O_RDWR)和文件控制函数 */ #include <fcntl.h&…...

常用负载均衡技术有哪些?不同网络层面上的网络负载均衡技术

前言 负载均衡是一种策略,它能让多台服务器或多条链路共同承担一些繁重的计算或I/O任务,从而以较低成本消除网络瓶颈,提高网络的灵活性和可靠性。 在系统管理员发现网络性能不好时,可以通过网络负载均衡来分配资源,以…...

由于复制槽导致wal大量堆积的处理方案

文章目录 环境症状问题原因解决方案 环境 系统平台:N/A 版本:N/A 症状 数据库中的pg_wal占用大量空间,且不删除。 问题原因 复制槽占用早期的wal日志,导致wal归档后无法正常删除。 1. 排查复制槽情况: highgo# …...