FPGA系列之DDS信号发生器设计(DE2-115开发板)

一、IP核

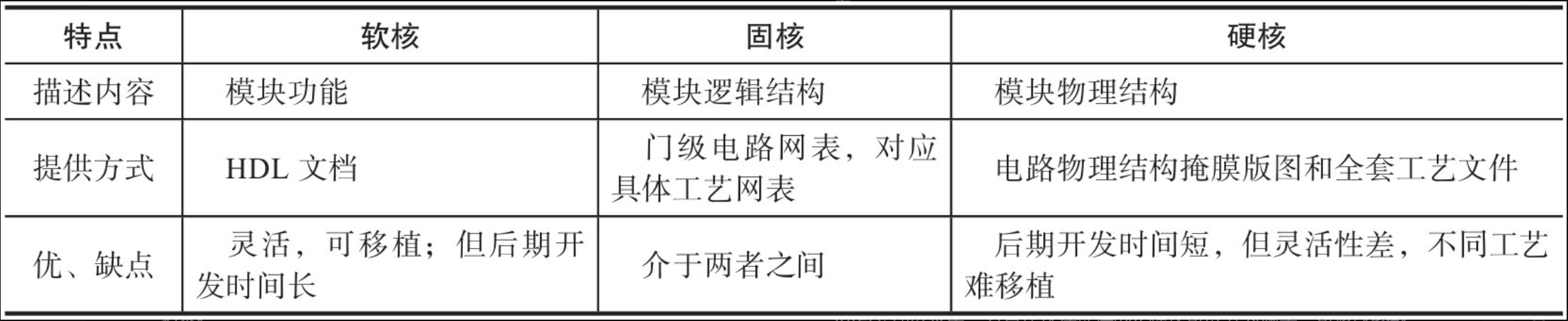

IP(Intellectual Property)原指知识产权、著作权等,在IC设计领域通常被理解为实现某种功能的设计。IP模块则是完成某种比较复杂算法或功能(如FIR滤波器、FFT、SDRAM控制器、PCIe接口、CPU核等)并且参数可修改的电路模块,又称为IP核(IP Core)。随着CPLD/FPGA器件的集成度越来越高,设计越来越复杂,使用IP核是EDA设计的发展趋势。根据实现方式的不同,IP核可以分为软核(soft core)、固核(firm core)和硬核(hard core)。

Intel公司以及第三方合作伙伴提供的IP模块可以分为两类:可修改参数的IP核(Library of Parameterized Modules, LPM)和需要授权才能在生产设计中使用的IP核(功能更复杂的模块,也称为MegaCore)。这些模块专门针对不同的器件结构进行了优化,在设计数字系统时,我们可以充分利用这些IP模块,加快设计进度,同时提高器件资源的利用率。

注:该内容引用自Verilog HDL与FGPGA数字系统设计(第二版)

二、DDS信号发生器设计

1.DDS信号发生器

(1)概念

直接数字频率合成(Direct Digital Frequency Synthesis,简称DDS或DDFS)是一种应用数字技术产生信号波形的方法,它是由美国学者J. Tierncy、C.M. Rader和B. Gold在1971年提出的,他们以数字信号处理理论为基础,从相位概念出发提出了一种新的直接合成所需波形的全数字频率合成方法。

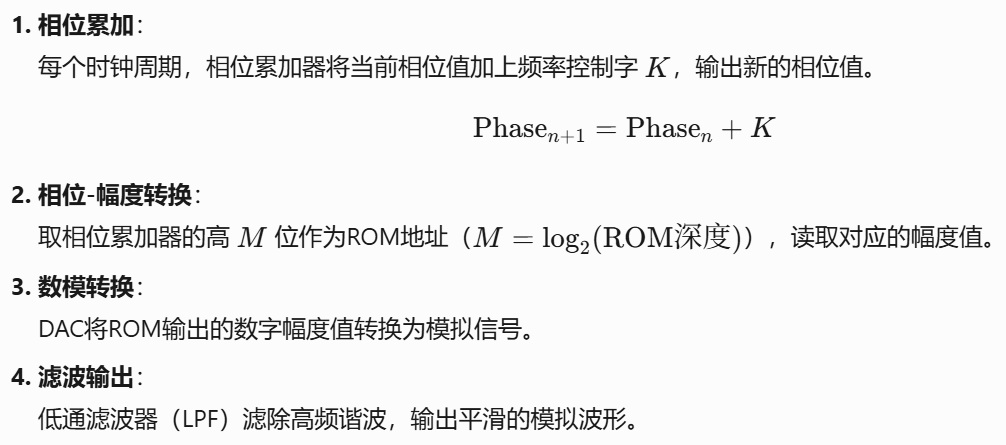

DDS系统通常包含以下模块:

相位累加器(Phase Accumulator)

波形查找表(Waveform ROM/LUT)

数模转换器(DAC)

抗混叠滤波器(Anti-Aliasing Filter)

(2)DDS工作流程

2. DDS信号发生器设计

使用Quartus Prime Lite创建工程,顶层文件名为DDS_top,芯片选择EP4CE115F29C7(详细步骤看其余FPGA文章)。

(1)相位累加器的设计

新建Verilog HDL File文件,文件名为addr_cnt.v(如果与VS Code连用代码写好后另存为就好)

//=====相位累加器和数据锁存器=====

module addr_cnt(CPi,K,ROMaddr,Address);input CPi; //系统基准时钟(100MHz)input [12:0] K; //13位频率控制字output reg [9:0] ROMaddr; //10位ROM地址output reg [16:0] Address; //17位相位累加器地址信号always @(posedge CPi)beginAddress = Address + K;ROMaddr = Address[16:7];end

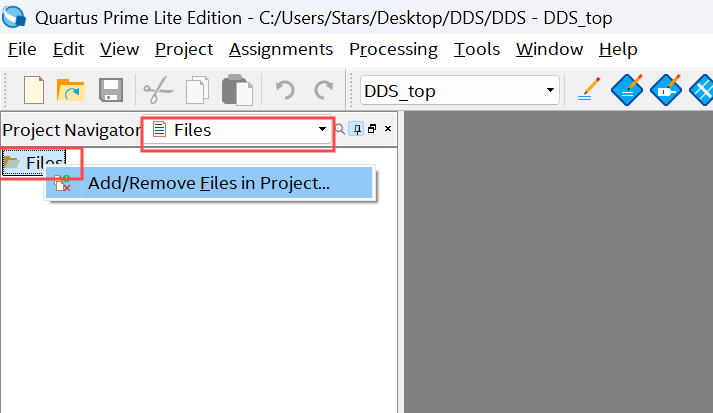

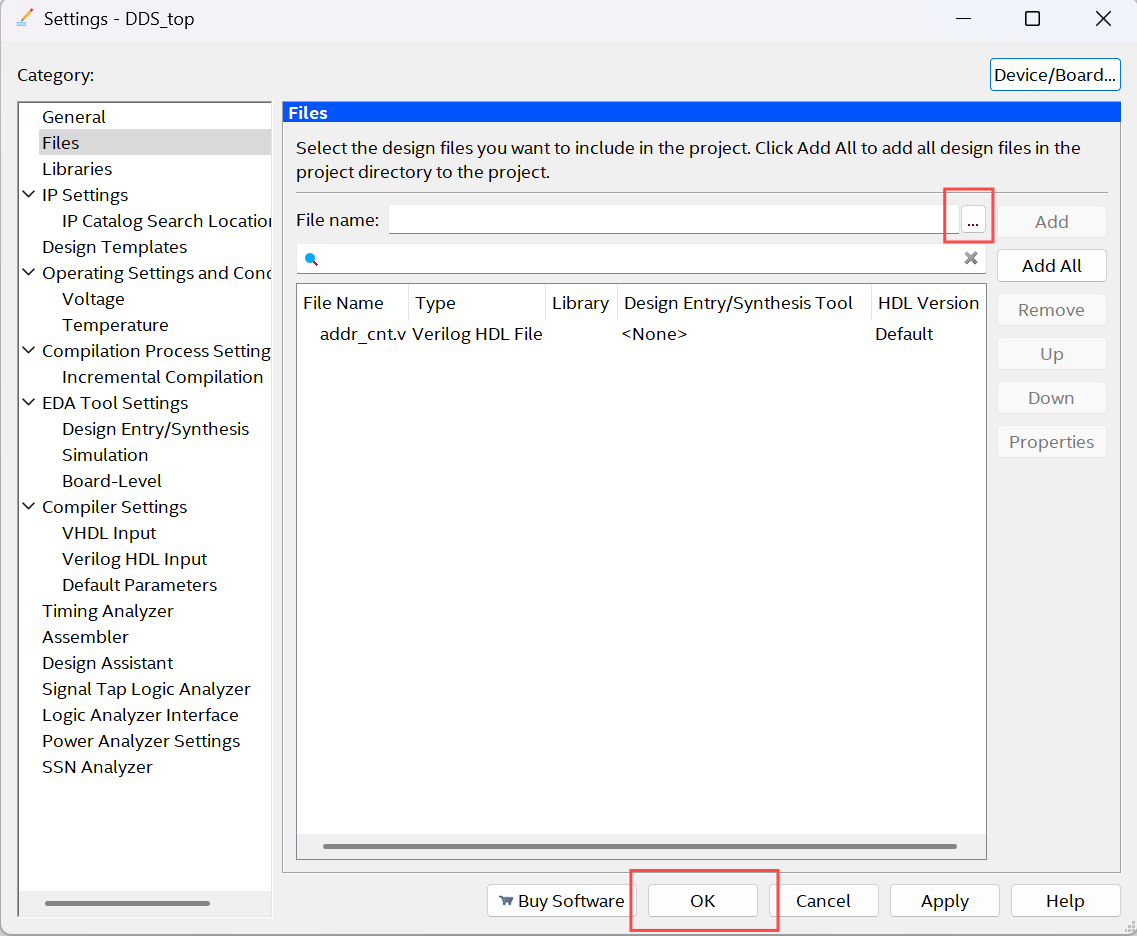

endmodule在项目中添加addr_cnt.v文件,选择Files,右键点击Files,点击添加

找到刚才保存的文件添加

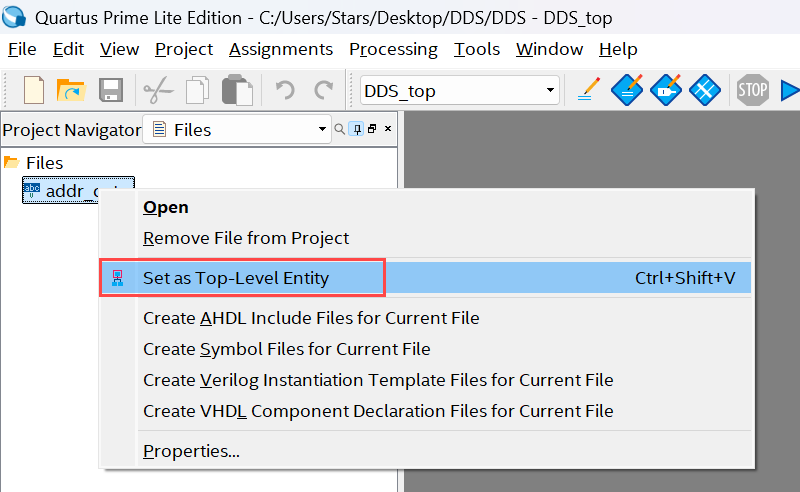

选择Set as Top-Level Entity将其设为顶层文件,点击编译

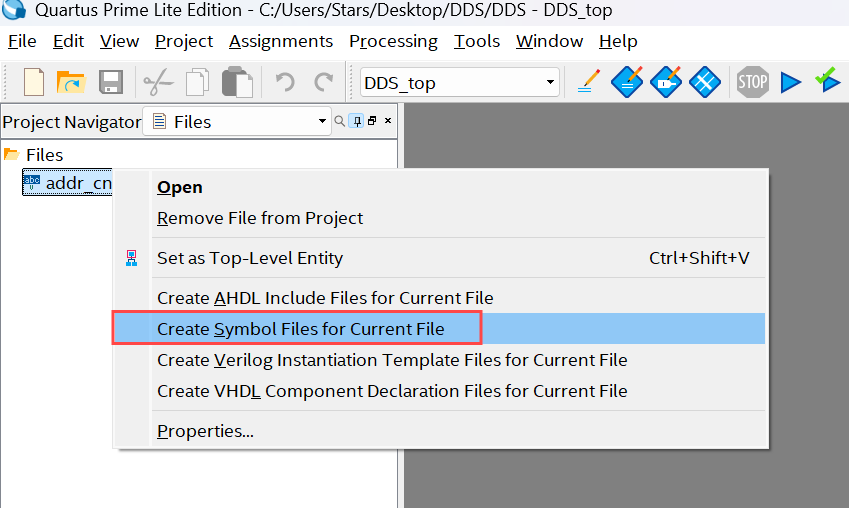

右键点击addr_cnt.v文件,选择CreateSymbol Files for Current File命令,生成该模块的符号

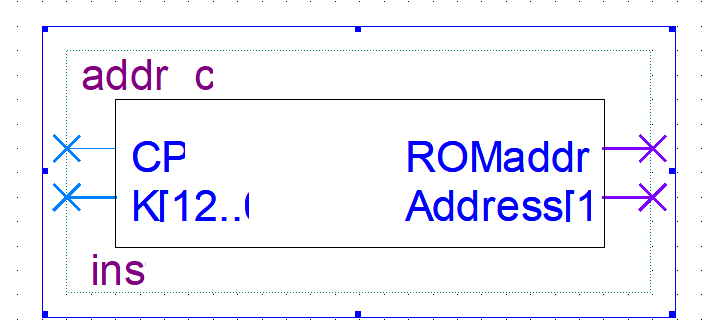

在Quartus中打开生成的addr_cnt.bsf文件,生成的该模块的符号如图

(2)波形存储器ROM的设计

A.方波模块

步骤跟上面的一样,文件名为squwave.v,其代码如下

//=====方波产生模块:squwave.v ======

module squwave(CPi,RSTn,Address,Qsquare);input CPi; //系统基准时钟(100MHz)input RSTn; //同步清零input [16:0] Address; //17位地址输入信号output reg [11:0] Qsquare; //输出方波信号,12位宽,送至DACalways @(posedge CPi) if(!RSTn) Qsquare=12'h000; //同步清零else begin if(Address<=17'h0FFFF) Qsquare=12'hFFF; //输出高电平else Qsquare=12'h000; //输出低电平end

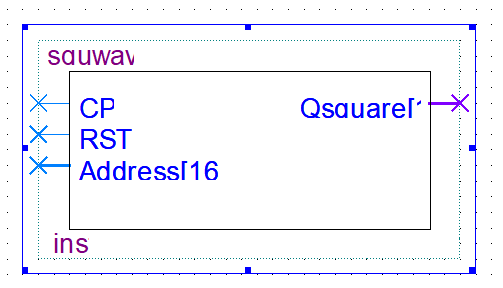

endmodule打开生成的squwave.bsf文件后该模块的符号如图

B.正弦波形存储器模块

Quartus Prime软件接受两种格式的初始化文件MemoryInitialization File(.mif)和Hexadecimal(Intel-Format)File(.hex)。使用时,将初始化文件放在当前工程项目子目录中,在配置LPM_ROM时会对其进行初始化。而建立.mif格式文件有两种方法,一种是直接编辑法,另一种是用C语言等软件生成初始化文件(初始化储存单元较多时更加实用)

打开c语言编译器,建立sinewave.c文件,代码如下

#include <stdio.h>

#include <math.h>

#define PI 3.141592

#define DEPTH 1024 //数据深度,即存储单元的个数

#define WIDTH 12 //存储单元的宽度

int main(void)

{int n,temp;float v;FILE *fp;

/*建立文件名为Sine1024.mif的新文件,允许写入数据,对文件名没有特殊要求,但扩展名必须为.mif*/fp=fopen("Sine1024.mif","w+");if(NULL==fp)printf("Can not creat file!\r\n");else{printf("File created successfully!\n");/*生成文件头,注意不要忘了“;” */fprintf(fp,"DEPTH =%d;\n",DEPTH);fprintf(fp,"WIDTH =%d;\n",WIDTH);fprintf(fp,"ADDRESS_RADIX=HEX;\n");fprintf(fp,"DATA_RADIX=HEX;\n");fprintf(fp,"CONTENT\n");fprintf(fp,"BEGIN\n");/*以十六进制输出地址和数据*/for(n=0;n<DEPTH;n++){/*周期为1024个点的正弦波*/v=sin(2*PI*n/DEPTH);/*将-1~1之间的正弦波的值扩展到0~4095之间*/temp=(int)((v+1)*4095/2); //v+1将数值平移到0~2之间/*以十六进制输出地址和数据*/fprintf(fp,"%x\t:\t%x;\n",n,temp);}fprintf(fp,"END;\n");fclose(fp); //关闭文件}

}运行此文件后会生成sinewave.exe文件,双击运行就会生成Sine1024.mif文件

接着,验证生成的数据是否正确。用记事本打开生成的mif文件,同时用Quartus Prime软件打开mif文件,若能成功导入数据且数据一致,则说明生成文件正确,将其添加到工程文件中。

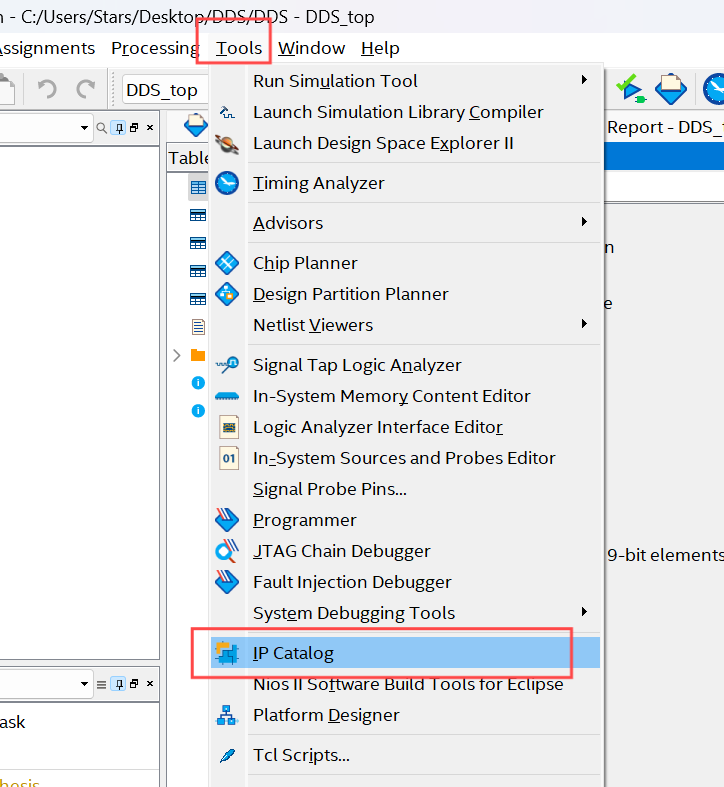

在Quartus Prime主界面选择Tool→IP Catalog

在查找框内输入ROM, IP核目录(IP Catalog)栏中会列出相关的IP核,选择ROM:1-PORT并双击

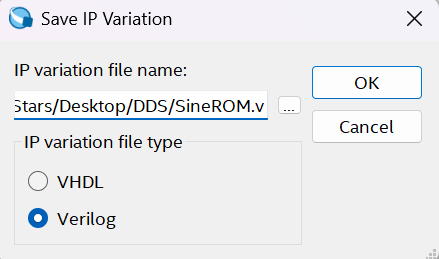

弹出如图所示的保存IP设置界面,输入文件名SineROM.v,并选中Verilog,单击OK按钮

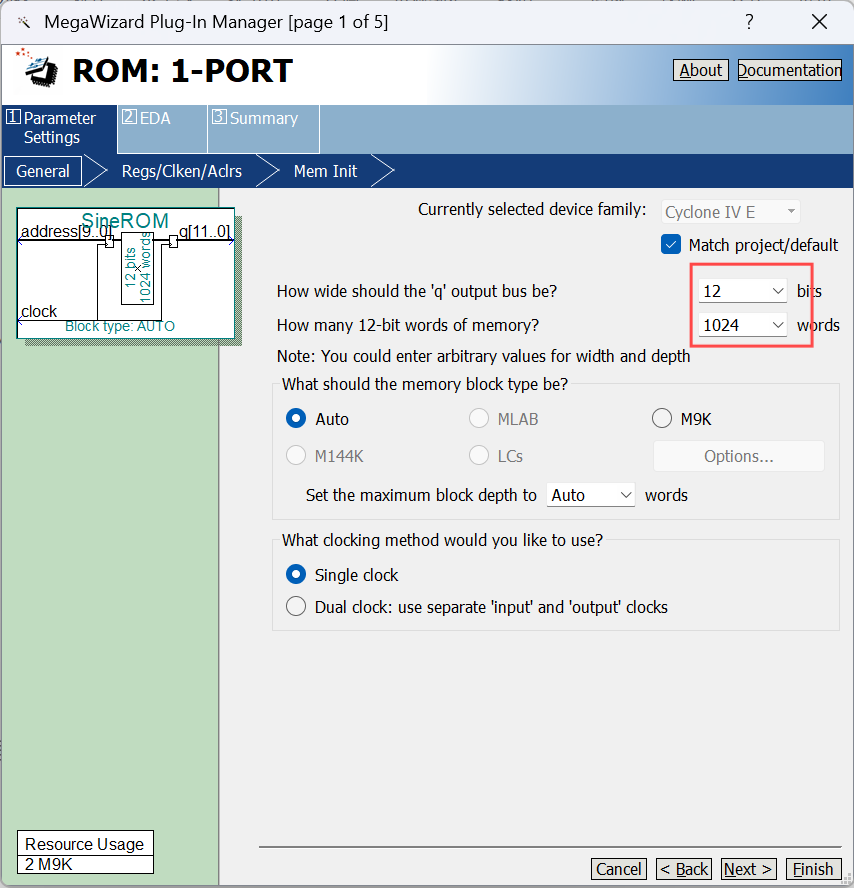

设置ROM的数据位宽为12,存储容量(字数)为1024,单击Next按钮

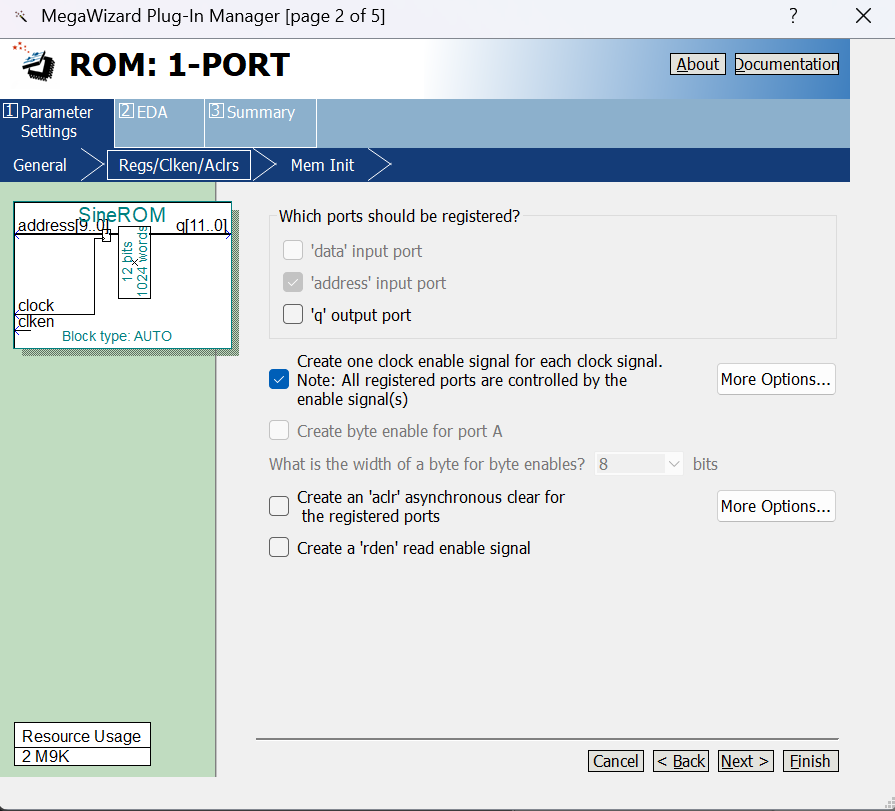

点击Next,配置如下

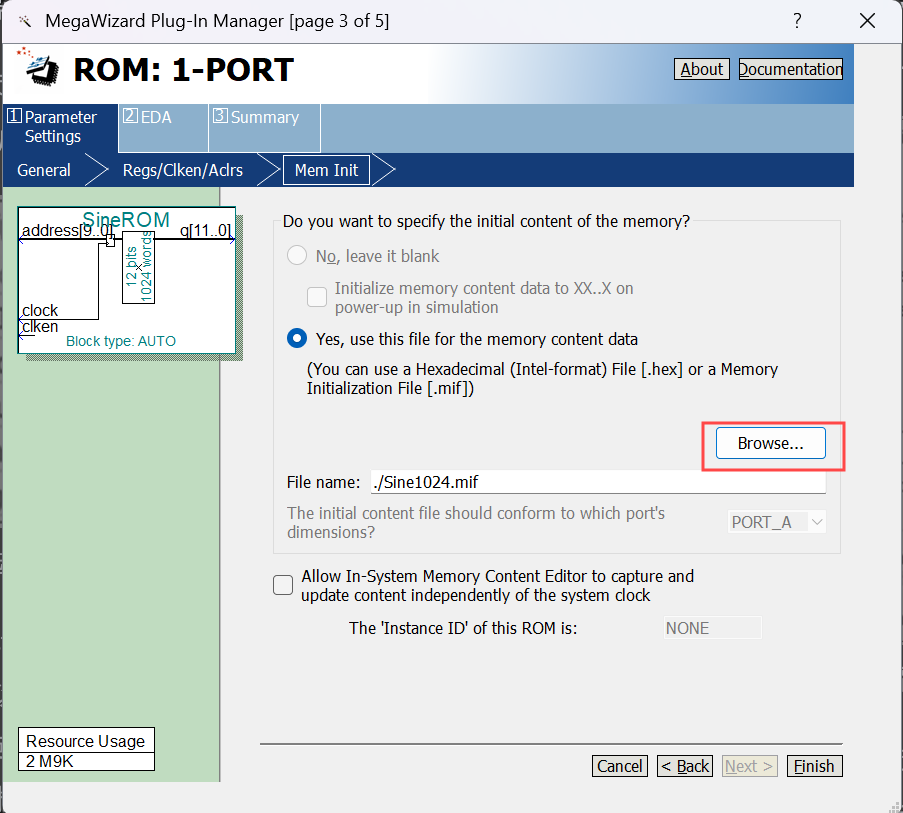

点击Browse...选择生成的Sine1024.mif文件,这是指明初始化ROM所使用的数据文件名

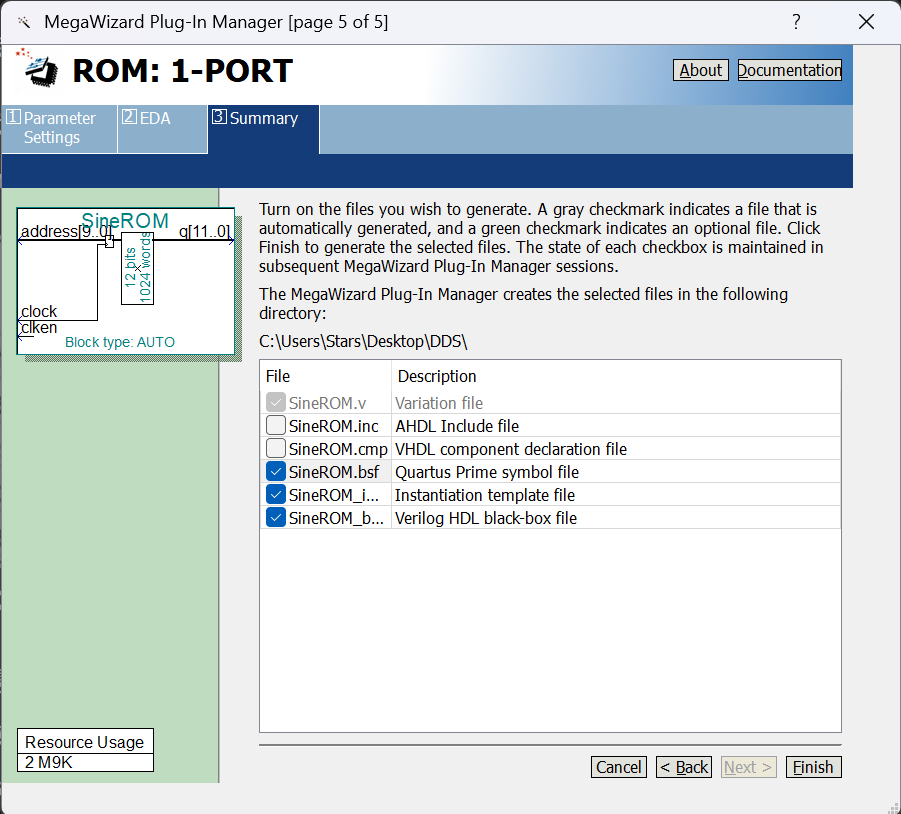

然后Next直到最后一页,弹出如图所示的选择输出文件的对话框(最重要的是.v文件,其余文件按需要勾选,.bsf文件也可以选上),选择好后点击Finish

SineROM.v等相关文件就生成好了

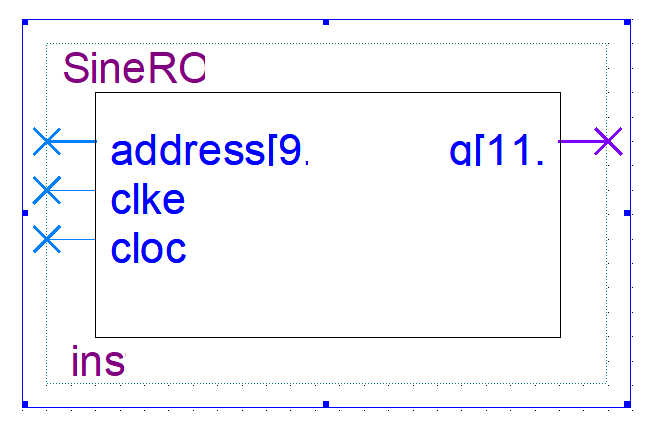

该模块的符号如下图所示:

3.锁相环倍频电路设计

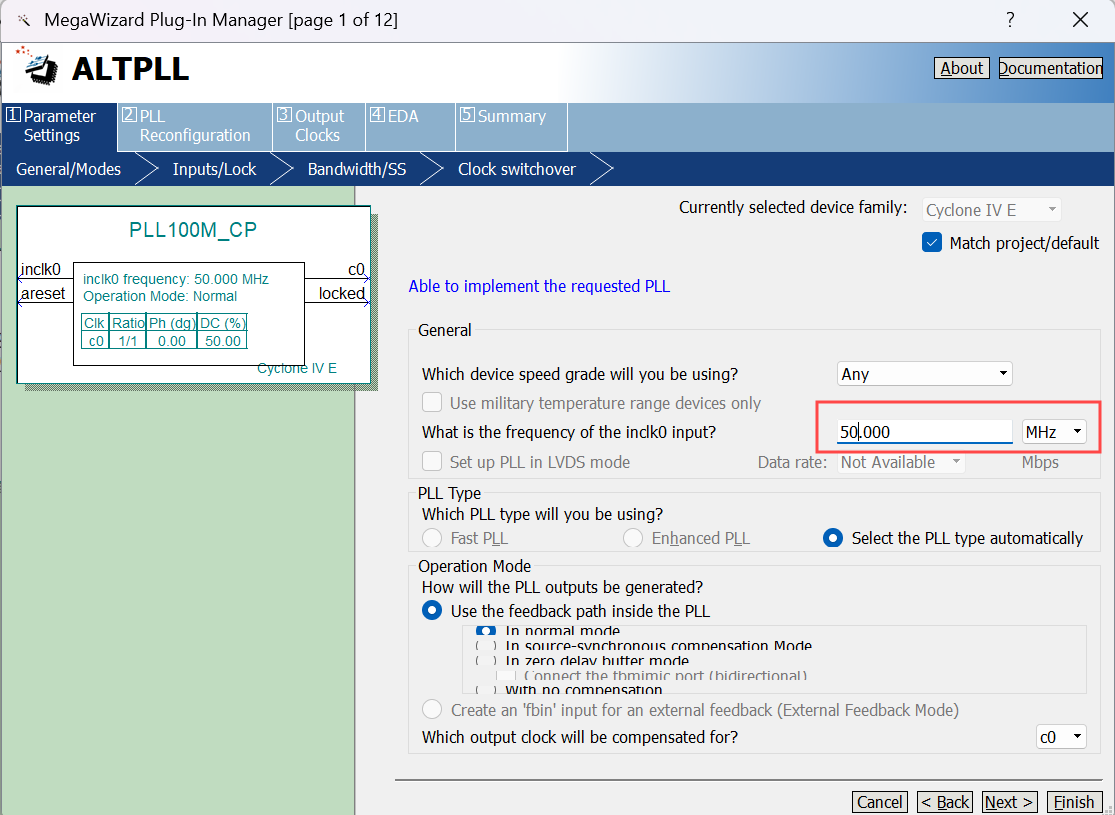

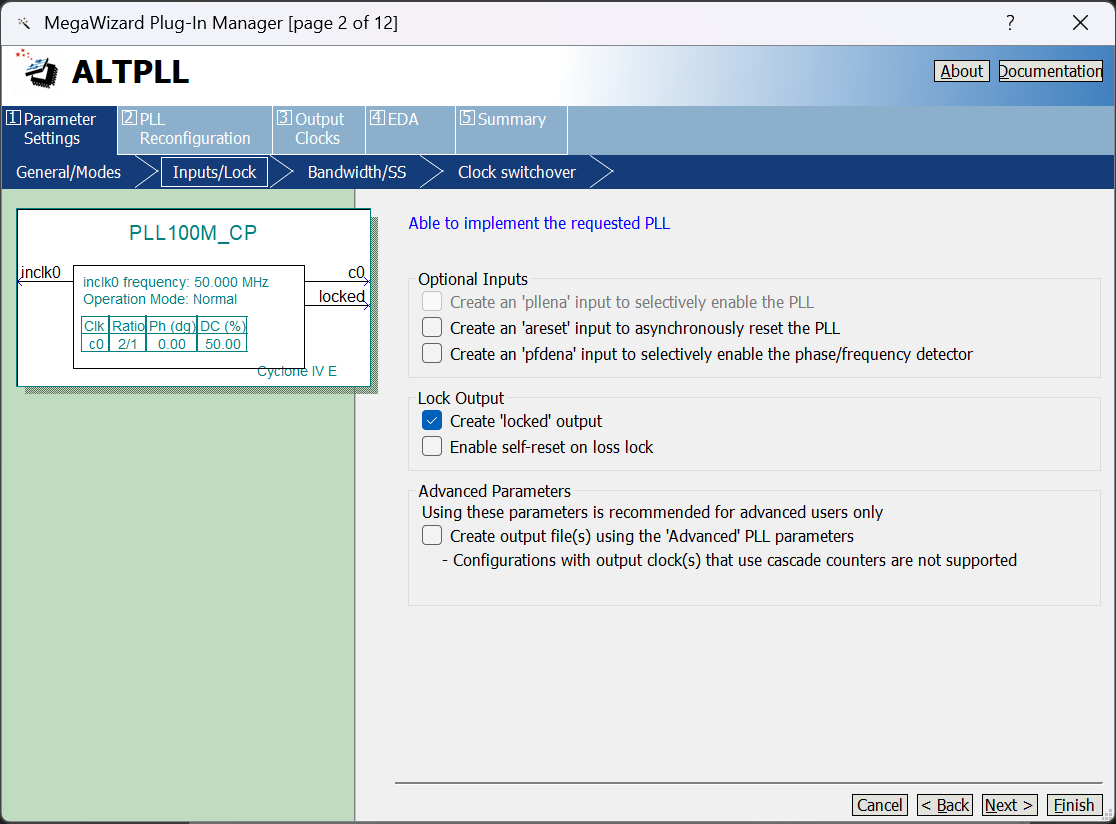

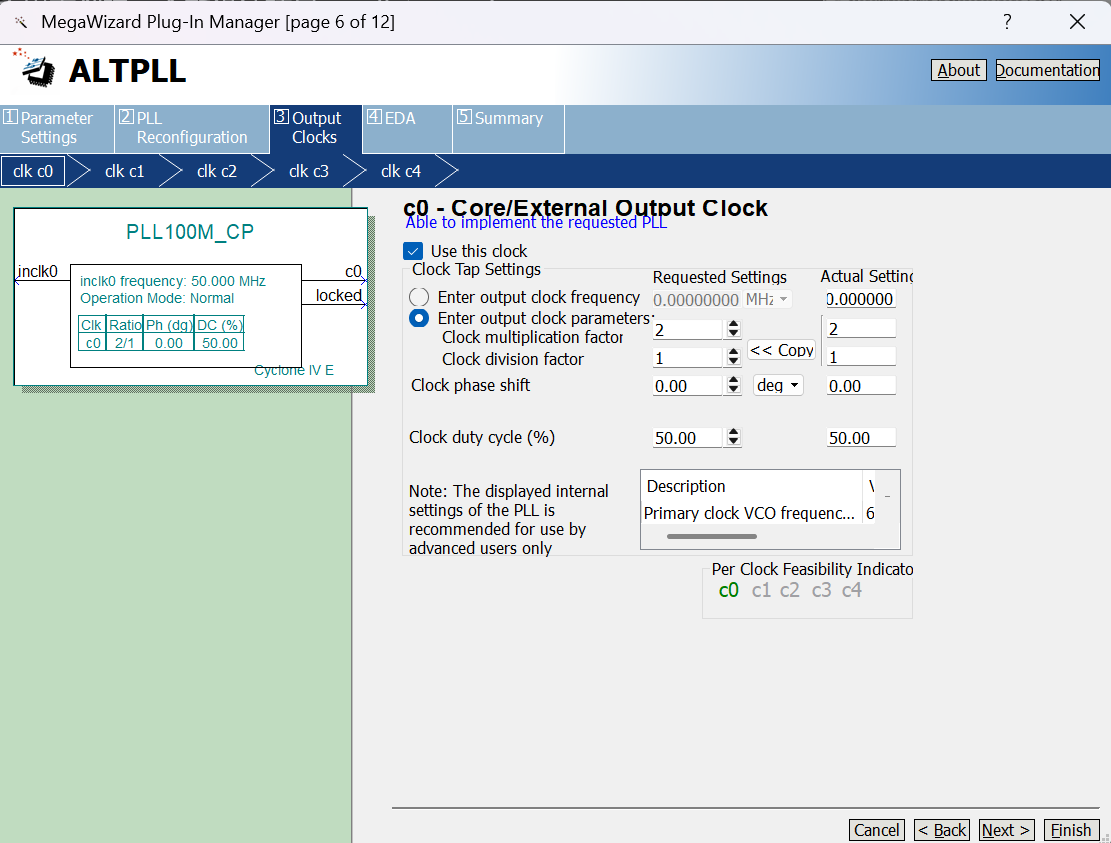

定制一个名称为PLL100M_CP的时钟模块,该模块的输入inclk0为50MHz时钟信号,输出c0为100MHz的脉冲信号,占空比为50%,带有相位锁定指示输出端locked。

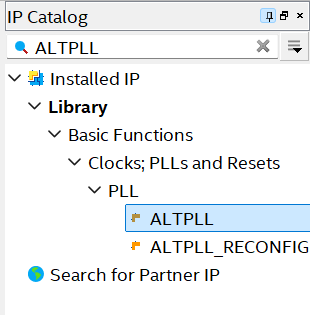

在右侧查找框内输入ALTPLL(嵌入式锁相环)

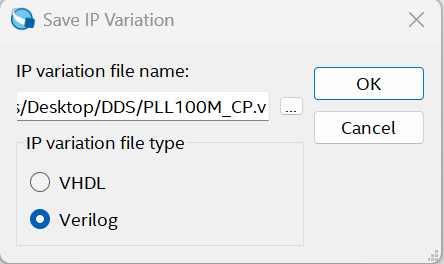

双击打开,输入文件名PLL100M_CP.v,并选中Verilog,单击OK按钮

设置输入时钟(inclk0)频率为50MHz

其余的按如下图片设置

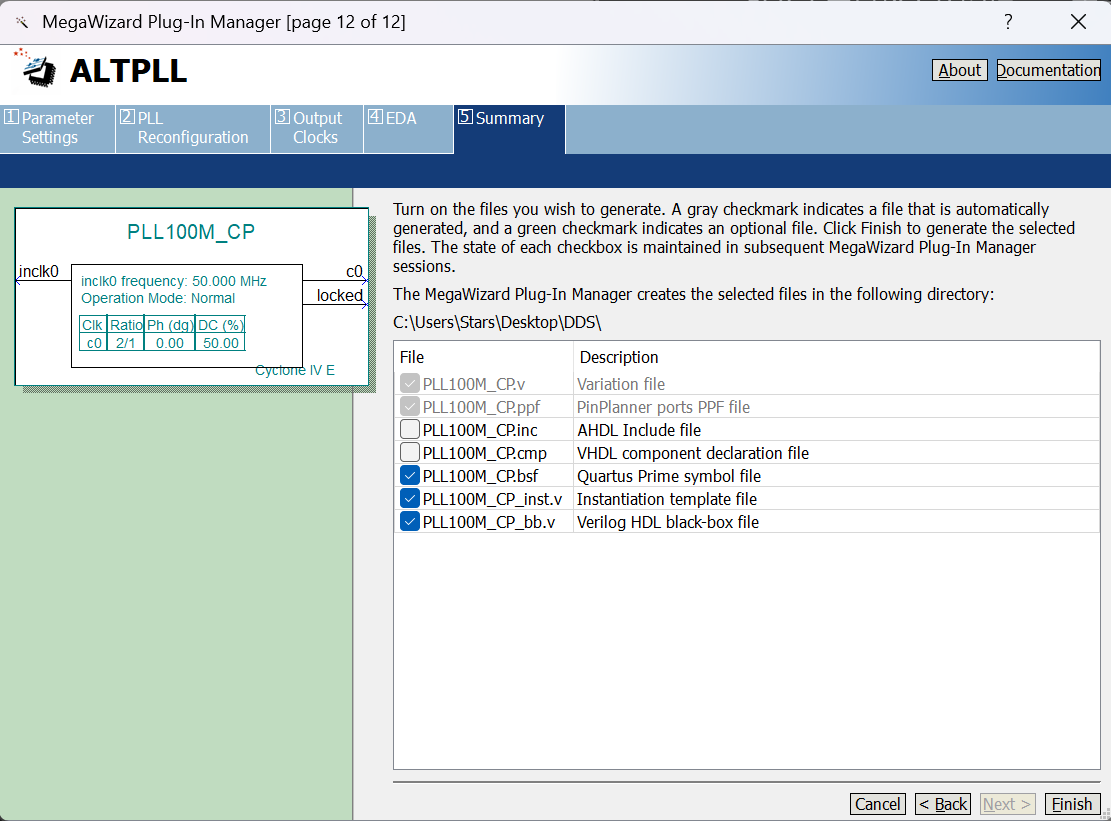

最后选择需要生成的文件

4.顶层电路设计

代码如下

//========DDS的顶层模块:DDS_top.v ======

module DDS_top(CLOCK_50, RSTn, WaveSel, K,

WaveValue, LEDG, CLOCK_100);input CLOCK_50; //50MHz时钟input RSTn; //控制方波清零,低电平有效input [1:0] WaveSel; //波形选择:SW[17:16]=10时为方波;SW//[17:16]=01时为正弦波input [12:0] K; //频率控制字SW12..SW0output reg [11:0] WaveValue; //输出波形数据wire [9:0] ROMaddr; //波形存储器地址wire [16:0] Address; //17位相位累加器地址wire [11:0] Qsine, Qsquare; //正弦、方波数据输出output [0:0]LEDG; //锁相环相位锁定指示灯,亮表示锁定output CLOCK_100; //锁相环输出时钟,频率为100MHzwire CPi =CLOCK_100;PLL100M_CP PLL100M_CP_inst ( //实例引用锁相环子模块.inclk0 ( CLOCK_50 ), //50MHz时钟输入.c0 ( CLOCK_100 ), //100MHz时钟输出.locked ( LEDG[0] ) //相位锁定指示

);addr_cnt U0_instance(CPi,K,ROMaddr,Address);//实例引用地址累加器SineROM ROM_inst ( //实例引用正弦LPM_ROM子模块.address (ROMaddr),.clock ( CPi ),.q ( Qsine )

);squwave U1(CPi,RSTn, Address,Qsquare); //实例引用方波子模块always @(posedge CPi)

begincase(WaveSel) //选择输出波形2'b01:WaveValue=Qsine; //输出正弦波2'b10:WaveValue=Qsquare; //输出方波default:WaveValue=Qsine;endcase

end

endmodule写好后添加到工程中,将此文件设为顶层模块并进行编译。

三、设计实现

使用DE2-115开发板来验证上述设计。用板上的50MHz晶振作为时钟输入,用KEY3控制方波清零,用SW12~SW0设置频率控制字,SW17、SW16用来选择输出波形的种类,用LEDG0作为PLL的相位锁定指示。

有DE2_115_pin_assignments.csv文件可以直接导入不用手动配置引脚,没有的话参考DE2-115文档配置。为了方便导入文件DE2_115_pin_assignments.csv进行引脚分配,将使用该文件中的端口名称代替上述DDS_top.v(代码如下)中的信号名称。为此再编写一个顶层文件DE2_DDS_top.v代码如下:

//=====在开发板上运行的DDS的顶层模块:DE2_115_DDS_top.v ======

module DE2_115_DDS_top(CLOCK_50, KEY, SW, GPIO_0, LEDG);input CLOCK_50; //50MHz时钟input[3:3] KEY; //按键KEY3,控制方波清零input[17:0] SW; //拨动开关output [12:0] GPIO_0; //扩展接口,送出波形数据给DACoutput [0:0]LEDG; //绿色LED指示相位是否锁定wire CLOCK_100; //100MHz时钟assign GPIO_0[12]=CLOCK_100; //送给DAC的时钟wire RSTn = KEY[3]; //控制方波清零,低电平有效wire [1:0] WaveSel = SW[17:16]; //选择输出波形wire [12:0] K = SW[12:0]; //设置频率控制字,最小值必须为1wire [11:0] WaveValue;assign GPIO_0[11:0] = WaveValue; //输出波形数据DDS_top DE2(CLOCK_50, RSTn, WaveSel, K, WaveValue, LEDG, CLOCK_100);

endmodule对其进行全编译

相关文章:

)

FPGA系列之DDS信号发生器设计(DE2-115开发板)

一、IP核 IP(Intellectual Property)原指知识产权、著作权等,在IC设计领域通常被理解为实现某种功能的设计。IP模块则是完成某种比较复杂算法或功能(如FIR滤波器、FFT、SDRAM控制器、PCIe接口、CPU核等)并且参数可修改的电路模块,…...

修改Theme SHELL美化panel

安装 使用 使用Tweaks进行设置 需要创建.themes文件夹,在当前目录下 mkdir ~/.themes从官网下载文件 https://www.gnome-look.org/p/1013030 将打包压缩文件移动到~/themes,并解压 tar -xvf 01-Flat-Remix-Light-20250413.tar.xz然后使用 按 Alt F2…...

Sentinel源码—5.FlowSlot借鉴Guava的限流算法二

大纲 1.Guava提供的RateLimiter限流使用示例 2.Guava提供的RateLimiter简介与设计 3.继承RateLimiter的SmoothBursty源码 4.继承RateLimiter的SmoothWarmingUp源码 3.继承RateLimiter的SmoothBursty源码 (1)SmoothBursty的初始化流程 (2)SmoothBursty的初始化完成后的变量…...

)

自由学习记录(56)

从贴图空间(texture space)将值还原到切线空间(tangent space)向量 tangentNormal.xy (packedNormal.xy * 2 - 1) * _BumpScale; 背后的知识点:法线贴图中的 RGB 是在 0~1 范围内编码的向量 所以贴图法线是怎么“压…...

计算机网络八股——HTTP协议与HTTPS协议

前言: 到时候我想要写一篇文章就是:在浏览器中输入URL并按下回车会发生什么? 然后将几篇文章全部串联到一起,现在几天的任务就是将这里的每个小部分进行一个详细的介绍 HTTP1.1简述与特性 Web 上的通信都是建⽴在 HTTP 协议上的…...

)

JAVAEE(网络原理—UDP报头结构)

我们本篇文章要讲的是UDP的报头结构以及注意事项。 下面呢,我先说一下UDP是什么? 1.UDP是什么? UDP是一种网络协议。网络协议是计算机网络中,为了使不同设备之间能够准确、高效地进行数据交换和通信,而预先制定的一…...

Redis-分布式锁

Redis-分布式锁 文章目录 Redis-分布式锁1.基本原理和不同方式实现方式对比2.Redis分布式锁的基本实现思路3.分布式锁误删问题一4.分布式锁误删问题二5.Redission1.功能介绍2.快速入门3.可重入锁原理4.锁重试和WatchDog机制1.锁重试2. WatchDog 机制(锁自动续期&…...

如何优雅地为 Axios 配置失败重试与最大尝试次数

在 Vue 3 中,除了使用自定义的 useRequest 钩子函数外,还可以通过 axios 的拦截器 或 axios-retry 插件实现接口请求失败后的重试逻辑。以下是两种具体方案的实现方式: 方案一:使用 axios 拦截器实现重试 实现步骤: 通…...

Windows使用SonarQube时启动脚本自动关闭

一、解决的问题 Windows使用SonarQube时启动脚本自动关闭,并发生报错: ERROR: Elasticsearch did not exit normally - check the logs at E:\Inori_Code\Year3\SE\sonarqube-25.2.0.102705\sonarqube-25.2.0.102705\logs\sonarqube.log ERROR: Elastic…...

)

MYSQL初阶(暂为自用草稿)

目录 基本操作 database操作 table操作 数据类型 INT类型 bit类型 FLOAT类型 CHAR类型 DATE类型 SEL类型 表的约束 列约束 NULL DEFAULT PRIMARY KEY UNIQUE KEY 表约束 PRIMARY KEY FOREIGN KEY 其他补充 AUTO_INCREMENT COMMENT ZEROFILL 表的CRUD …...

交换排序——快速排序

交换排序的基本思路:把序列中的两个元素进行比较,根据需求对两个元素进行交换。特点是较大的元素向序列的尾部移动,较小的元素向序列的前部移动。 hoare法 在序列中任取一个元素作为基准值,一趟排序完成之后,以基准值为…...

资源-又在网上淘到金了

前言: 本期再分享网上冲浪发现的特效/动画/视频资源网站。 一、基本介绍: mantissa.xyz,about作者介绍为:Midge “Mantissa” Sinnaeve (米奇辛纳夫)是一位屡获殊荣的艺术家和导演,提供动画、…...

CSS中的`transform-style`属性:3D变换的秘密武器

在CSS中,当我们尝试创建复杂的3D场景时,transform-style属性变得尤为重要。它决定了子元素是在3D空间中呈现还是被展平到2D平面中。本文将深入探讨transform-style的用法,并通过具体的代码示例来展示如何利用这个属性来增强你的网页设计。 什…...

Step文件无法编辑怎么办?

Step文件无法编辑怎么办? 这里介绍两种方法, 1、 直接导入 准备step文件,solidworks导入后是这样,不能在上面直接编辑 图 1 点击右键,选择解除特征(不同版本的可能不太一样,这里是solidworks2…...

从 LabelImg 到 Label Studio!AI 数据标注神器升级,Web 版真香

视频讲解: 从 LabelImg 到 Label Studio!AI 数据标注神器升级,Web 版真香 Label Studio 支持图像、文本、音频、视频、时间序列等多类型数据标注,覆盖计算机视觉(目标检测、语义分割)、自然语言处理&#x…...

纯FPGA实现驱动AD9361配置的思路和实现之一 概述

我们在做ZYNQ系统开发时候做的IP基本都是AXI_LITE_SLAVE,是SLAVE,从设备。就是提供了若干寄存器接口供MASTER进行读写。SLAVE里面的逻辑通过读写动作或者读写的数据进行响应的动作。这种方式的好处是硬件层面可以访问寄存器,软件层面是可以实…...

Nacos配置中心服务端源码解析

文章目录 概述一、配置持久化到数据库二、发布事件2.1、事件发布者端2.1.1、DefaultPublisher#publish2.1.2、DefaultPublisher#run2.1.3、DefaultPublisher#receiveEvent 2.2、事件订阅者端2.2.1、Subscriber#onEvent2.2.2、ConfigCacheService#dump 总结:Nacos 配…...

SAP系统工艺路线的分配物料出现旧版包材

问题:工艺路线的物料错了 这是3月份技术部发现的问题,10000209这个成品有两个版本的BOM, 在创建新版的工艺路线里,发现分配的物料仍然是旧版的物料. 原因排查: 1 BOM中物料错误? 2 选错了生产版本,选了版本1? 3 生产版本设置中的可选BOM错误? 解决:把可选的BOM…...

JVM虚拟机--JVM的组成

(一)JVM的组成 一、JVM介绍 (1)JVM的作用 我们知道,Java代码要想在计算机中正常运行,就需要经过编译为class二进制字节码文件,而JVM就提供了class二进制字节码的运行环境。 一次编写,到处运行 因为JVM是…...

科学研究:怎么做

科研(科学研究) 是指通过系统化的方法,探索自然、社会或人文领域的未知问题,以发现新知识、验证理论或解决实际问题的活动。它的核心是基于证据的探索与创新,旨在推动人类认知和技术的进步。 科研的核心要…...

PyTorch数据操作基础教程:从张量创建到高级运算

本文通过示例代码全面讲解PyTorch中张量的基本操作,包含创建、运算、广播机制、索引切片等核心功能,并提供完整的代码和输出结果。 1. 张量创建与基本属性 import torch# 创建连续数值张量 x torch.arange(12, dtypetorch.float32) print("原始张…...

微服务治理与可观测性

服务注册与发现 核心功能 服务实例动态变化:实例可能因扩缩容、故障或迁移导致IP变动。服务依赖解耦:调用方无需硬编码服务地址,降低耦合度。负载均衡:自动选择健康实例,提升系统可用性。 核心组件 服务注册中心&am…...

如何对docker镜像存在的gosu安全漏洞进行修复——筑梦之路

这里以mysql的官方镜像为例进行说明,主要流程为: 1. 分析镜像存在的安全漏洞具体是什么 2. 根据分析结果有针对性地进行修复处理 3. 基于当前镜像进行修复安全漏洞并复核验证 # 镜像地址mysql:8.0.42 安全漏洞现状分析 dockerhub网站上获取该镜像的…...

OpenCV 04.19 练习

1. 创建一个 PyQt 应用程序,该应用程序能够: 1.使用 OpenCV 加载一张图像。 2.在 PyQt 的窗口中显示这张图像。 3.提供四个按钮(QPushButton): - 一个用于将图像转换为灰度图 - 一个用于将图像恢复为原始彩色图 - 一个…...

uv:重新定义Python开发效率的下一代工具链

在Python生态系统中,包管理和项目工具链的复杂性一直是开发者面临的一大挑战。从依赖管理、虚拟环境创建到多版本Python切换,传统的工具链(如pip、virtualenv、poetry等)虽然功能强大,但操作繁琐、性能不足的问题长期存在。而uv的出现,以颠覆性的速度和功能集成,为Pytho…...

【Easylive】Gateway模块 bootstrap.yml 解析

【Easylive】项目常见问题解答(自用&持续更新中…) 汇总版 Gateway模块 bootstrap.yml 常规解析 该配置文件定义了 Spring Cloud Gateway 的核心配置,包括 环境配置、服务注册、动态路由规则 等。以下是逐项解析: 1. 基础配…...

Warcraft Logs [Classic] [WCL] Usage Wizard <HTOC>

HTOC(十字军的试炼)副本中各个BOSS的ID如下: 629 - 诺森德野兽 633 - 加拉克苏斯大王 637 - 派系冠军 641 - 瓦格里双子 645 - 阿努巴拉克 encounterID!637 and encounterID!641 encounterID NOT IN (637,641) 伤害 …...

)

多模态大语言模型arxiv论文略读(二十八)

MM-SAP: A Comprehensive Benchmark for Assessing Self-Awareness of Multimodal Large Language Models in Perception ➡️ 论文标题:MM-SAP: A Comprehensive Benchmark for Assessing Self-Awareness of Multimodal Large Language Models in Perception ➡️…...

JavaScript数据类型简介

在JavaScript中,理解不同的数据类型是掌握这门语言的基础。数据类型决定了变量可以存储什么样的值以及这些值能够执行的操作。JavaScript支持多种数据类型,每种都有其特定的用途和特点。本文将详细介绍JavaScript中的主要数据类型,并提供一些…...

CasualLanguage Model和Seq2Seq模型的区别

**问题1:**Causal Language Modeling 和 Conditional Generation 、Sequence Classification 的区别是什么? 因果语言模型(Causal Language Model): 预测给定文本序列中的下一个字符,一般用于文本生成、补全句子等,模型…...

在Qt和OSG中动态改变部分3D模型数据

要在Qt和OSG环境中导入3D模型并只对部分数据进行动态改变,你可以采用以下方法: 基本实现步骤 加载模型:使用OSG的读取器加载3D模型文件 访问特定部分:识别并获取模型中需要修改的部分 动态修改:在Qt界面或逻辑中设置修改这些部分的机制 更新显示:确保修改后的模型能够实…...

命令update-alternatives

❯ which pip /home/ying/anaconda3/bin/pipying192 ~ [2]> which pip /usr/bin/pip使用update-alternatives对他们进行管理和切换 快捷方式 和 实际路径不可以相同 所以我这边选择了/usr/local/bin目录作为介质存储快捷方式,另外该快捷方式会自己创建我们只需选…...

10.thinkphp的响应

响应输出 响应操作 1. 响应输出,有好几种:包括return、json()和view()等等; 2. 默认输出方式是以html格式输出,如果你发起json请求,则输出json; 3. 而背后是response对象,可以用response()输…...

【技术派后端篇】技术派中的白名单机制:基于Redis的Set实现

在技术派社区中,为了保证文章的质量和社区的良性发展,所有发布的文章都需要经过审核。然而,并非所有作者的文章都需要审核,我们通过白名单机制来优化这一流程。本文将详细介绍技术派中白名单的实现方式,以及如何利用Re…...

Keil A51汇编伪指令

以下是 Keil A51 汇编器支持的常用伪指令 及其详细说明,涵盖代码结构、数据定义、条件编译等关键功能,结合实际应用场景进行分类和示例: 一、程序结构与地址控制 伪指令功能语法示例说明ORG设置代码/数据起始地址ORG 0000H后续代码从指定地址…...

Windows上安装FFmpeg的详细指南

1.下载FFmpeg 访问FFmpeg官方下载页面:https://ffmpeg.org/download.html 点击"Windows builds from gyan.dev"或"Windows builds by BtbN" gyan.dev版本:https://www.gyan.dev/ffmpeg/builds/ BtbN版本:https://githu…...

jmeter利用csv进行参数化和自动断言

1.测试数据 csv测试数据如下(以注册接口为例) 2.jemer参数化csv设置 打开 jmeter,添加好线程组、HTTP信息头管理器、CSV 数据文件设置、注册请求、响应断言、查看结果树 1) CSV 数据文件设置 若 CSV 中数据包含中文,…...

《Android 应用开发基础教程》——第二章:Activity 与生命周期详解

目录 第二章:Activity 与生命周期详解 2.1 什么是 Activity? 作用: 2.2 创建一个 Activity 示例代码 Manifest 注册: 2.3 Activity 生命周期(Life Cycle) 生命周期图解: 2.4 生命周期代…...

[Java]反射、String类补充

目录 1、反射定义 2、用途(了解) 3、反射相关的类 4、Class类(反射机制的起源) 4.1、相关方法 5、反射示例 5.1、获取Class对象 5.2、反射的使用 6、反射优点和缺点 7、String类补充 7.1、创建对象的思考 8、字符串常量池 9、再谈String对象创建 10、intern方法 …...

word表格批量操作——宏

word中所有表格代码 这个是表格的模板代码 Sub 表格通用代码() For i ActiveDocument.Tables.Count To 1 Step -1ActiveDocument.Tables (i) Next End Sub1、根据内容自动调整表格 Sub 表格适用内容() For i ActiveDocument.Tables.Count To 1 Step -1ActiveDocument.Tabl…...

eSTK.me

eSTK.me 调用 USIM 卡的 Applet 实现在 iOS 内自助切换 Profile。写卡仍然需要借助硬件读卡器或者兼容 eSIM 的 Android 手机。支持国行 iPhone。 eSTK.me(固件 v2.x 及以后的版本)基于 ETSI 的 Bearer Independent Protocol (BIP) 协议,使…...

四级英语备考指南

一、引言 大学英语四级考试是对大学生英语综合能力的一次重要检验。无论是为了学业要求,还是提升自身竞争力,顺利通过四级考试都有着重要意义。本文将为大家详细介绍四级英语的备考策略,帮助大家高效备考,取得理想成绩。 二、了…...

Java Web 之 互联网协议 100问

HTTP是什么? HTTP(HyperText Transfer Protocol,超文本传输协议)是互联网上应用最广泛的协议之一,用于在客户端(如浏览器)和服务器之间传输数据。它是 Web 通信的基础,支持浏览器访…...

【单倍型理解及计算系列之二】单倍型基本概念以及其与遗传定位中Bin的定义区别

问题:如何理解单倍型,与遗传定位中Bin的定义区别: 简而言之:就是单倍型是基于LD,通常为连锁不平衡(LD)较高的区域形成。但bin是人为划分的,如以固定SNP数量/固定长度设置࿰…...

ArcPy Mapping 模块基础

在地理信息系统(GIS)的应用中,地图制作是一个非常重要的环节。无论是生成用于展示的静态地图,还是动态更新的地图服务,都需要高效且灵活的工具来实现。ArcPy 提供了强大的mapping模块,可以帮助用户自动化地…...

AcWing 11:背包问题求方案数 ← 0-1背包

【题目来源】 https://www.acwing.com/problem/content/11/ 【题目描述】 有 N 件物品和一个容量是 V 的背包。每件物品只能使用一次。 第 i 件物品的体积是 vi,价值是 wi。 求解将哪些物品装入背包,可使这些物品的总体积不超过背包容量,且总…...

Redis增删改查

### 进入redis控制台 redis-cli --raw #加上raw,防止中文乱码### 增 127.0.0.1:6379> LPUSH list0 "hello" #增加一个list 1 127.0.0.1:6379> LRANGE list0 0 -1 #查看list hello### 删 127.0.0.1:6379> DEL list0 #删除list 1 127.0.0.1:6379> LRANG…...

多道程序和多任务操作系统区别

多道程序 vs. 多道任务:对比分析 ✅ 共同点 方面共同特征核心机制都依赖于进程/任务切换执行需求实现多个程序或任务"并发"执行系统支持都需要操作系统的支持(如调度算法、内存管理)本质目标提高资源利用率(CPU不空转…...

【MySQL】MySQL建立索引不知道注意什么?

基本原则: 1.选择性原则: 选择高选择性的列建立索引(该列有大量不同的值) 2.适度原则:不是越多越好,每个索引都会增加写入开销 列选择注意事项: 1.常用查询条件列:WHERE字句中频繁使用的列 2.连接操作列…...

区块链木材业务服务平台:商贸物流新变革

区块链木材业务服务平台:商贸物流新变革 在全球商贸物流行业不断发展的当下,木材贸易作为其中重要的一环,面临着诸多挑战。区块链木材业务服务平台的出现,为木材商贸物流领域带来了全新的解决方案,正逐步引领行业走向…...